一、ADC的工作原理

模数转换器即 A/D 转换器,或简称 ADC,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是把经过与标准量比较处理后的模拟量转换成以二进制数值表示的离散信号的转换器。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小。

二、ADC的分类

模数转换器的种类很多,按工作原理的不同,可分成间接 ADC 和直接 ADC。间接 ADC 是先将输入模拟电压转换成时间或频率,然后再把这些中间量转换成数字量,常用的有双积分型 ADC。直接 ADC 则直接转换成数字量,常用的有并联比较型 ADC 和逐次逼近型 ADC。

并联比较型 ADC: 采用各量级同时并行比较,各位输出码也是同时并行产生,所以转换速度快。并联比较型 ADC 的缺点是成本高、功耗大。

逐次逼近型 ADC: 它产生一系列比较电压 VR,但它是逐个产生比较电压,逐次与输入电压分别比较,以逐渐逼近的方式进行模数转换的。它比并联比较型 ADC 的转换速度慢,比双分积型 ADC 要快得多,属于中速 ADC 器件。

双积分型 ADC: 它先对输入采样电压和基准电压进行两次积分,获得与采样电压平均值成正比的时间间隔,同时用计数器对标准时钟脉冲计数。它的优点是抗干扰能力强,稳定性好;主要缺点是转换速度低

Σ-Δ 型 ADC: Σ-Δ 型 ADC 由积分器、比较器、1 位 D/A 转换器和数字滤波器等组成。原理上近似于积分型,将输入电压转换成时间(脉冲宽度)信号,用数字滤波器处理后得到数字值。电路的数字部分基本上容易单片化,因此容易做到高分辨率。主要用于音频和测量。这种转换器的转换精度极高,达到 16 到 24 位的转换精度,价格低廉,弱点是转换速度比较慢,比较适合用于对检测精度要求很高但对速度要求不是太高的检验设备

三、ADC 的选型(技术指标)

采样精度 —— 即分辨率,一般有 8 位、10 位、12 位、16 位等;

转换时间 —— 即每次采样所需的时间,表征 ADC 的转换速度,与 ADC 的时钟频率、采样周期、转换周期有关;

数据输出方式 —— 如并口输出、串口输出;

ADC 类型 —— 如上面所提到的,ADC 有多种类型,不同类型的 ADC 有不同的性能极限;

工作电压 —— 需要注意 ADC 的工作电压范围、能否直接测量负电压等;

芯片封装 —— 芯片封装是否符合产品设计要求;

性价比 —— 控制成本。

四、LPC824 ADC 特征及电气特性

4.1 ADC 特征

A. 12 位逐次比较型模数转换器

B. 转换速率高达 1.2Msample/s

D. 自动采样结果“过零”比较检测

E. 具有 power-down 模式和 low-power 操作模式

F. 支持单/多通道突发(burst)转换模式

G. 支持 DMA 功能

H. 支持硬件校准模式

I. 电压的测量范围为 VREFN ~ VREFP

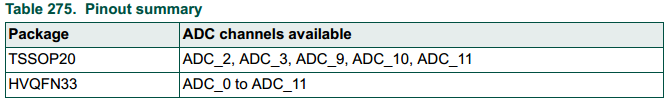

K. 不同封装的的 ADC 通道数不一样

4.2 ADC 电气特性-1

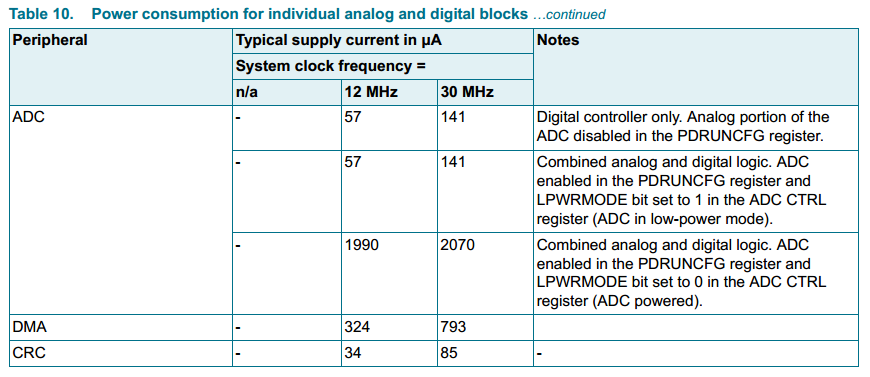

ADC 在正常工作状态下,主频是 12MHz 和 30MHz 的时候,典型的电流分别是 1990uA 和 2070uA。

4.3 ADC 电气特性-2

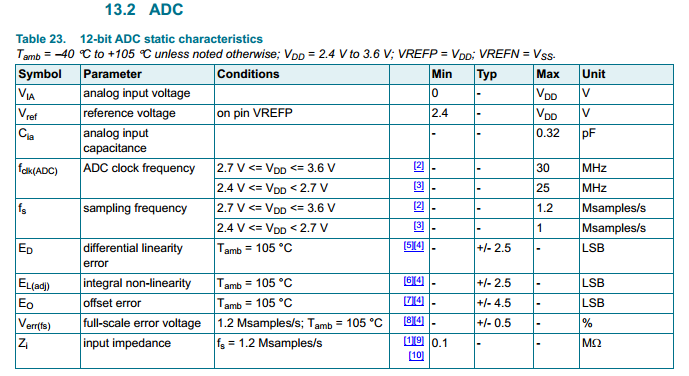

有关 ADC 的输入电压、参考电压、时钟频率、采样时钟等静态特性请参考下表。

如下表 是 ADC 静态特性:

五、ADC 功能模块及配置

5.1 ADC 引脚配置-1

ADC 参考电源引脚

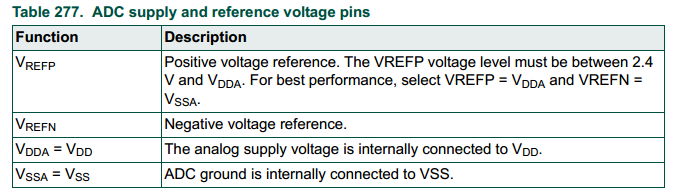

A. 参考电源的供电要求(VREFP - VREFN)/2 + VREFN = VDD/2,为了达到最好的效果,VREFP 和 VREFN 与 VDD 和 VSS 的电压相同

B. ADC 外设不使用的情况下, VREFP 连接到 VDD, VREFN 连接到 VSS

如下表格式 ADC 参考电压配置:

5.2 ADC 引脚配置-2

ADC 采样引脚

A. 确保测量信号的电压应低于 VDD

B. IOCON 寄存器配置 ADC 采样引脚,应禁能内部上拉和下拉电阻,这点很重要,使能内部上下拉会影响采样精度

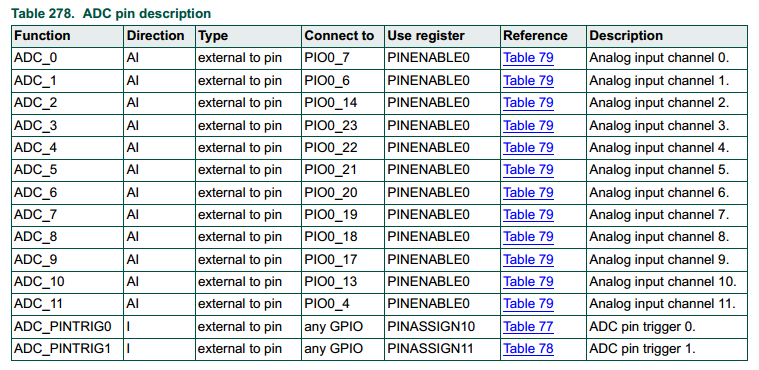

ADC 引脚配置如下表所示:

5.3 ADC 功能模块

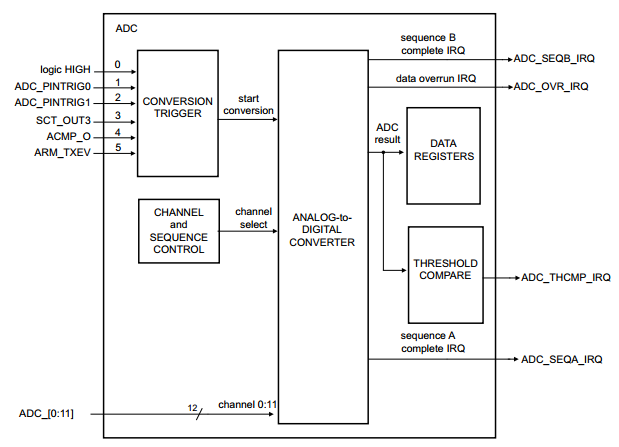

A. ADC 全精度的采样转换需要 25 个 ADC clock

B. ADC 的时钟来源于系统时钟,最大 ADC 的时钟频率为 30MHz

ADC Block Diagram 如下图所示:

5.4 ADC 寄存器描述

ADC 的寄存器可以分为四类:

A. 全局控制及数据寄存器:CTRL、 SEQA_CTRL、 SEQB_CTRL、SEQA_GDAT、 TRIM和SEQB_GDAT

B. 数据寄存器:DAT0 ~ DAT11

C. 采样结果进行比较相关的寄存器:THR0_LOW、 THR1_LOW、THR0_HIGH和THR1_HIGH

D. 中断相关的寄存器:INTEN、 FLAGS

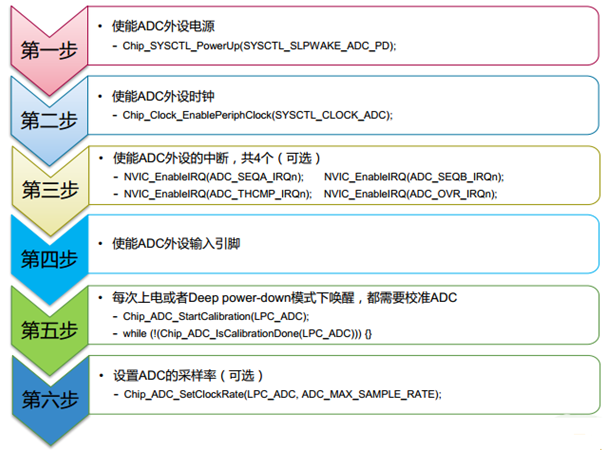

5.5 ADC 代码配置流程

六、ADC 实验

6.1 实验介绍

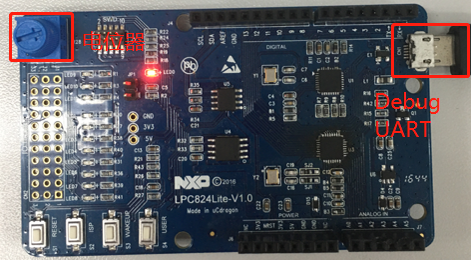

A. 通过本实验,理解和掌握 LPC82x ADC 的采样,ADC 的采样引脚为 P0.23

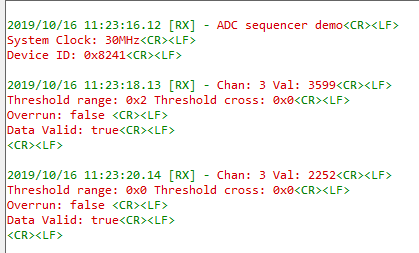

C. 结果:采样的结果会通过 DEBUG UART 口打印出来

6.2 软/硬件环境搭建

A. 硬件

评估板:LPC824Lite-V1.0

B. 工程位置

.\peri_example\adc\adc_example\project_adc_example.uvprojx

6.3 硬件配置

A. 无需特别的硬件配置

使用电位器来调节 ADC 的输入电压

DEBUG UART 口会打印出 ADC 的采样结果,波特率 115200

6.4 实验步骤

第一步 - 编译下载 ADC 工程生成的可执行文件

第二步 - 给板上电,按复位按钮开始动手实验

第三步 - 调节板子上的电位器,观察 DEBUG UART 口的打印结果

6.5 相关底层驱动 APIs 说明

1.初始化 ADC。使能 ADC 的时钟和电源

void Chip_ADC_Init(LPC_ADC_T *pADC, uint32_t flags)

2. 校准 ADC 外设

void Chip_ADC_StartCalibration(LPC_ADC_T *pADC)

3.设置 ADC 的时钟

STATIC INLINE void Chip_ADC_SetClockRate(LPC_ADC_T *pADC, uint32_t rate)

4.设置 ADC 序列

STATIC INLINE void Chip_ADC_SetupSequencer(LPC_ADC_T *pADC, ADC_SEQ_IDX_TseqIndex, uint32_t options)

5.使能 ADC 中断

STATIC INLINE void Chip_ADC_EnableInt(LPC_ADC_T *pADC, uint32_t intMask)

6.使能 ADC 序列

STATIC INLINE void Chip_ADC_EnableSequencer(LPC_ADC_T *pADC, ADC_SEQ_IDX_T seqIndex)

评论

sworpid

2019年11月22日

sworpid

2019年11月22日

我满分

2019年11月22日

我满分

2019年11月22日

sworpid

2019年11月22日

sworpid

2019年11月22日

我满分

2019年11月22日

sworpid

2019年11月22日