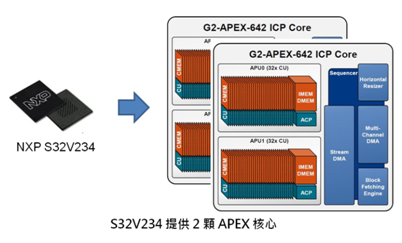

S32V234 處理器內搭配 2 顆 APEX 的核心,提供給我們使用與搭配。如下圖所示 :

APEX 的正確核心名稱為 G2-APEX-642 ICP Core ,其中名詞可拆解成以下定義 :

G2:為第二世代的意思 ( 2nd generation)

642:為 64 個 CUs 與 2 個 ACP

ICP:為影像領域處理器 ( Image Cogntion Processor )

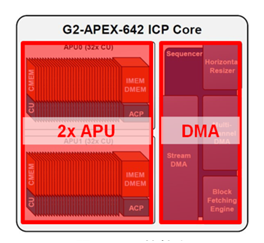

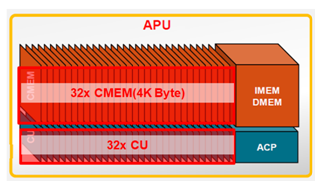

APEX 的核心架構是由兩大架構所組成,如下圖所示,

第一大架構為 APU (Array Process Uint) 矩陣運算單元,主要負責平行化處理,並配置 2 顆供使用。

第二大架構為 DMA( Direct Memory Acess) 快速存取記憶體架構,主要負責資料與記憶體之間的傳輸。

------------------------分割线-------------------------

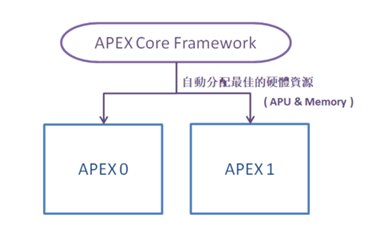

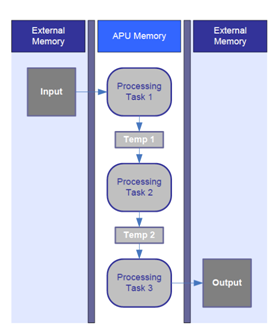

ACF 主要作用為替使用者配置最佳的硬體資源。此軟體層是以自動生產代碼的方式,直接取代向硬體溝通的動作,並分配最佳的 APU 與 Memory 資源。

* ACF 詳細使用介紹之後會以专题博文的方式介紹。

------------------------分割线-------------------------

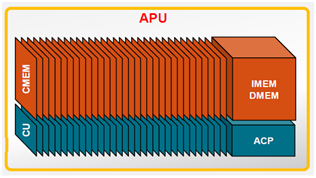

接續回到之前所提及的主要核心架構之一的 APU ,也是硬體加速的關鍵核心。

如 APU 架構示意圖,首先認識以下架構

- 1) CU(Computational Unit) 運算單元 : 為 APU 專門設計的小型運算單元。

- 2) ACP (Array Control Processor) 矩陣控制處理器 : 為專門控制與分配 CU 的一個處理器。

- 3) CMEM (Computational Memory) 運算處理記憶體 : 為 CU 所使用之記憶體,各 CU 配置 4KByte。

- 4) IMEM (Instruction Memory) 指令記憶體 : 為暫存指令類別的記憶體,並隨 ACP 配置於 CMEM。

- 5) DMEM (Data Memory) 資料記憶體 : 為暫存資料類別的記憶體,並隨 ACP 配置於 CMEM。

理解以上架構後,我們來探討 APU 硬體配置狀況吧!

如下圖所示

一顆 APU 是由 32 個 CU 以及 4KByte 的記憶體 (CMEM) 大小所構成。並由 ACP 與 IMEM / DMEM 進行分配與控制,最後透過第二大架構 DMA 的特性快速將資料進行傳輸,盡而達到硬體加速之目的。

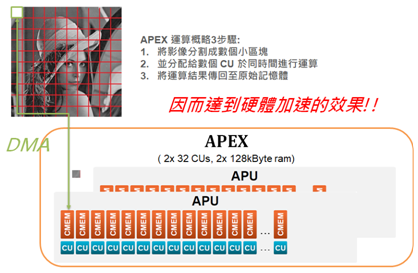

因此一顆 APEX 提供 2 顆 APU 核心作為使用,所分配到的資源為 64 個 CU 以及 256KByte 的記憶體 (CMEM),供給使用者運用與搭配。

因此可揣摩一下整個 APEX 的運算流程,如下图所示,

假設有一張圖片需給 APEX 運算將可以分成 3 個步驟

- 1) 將影像分割成數個小區塊,實質上稱作為 Chunk 。

- 2) 藉由 DMA 與 ACP 將資料傳至各個 Chunk 中,並於同時間進行平行化運算。

- 3) 運算完成後,再次透過 DMA 將資料傳送回到原本圖片的記憶體中。

*值得注意的是該資料不限至於影像,只要是數據型態即可作運用

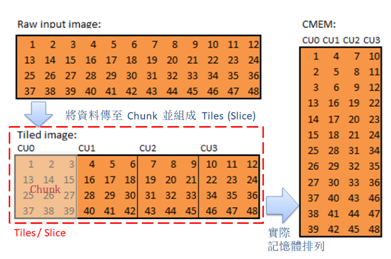

更進一步來說,APEX 會將 Chunk 組成 Tiles 的形式,以便控制與提高效能。

如 Chunk 與 Tiles 組成示意圖所示,其中 Tiles 與 Slice 皆描述一整片記憶體位置,由原始數據 (Raw input image) 的資料,可以被拆分成各個 Chunk 並設置於 CU0 至 CU3 之中,這樣排列成一條的方式即組成 Tile (Tile image) ,而實際排列則如同示意圖上記憶體 CMEM 所呈現的方式。

換個方式来说,即為單指令多數據流 (SIMD) 的架構,这也是 APEX 與 GPU 差異最大之處,因 GPU 屬於多指令多數據流 (MIMD) 故無法減少耗電量,而 APEX 能保持低功耗且仍有優渥的快速平行化運算速度,即為 APEX 的特點。如下图所示:

*詳細的速度比較將於後續博文跟大家分享。

本文给大家介绍了 APEX 的架构及其数据的处理流程,相信对大家进一步了解这个 S32V234 独有的视觉加速器会起到帮助。

接下来我们还会分享 ACF 詳細使用介紹、S32V APEXCV 的环境搭建 以及 S32V APEXCV Library 等介绍,敬请期待 飞车侠!!!

评论

Angel07

2020年7月16日