KV31时钟树Overview

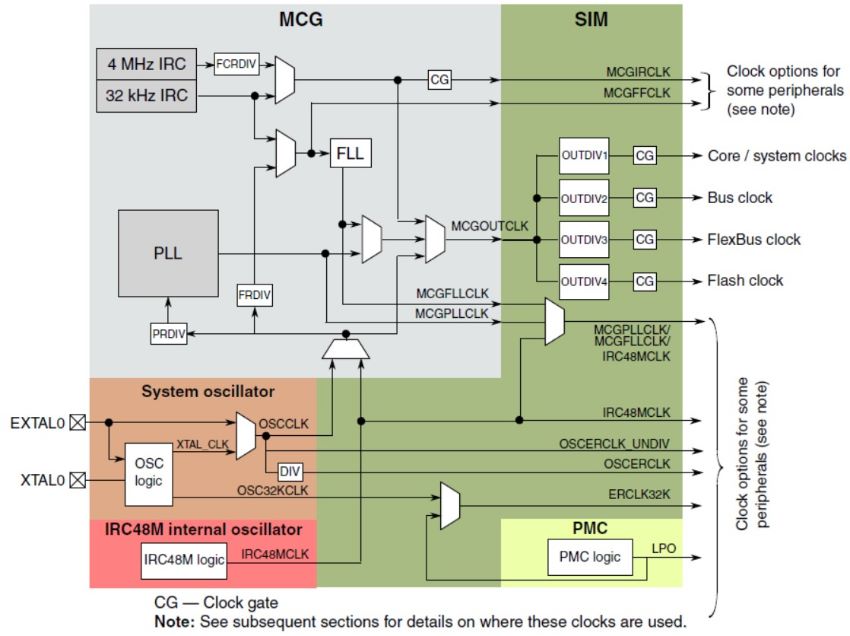

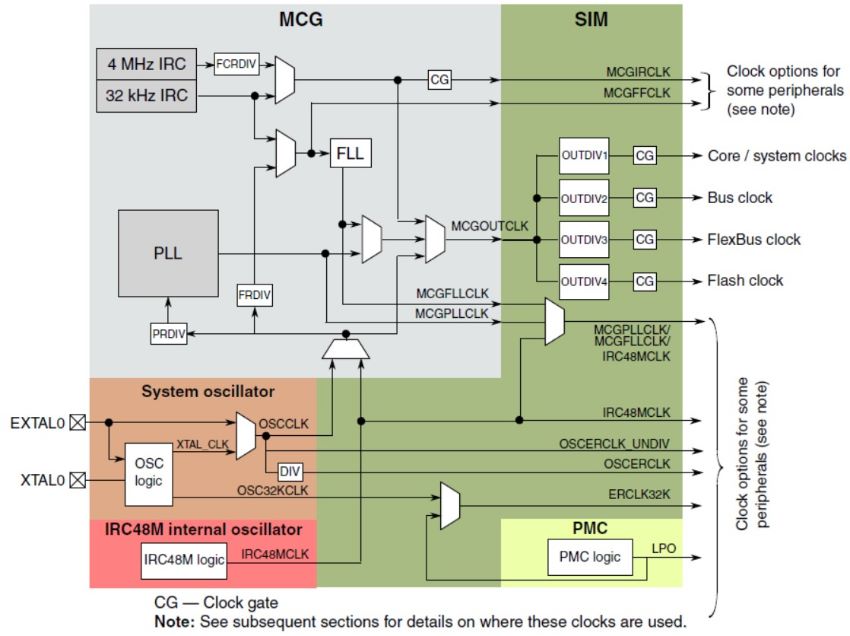

时钟是一个单片机系统的核心所在,几乎所有模块的运作都离不开时钟。而时钟源对于单片机来说就是心脏对人体一样的存在,是整个单片机系统不可或缺的一部分,不同的是单片机往往有多个时钟源。由于不同外设对时钟的需求不同,系统拿到时钟源后不会接提供给内核或外设使用,都会经过倍频、分频、多路输出等一系列操作,这样就构成了时钟树。而根据不同单片机复杂程度的不同时钟树也不同。KV31作为一颗电机控制转用 MCU ,有着较为复杂的时钟系统,下图给出了 KV31时钟树的整体框架。

MCG模块控制用于派生系统时钟的时钟源。时钟生成单元将选择的时钟源划分为各种时钟域,包括系统总线主机、系统总线从机和闪存的时钟。时钟生成单元还实现特定模块的时钟门控。

系统的主时钟由 MCGOUTCLK 时钟生成。时钟产生单元提供几个时钟分频器,允许设备的不同部分在不同的频率上计时。这允许在性能和功耗之间进行权衡。各种模块都有特定的时钟,可以从 IRC48MCLK 或 MCGPLLCLK 或 MCGFLLCLK 时钟中选择。

时钟分频器是通过 SIM 模块的 CLKDIV 寄存器来编程的。每个分频器是可编程的,从除以1到除以16。每个模块的时钟可以使用 SIM模块分别开关。这些位会在任何重置之后被清除,这将使时钟无法进入相应的模块以节省电能。在初始化一个模块之前,在SCGCx寄存器中设置相应的位来启用时钟。在关闭时钟之前,请确保禁用模块。对已禁用其时钟的外设的任何总线访问都会生成错误终止。

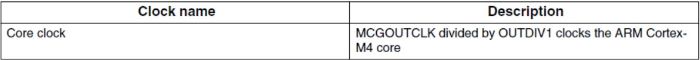

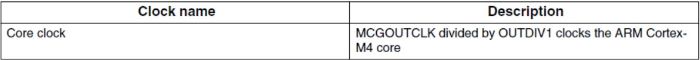

下表是对框图中时钟的描述:

多功能时钟发生器(MCG)

多功能时钟发生器(以下简称MCG)是 KV31 时钟系统的关键所在,对多个时钟源进行选择、处理、打磨,为MCU提供多个时钟选择。

MCG 模块包括一个锁频环(FLL)和一个锁相环(PLL)。的 锁频环可由内部或外部参考时钟控制。锁相环是由外部参考时钟控制的。模块可以选择FLL或PLL输出时钟,也可以选择参考时钟(内部或外部)作为 MCU 系统时钟的源。MCG 与晶体振荡器一起工作,该振荡器允许外部晶体、陶瓷谐振器或其他外部时钟源产生外部参考时钟。

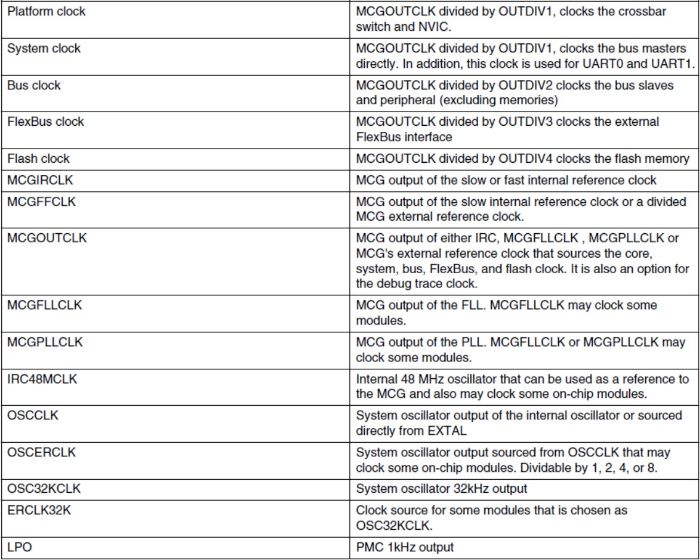

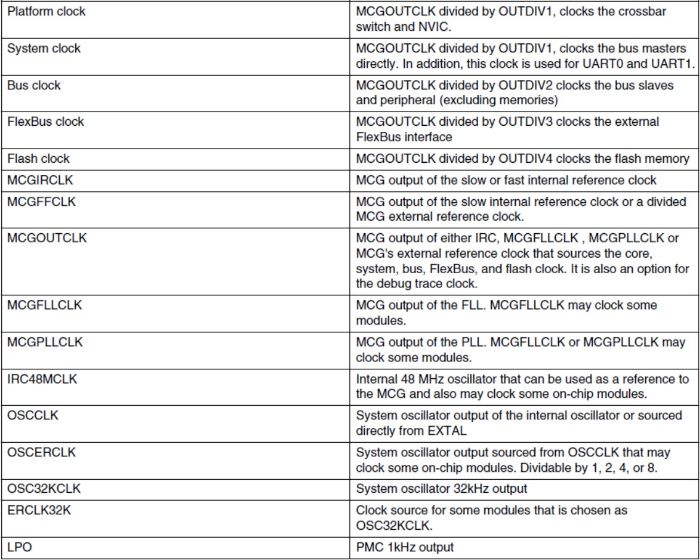

下图给出了MCG模块的框图:

MCG 模块的主要特性有:

1.锁频环(FLL):

•有效输入频率范围:31.25KHz~39.0625KHz。

•数控振荡器(DCO)。

• DCO 频率范围可编程多达四个不同的频率范围。

•选择编程和最大化 DCO 输出频率为一个低频外部参考时钟源。

•锁频环保护,防止 FLL 选择未准备好的时钟作为时钟源。

•内部或外部参考时钟可作为 FLL 源。

•可作为其他芯片外设的时钟源。

2.锁相环(PLL):

•有效输入频率范围:2MHz~4MHz。

•压控振荡器 (VCO)

•外部参考时钟作为锁相环的源。

•模块化 VCO 分频器

•阶段/频率检测器

•集成环路滤波器

•可作为其他芯片外设的时钟源。

3.内部参考时钟发生器:

•低速时钟带有九个校准位。

•快速时钟带有四个校准位。

•可以用作 FLL 的源时钟。在 FEI 模式下只能使用低速内部时钟。

•参考时钟 (IRC) 可以用作 FLL 源。

•可以选择慢时钟或快时钟作为 MCU 的时钟源。

•可作为其他芯片外设的时钟源。

4.来自外部晶体振荡器的时钟:

•可以用作 FLL 和 PLL 的时钟源。

时钟是一个单片机系统的核心所在,几乎所有模块的运作都离不开时钟。而时钟源对于单片机来说就是心脏对人体一样的存在,是整个单片机系统不可或缺的一部分,不同的是单片机往往有多个时钟源。由于不同外设对时钟的需求不同,系统拿到时钟源后不会接提供给内核或外设使用,都会经过倍频、分频、多路输出等一系列操作,这样就构成了时钟树。而根据不同单片机复杂程度的不同时钟树也不同。KV31作为一颗电机控制转用 MCU ,有着较为复杂的时钟系统,下图给出了 KV31时钟树的整体框架。

MCG模块控制用于派生系统时钟的时钟源。时钟生成单元将选择的时钟源划分为各种时钟域,包括系统总线主机、系统总线从机和闪存的时钟。时钟生成单元还实现特定模块的时钟门控。

系统的主时钟由 MCGOUTCLK 时钟生成。时钟产生单元提供几个时钟分频器,允许设备的不同部分在不同的频率上计时。这允许在性能和功耗之间进行权衡。各种模块都有特定的时钟,可以从 IRC48MCLK 或 MCGPLLCLK 或 MCGFLLCLK 时钟中选择。

时钟分频器是通过 SIM 模块的 CLKDIV 寄存器来编程的。每个分频器是可编程的,从除以1到除以16。每个模块的时钟可以使用 SIM模块分别开关。这些位会在任何重置之后被清除,这将使时钟无法进入相应的模块以节省电能。在初始化一个模块之前,在SCGCx寄存器中设置相应的位来启用时钟。在关闭时钟之前,请确保禁用模块。对已禁用其时钟的外设的任何总线访问都会生成错误终止。

下表是对框图中时钟的描述:

多功能时钟发生器(MCG)

多功能时钟发生器(以下简称MCG)是 KV31 时钟系统的关键所在,对多个时钟源进行选择、处理、打磨,为MCU提供多个时钟选择。

MCG 模块包括一个锁频环(FLL)和一个锁相环(PLL)。的 锁频环可由内部或外部参考时钟控制。锁相环是由外部参考时钟控制的。模块可以选择FLL或PLL输出时钟,也可以选择参考时钟(内部或外部)作为 MCU 系统时钟的源。MCG 与晶体振荡器一起工作,该振荡器允许外部晶体、陶瓷谐振器或其他外部时钟源产生外部参考时钟。

下图给出了MCG模块的框图:

MCG 模块的主要特性有:

1.锁频环(FLL):

•有效输入频率范围:31.25KHz~39.0625KHz。

•数控振荡器(DCO)。

• DCO 频率范围可编程多达四个不同的频率范围。

•选择编程和最大化 DCO 输出频率为一个低频外部参考时钟源。

•锁频环保护,防止 FLL 选择未准备好的时钟作为时钟源。

•内部或外部参考时钟可作为 FLL 源。

•可作为其他芯片外设的时钟源。

2.锁相环(PLL):

•有效输入频率范围:2MHz~4MHz。

•压控振荡器 (VCO)

•外部参考时钟作为锁相环的源。

•模块化 VCO 分频器

•阶段/频率检测器

•集成环路滤波器

•可作为其他芯片外设的时钟源。

3.内部参考时钟发生器:

•低速时钟带有九个校准位。

•快速时钟带有四个校准位。

•可以用作 FLL 的源时钟。在 FEI 模式下只能使用低速内部时钟。

•参考时钟 (IRC) 可以用作 FLL 源。

•可以选择慢时钟或快时钟作为 MCU 的时钟源。

•可作为其他芯片外设的时钟源。

4.来自外部晶体振荡器的时钟:

•可以用作 FLL 和 PLL 的时钟源。

•可以选择作为单片机的时钟源。

5.提供了 FLL 和 PLL 的参考除法器。

6.提供快速内部参考时钟的参考分配器。

7.MCG 锁相环时钟 (MCGPLLCLK) 作为其他片上外设的时钟源。

5.提供了 FLL 和 PLL 的参考除法器。

6.提供快速内部参考时钟的参考分配器。

7.MCG 锁相环时钟 (MCGPLLCLK) 作为其他片上外设的时钟源。

8.MCGFLL 时钟 (MCGFLLCLK) 是作为其他片上外设的时钟源。

9.MCG 固定频率时钟 (MCGFFCLK) 作为其他片上外设的时钟源。

10.MCG 内部参考时钟 (MCGIRCLK) 作为其他片上外设的时钟源。

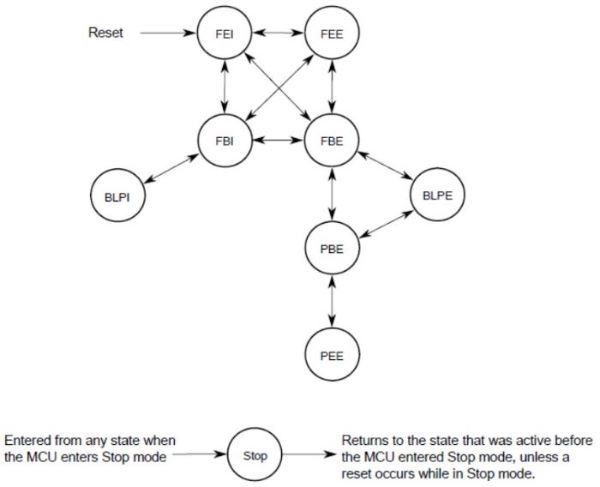

MCG工作模式

MCG可工作在以下几种模式,请结合 MCG 模块框图观看。

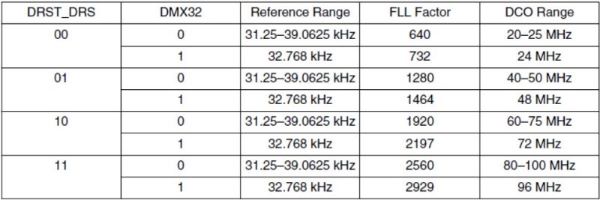

1.FLL Engaged Internal (FEI)(默认)

在FEI模式下,MCGOUTCLK 源自32 kHz内部参考时钟 (IRC) 控制的 FLL 时钟 (DCOCLK)。FLL 循环将 DCO 频率锁定为 FLL 因子(由[DRST_DRS] 和 [DMX32] 位选择)乘以内部参考频率。更多信息请参见 [DMX32] 描述。在 FEI 模式下,除非设置了 [PLLCLKEN],否则锁相环在低功耗状态下是禁用的。

2.FLL Engaged External (FEE)

在 FEE 模式中,MCGOUTCLK 源由外部参考时钟控制的 FLL 时钟 (DCOCLK)。FLL 循环将锁定 DCO 频率到 FLL 因子,如所选[DRST_DRS] 和 [DMX32] 位,乘以指定的外部参考频率 [FRDIV],请参阅[DMX32]位描述。在收费模式中 除非设置了[PLLCLKEN],否则 PLL 在低功耗状态下是禁用的。

3.FLL Bypassed Internal (FBI)

在 FBI 模式下,MCGOUTCLK由低速(32 kHz IRC)或高速(4 MHz IRC)内部参考时钟派生,由 [IRCS] 位选择。FLL 是可操作的,但其输出未被使用。当 MCGOUTCLK 从 [IRCS] 选择的内部参考时钟驱动时,这种模式有助于 FLL 获取其目标频率。FLL 时钟(DCOCLK)由慢速的内部参考时钟控制,DCO 时钟频率锁定一个乘因子,该乘因子由[DRST_DRS]和[DMX32]位选择,乘以内部参考频率。请参见[DMX32]位描述。在 FBI 模式下,锁相环在低功耗状态下被禁用,除非设置了[PLLCLKEN]。

4.FLL Bypassed External (FBE)

在 FBE 模式下,MCGOUTCLK 来自 OSCSEL 外部参考时钟。FLL 是可操作的,但其输出未被使用。当 MCGOUTCLK 从外部参考时钟驱动时,这种模式有助于 FLL 获得其目标频率。DCOCLK 由外部参考时钟控制,DCO 时钟频率锁定一个乘因子,该乘因子由[DRST_DRS] 和 [DMX32] 位选择,请参阅 [DMX32] 位描述。在 FBE 模式下,除非设置了[PLLCLKEN],否则锁相环将在低功耗状态下禁用。

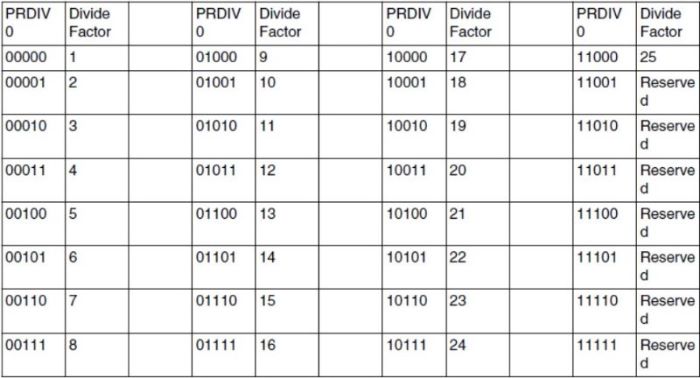

5.PLL Engaged External (PEE)

在PEE模式下,MCGOUTCLK 由外部参考时钟控制的锁相环的输出导出。锁相环时钟频率锁定到一个乘法因子(由其相应的 VDIV 指定)乘以所选锁相环参考频率(由其相应的 VDIV 指定) PRDIV。锁相环的可编程参考分频器必须配置为产生一个有效的锁相环参考时钟。FLL在低功耗状态下被禁用。

6.PLL Bypassed External (PBE)

在PBE模式下,MCGOUTCLK 源自 OSCSEL 外部参考时钟;锁相环是可操作的,但是它的输出时钟没有被使用。当 MCGOUTCLK 从外部参考时钟驱动时,这种模式有助于锁相环获得目标频率。锁相环时钟频率锁定一个乘法因子(由其[VDIV]指定),乘以锁相环参考频率(由其[PRDIV]指定)。在准备过渡到 PEE 时,锁相环的可编程参考分频器必须配置为产生有效的锁相环参考时钟。FLL 在低功率状态下被禁用。

7.Bypassed Low Power Internal (BLPI)

在BLPI模式下,MCGOUTCLK 源自内部参考时钟。FLL 是禁用的即使将 [PLLCLKEN] 设置为1,也禁用PLL。

8.Bypassed Low Power External (BLPE)

在BLPE模式下,MCGOUTCLK 源自 OSCSEL 外部参考时钟。即使将 [PLLCLKEN] 设置为1,也会禁用 FLL 和 PLL。

各种模式之间的转换需要遵循以下环节

--END--

评论