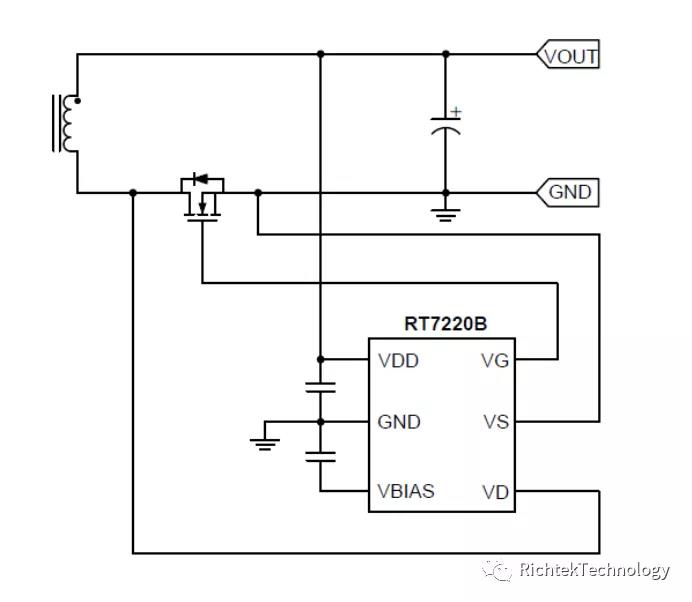

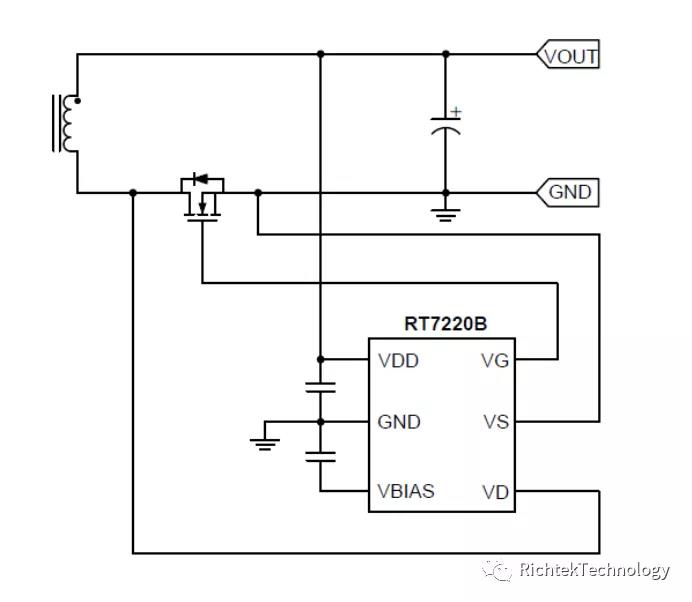

今天要说说RT7220B 同步整流控制器,它的任务是驱动 MOSFET 工作,以代替传统的整流二极管,来提高效率。电路如下图所示:

对应到传统的电路图中,RT7220B 和它外接的 MOSFET 就相当于续流二极管,只不过是被放在了 GND 一侧而已。这幅图当然也不是完整的电路图,它仅仅反映了次级侧绕组、输出电容、整流开关和整流控制器的关系,RT7220B 的内部电路框图如下:

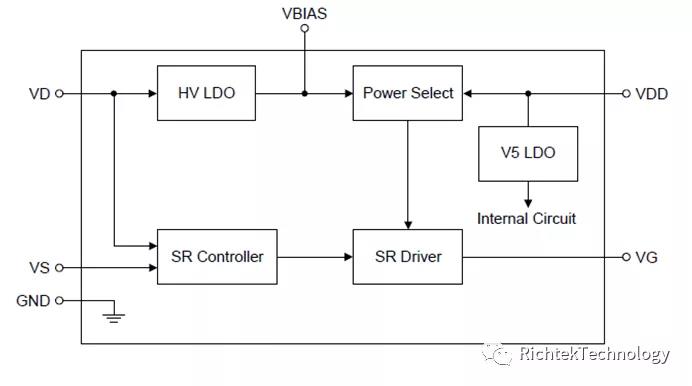

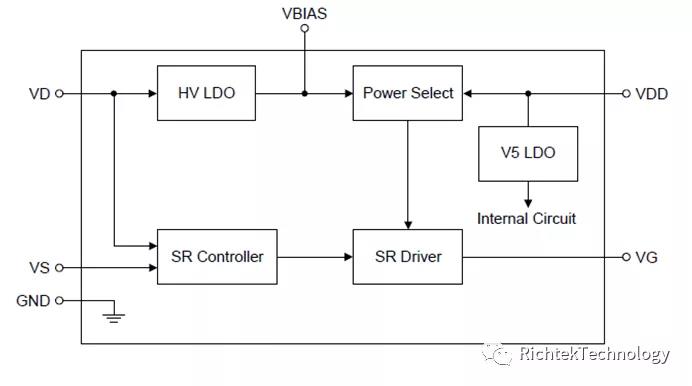

VD、VS 和 VG 分别连接到 MOSFET 开关的漏极、源极和栅极,前两个都是检测输入端,VG 则为输出端。同步整流控制器 SR Controller 根据 VD 和 VS 两个点的电压关系决定其输出状态,其输出经 SR Driver 变换为大信号经 VG 输出决定外部 MOSFET 的工作状态,顺利实现同步整流的作用。根据设计目标,RT7220B 在反激式应用中支持电流连续模式 CCM、电流非连续模式 DCM 和准谐振 QR 工作模式,其重点是要在适当的时机打开 MOSFET 实现续流工作,在适当的时机关闭 MOSFET 阻止电流的流动,将死区时间缩减至最小,这样就能实现效率的最大化。

同步整流控制器要工作是需要电能供应的。由于 VDD 端和电源输出端连接在一起,当输出电压正常时( > 4.7V )其内部电源由 VDD 端提供,否则其来源便是 VBIAS 外接电容储存的能量,它由 VD 内部连接的一个高压线性稳压器提供,这部分能量实际上是来自于初级侧导通期间的变压器传导,就像一个真正的变压器能够做到的样子,我这样说是因为我认为反激式电源的变压器并非变压器,它只是一个储能元件,而在这个时候却是表现为变压器的作用。由此设计即可推知 RT7220B 几乎在任何一个工作周期都可以通过工作实现完全的同步整流功能,只要 VBIAS 电容的储能足够一个驱动周期使用即可,而这是很容易实现的,但在实际上它又不会这样去做,因为当驱动 MOSFET 所消耗的能量多于利用它内部的体二极管导通所消耗的能量时,实现同步整流就不再是一个好的策略,这种状况在低消耗的节能模式下就会出现。

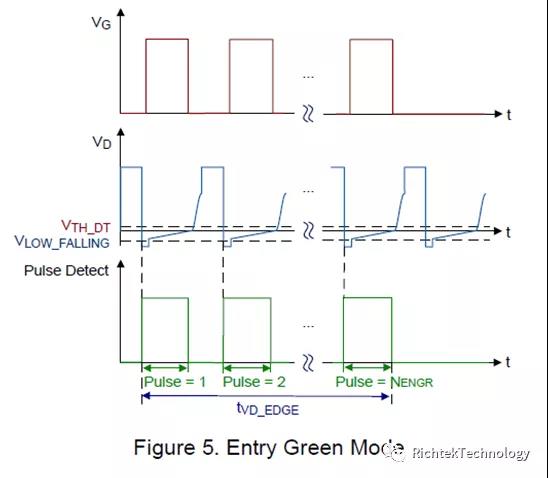

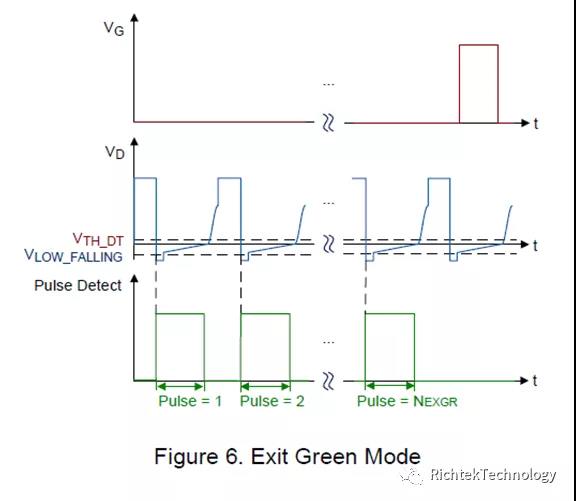

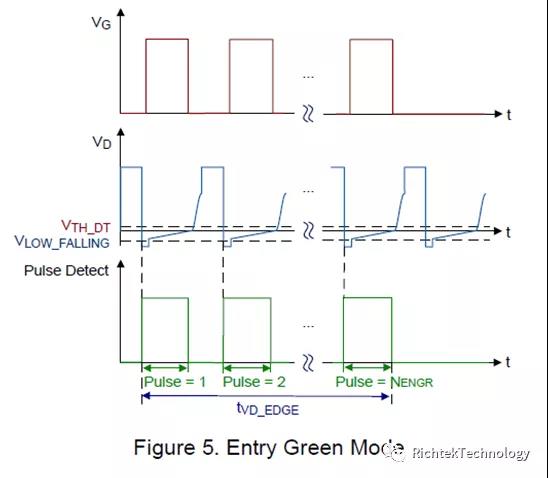

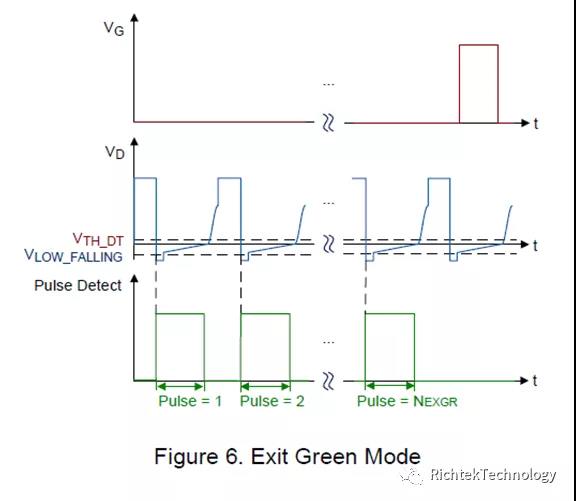

实际上,RT7220B 内部含有一个计数器不断地对 VG 端的输出脉冲进行计数,当它在 tVD_EDGE(= 10ms)时间段内的计数低于 32 时,RT7220B 就会进入节能模式,不仅不会再做驱动 MOSFET 导通的动作,其正常的静态消耗也会从 1mA 左右下降到 120µA 左右(最大 160µA)。而在节能模式下,RT7220B 又会对 VD 脉冲进行计数,当它在同样时长内的计数大于 64 时,RT7220B 就立即回到正常的同步整流状态。RT7220B 进、出节能模式的过程如下面两幅图所示:

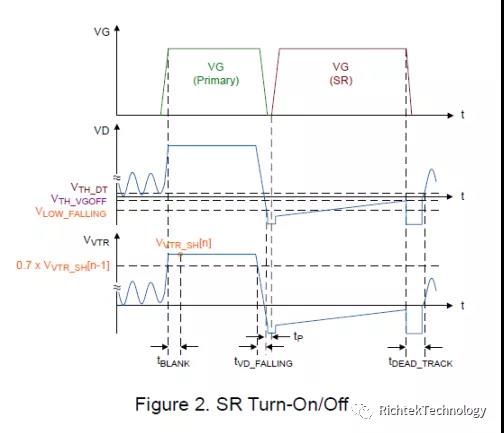

当初级侧的功率开关截止时,变压器次级侧就会有电流流过 MOSFET 体二极管,这将造成 VD 端的电压低于 VG 端,RT7220B 实现同步整流的方法就是对 VD 电压低于 VG 电压的状况进行监测,一旦发现两者间的压差低于 VLOW_FALLING,它便立即在 VG 端输出高电压驱动 MOSFET 导通以实现损耗更低的续流过程。

对应到传统的电路图中,RT7220B 和它外接的 MOSFET 就相当于续流二极管,只不过是被放在了 GND 一侧而已。这幅图当然也不是完整的电路图,它仅仅反映了次级侧绕组、输出电容、整流开关和整流控制器的关系,RT7220B 的内部电路框图如下:

VD、VS 和 VG 分别连接到 MOSFET 开关的漏极、源极和栅极,前两个都是检测输入端,VG 则为输出端。同步整流控制器 SR Controller 根据 VD 和 VS 两个点的电压关系决定其输出状态,其输出经 SR Driver 变换为大信号经 VG 输出决定外部 MOSFET 的工作状态,顺利实现同步整流的作用。根据设计目标,RT7220B 在反激式应用中支持电流连续模式 CCM、电流非连续模式 DCM 和准谐振 QR 工作模式,其重点是要在适当的时机打开 MOSFET 实现续流工作,在适当的时机关闭 MOSFET 阻止电流的流动,将死区时间缩减至最小,这样就能实现效率的最大化。

同步整流控制器要工作是需要电能供应的。由于 VDD 端和电源输出端连接在一起,当输出电压正常时( > 4.7V )其内部电源由 VDD 端提供,否则其来源便是 VBIAS 外接电容储存的能量,它由 VD 内部连接的一个高压线性稳压器提供,这部分能量实际上是来自于初级侧导通期间的变压器传导,就像一个真正的变压器能够做到的样子,我这样说是因为我认为反激式电源的变压器并非变压器,它只是一个储能元件,而在这个时候却是表现为变压器的作用。由此设计即可推知 RT7220B 几乎在任何一个工作周期都可以通过工作实现完全的同步整流功能,只要 VBIAS 电容的储能足够一个驱动周期使用即可,而这是很容易实现的,但在实际上它又不会这样去做,因为当驱动 MOSFET 所消耗的能量多于利用它内部的体二极管导通所消耗的能量时,实现同步整流就不再是一个好的策略,这种状况在低消耗的节能模式下就会出现。

实际上,RT7220B 内部含有一个计数器不断地对 VG 端的输出脉冲进行计数,当它在 tVD_EDGE(= 10ms)时间段内的计数低于 32 时,RT7220B 就会进入节能模式,不仅不会再做驱动 MOSFET 导通的动作,其正常的静态消耗也会从 1mA 左右下降到 120µA 左右(最大 160µA)。而在节能模式下,RT7220B 又会对 VD 脉冲进行计数,当它在同样时长内的计数大于 64 时,RT7220B 就立即回到正常的同步整流状态。RT7220B 进、出节能模式的过程如下面两幅图所示:

当初级侧的功率开关截止时,变压器次级侧就会有电流流过 MOSFET 体二极管,这将造成 VD 端的电压低于 VG 端,RT7220B 实现同步整流的方法就是对 VD 电压低于 VG 电压的状况进行监测,一旦发现两者间的压差低于 VLOW_FALLING,它便立即在 VG 端输出高电压驱动 MOSFET 导通以实现损耗更低的续流过程。

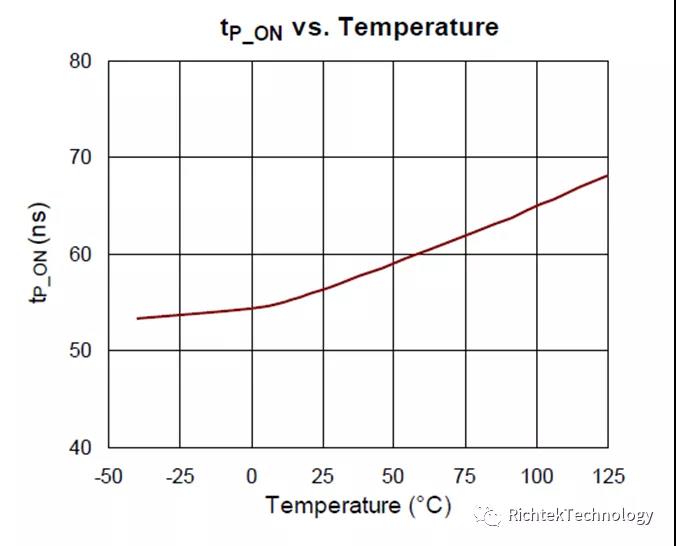

在上图中所示的 VLOW_FALLING 便是前段文字中提及的触发同步导通的阈值电平,此后经过时间 tP_ON(上图所示为 tP),同步 MOSFET 即开始进入导通过程,而 IC 设计之关键就是要使 tP_ON 尽可能地短,这样才能尽早实现同步整流过程。在 RT7220B 规格书所提供的数据中,这个tP_ON 的典型值为 100ns,但从该参数与温度的关系曲线来看,其范围在 60ns±10ns 以内(见下图)。关于前者,我们可以把它理解为芯片在测试过程中的控制值,后者则是具体到某一个体的表现情况。

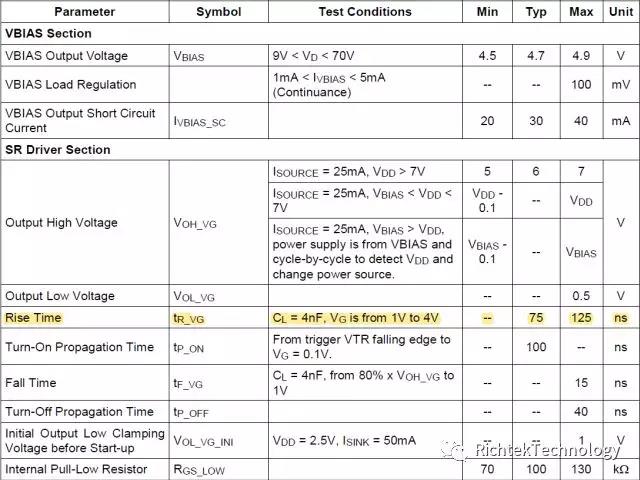

VG 输出高电平驱动 MOSFET 导通的过程需要耗时多久呢?这取决于所用 MOSFET 的输入电容、MOSFET 的导通阈值等与 MOSFET 本身有关的特性和 VG 端的输出能力,前者由用户的选择决定,只有 VG 端的输出能力是由 RT7220B 本身的设计所决定的,而 PCB 的设计也将对此造成影响,因为它会形成驱动路径上的串联阻抗。

VG 输出高电平是一个简单的描述,其真实的实现过程则要复杂得多。IC 内部能做的是先将一个连接到 GND 的开关断开,再将一个连接到电源端的开关接通,然后便有电流从电源端经 VG 端流出,经过外部连接以后进入 MOSFET 的栅极电容并经其源极回流到电源地,这样便使 MOSFET 栅极相对于其源极的电压越来越高,最后达到几乎等于电源电压的程度。当栅极电压在此过程中达到开启电压时,MOSFET 的源极和漏极之间便形成了沟道并开始流过电流,导通的目标也就实现了。所以所谓的高电平实际上是依靠一个过程来完成的,我们利用这个电路或是过程中的某个特征来对 IC 的驱动能力进行评价,而这样的选择可以有很多种,RT7220B 规格书在表现这一点的时候只给出来一行数据:

如上图中高亮显示的一行,其意思是说:当 VG 端外接 4nF 电容时,VG 电压从 1V 上升到 4V 需要的时间典型值为 75ns,最大值为 125ns。到了具体应用中,这个时间到底为多少,就可以参照这个信息来做评估。

对问题的思考一旦深入到过程,有的事情就变得复杂起来。前面说了芯片发现 VD 电压跌落到 MOSFET 开始导通的延迟时间典型值是 100ns,这个数据就出现在上述高亮行的下一行,其中的注解说明了两个时间点,一个是 VD 电压下降过程中触发同步动作的时间,一个是 VG 电压上升到 0.1V 的时间,当需要对此时间段的长度进行评估的时候,就需要考虑到实际的测试条件,需要知道电源电压、负载电容、串联阻抗等数据,当这些因素发生改变的时候,所有的测试结果也都会改变,给人的认识也就会不同,所以单独看某一个数据实际上是没有什么意义的,仅仅是能帮助我们做个评估而已,但在某些时候这也已经够了,因为实际的应用常常也不需要多么地精确。