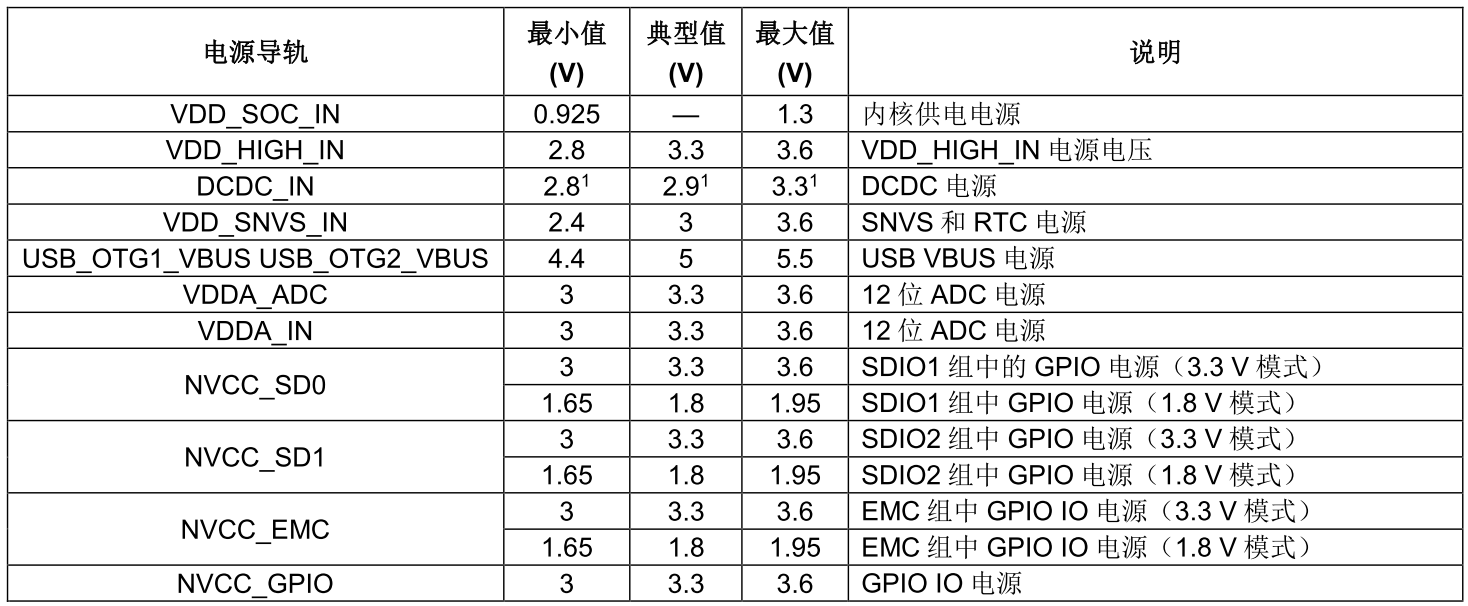

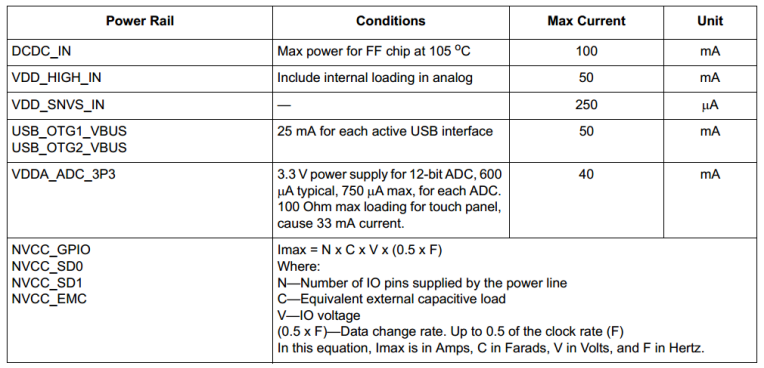

上图是设计当中应该注意的电源域。主要是

1.电源输入DCDC_IN

2.VDD_HIGH_IN ,以及对SNVS和RTC供电的VDD_SNVS_IN

3.对内核供电的VDD_SOC_IN 以及负责对其他模块供电的电源域

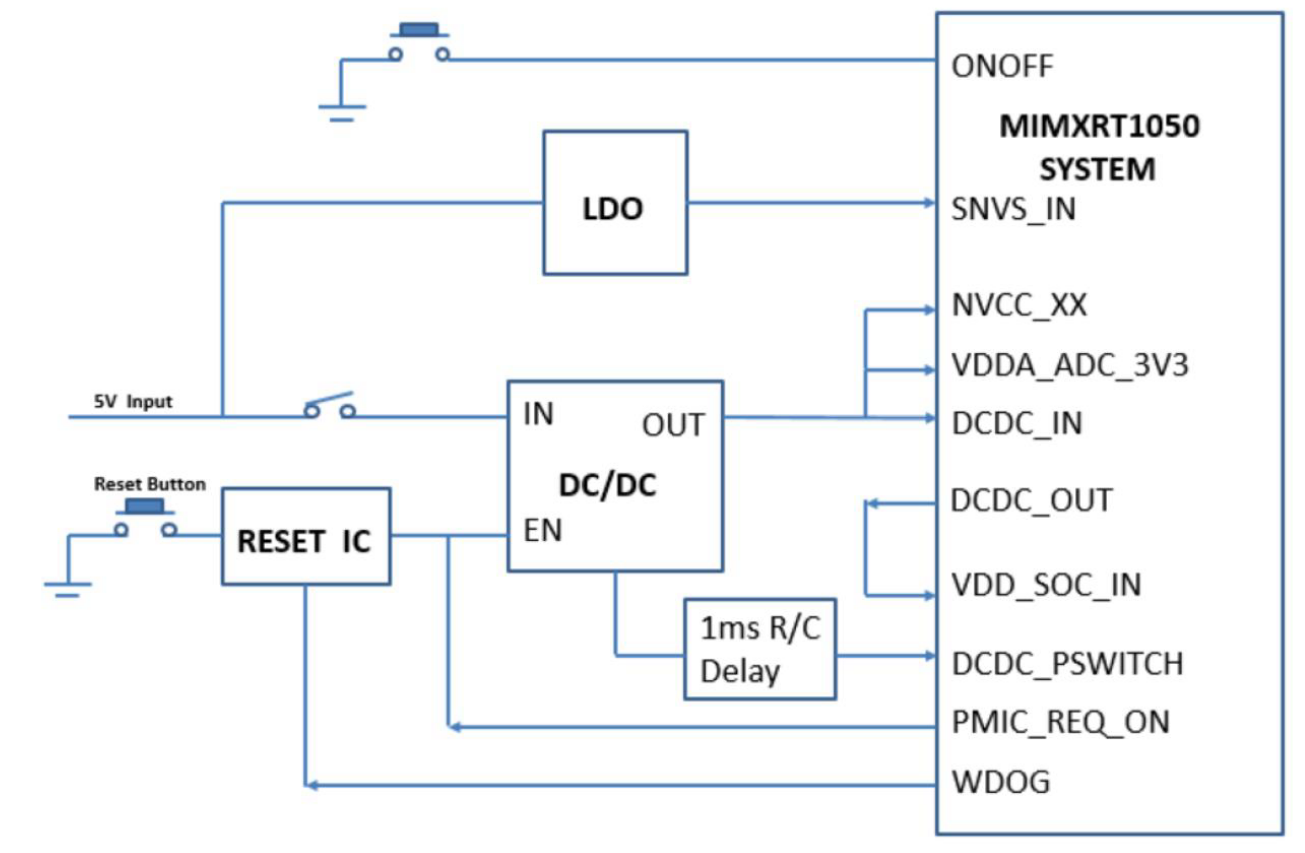

下图是比较典型的设计方案。

外围加了RESET IC、LDO 和DCDC模块。先看看上电流程:

首先是提供5V电源对LDO供电,LDO输出至VDD_SNVS_IN,上电稳定后PMIC_ON_REQ自动置高,使能外部DCDC模块为其他电源域供电,而DCDC_PSWITCH由于RC电路会延迟1ms拉高,从而延缓内部DCDC的使能,而后 DCDC_OUT 输出,为 VDD_SOC_IN 供电:延迟的目的是等DCDC_IN 稳定,再启动内部DCDC。在此期间,VDD_SNVS_IN 需先于其他电源域上电。

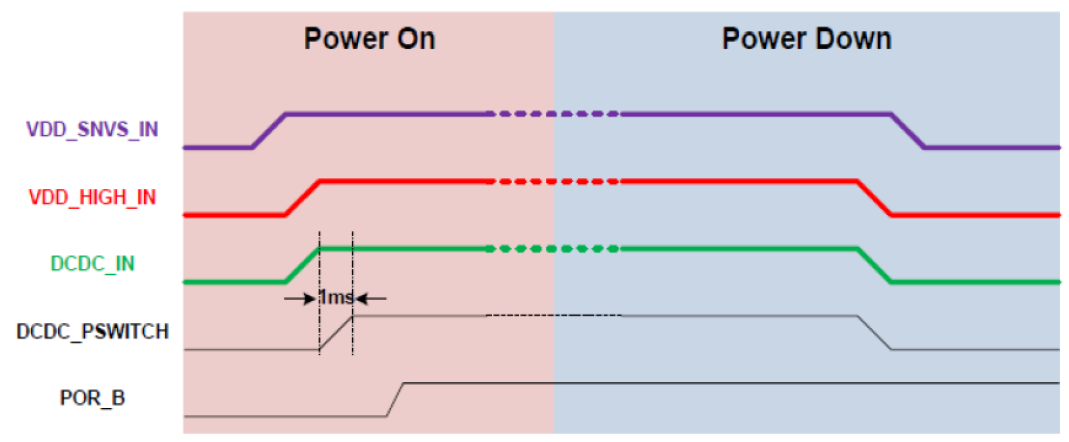

上下电时序如下图所示

上电期间,POR_B需要保持拉低直到其他电源域上电完毕。下电时序则几乎与上电时序相反:VDD_SNVS_IN 须后于其他pin下电后才能下电。如果在系统掉电期间不需要实时时钟功能,则可将 VDD_HIGH_IN和 VDD_SNVS_IN 连接在一起,也就是说不论上电还是下电,VDD_SNVS_IN 都可以跟VDD_HIGH_IN短接或一块上下电。与这些序列的任何偏差都可能导致以下情况:

1.上电阶段电流过大

2.设备启动失败

3.对处理器造成不可逆转的损害(最坏情况)

如果不需要lowest sleep power mode(SNVS Mode) ,SNVS_IN可以跟DCDC_IN、VDDA_ADC、VDD_HIGH_IN、NVCC_XXX一起短接,确保同时上电,从而去掉外部DCDC,用LDO单独供电。如果觉得前面的方案外围元器件过多,希望裁剪以节省成本也是可以,这就是其中一种方案。但是有些元件的裁剪会影响稳定,例如reset IC:虽然非必需,但是可以确保POR_B在上电完成之前稳定拉低,避免影响上电时序。

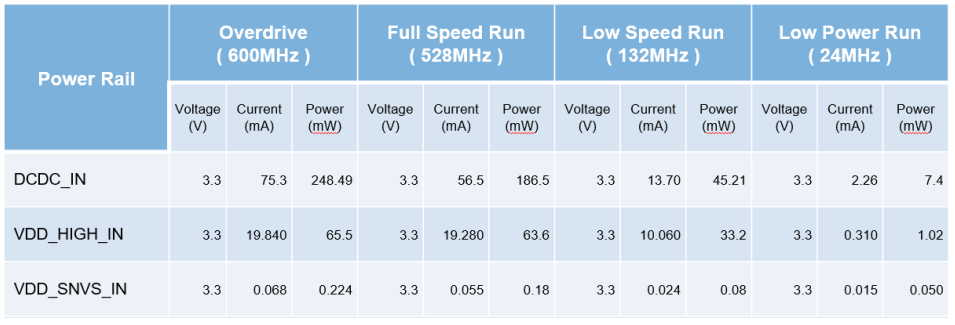

为了保证i.MXRT能正常运行,LDO和DC-DC的选择也需要对 i.MXRT的工作能耗相关的参数进行考量。以下分别是不同主频的 i.MXRT 几个主要电源域在不同频率下的工作电流,以及最大的工作电流,可供参考

(由于测量方式和具体硬件不同,具体情况可能略有差别,仅供参考)

由于篇幅原因,其他外围阻容感器件的选用在此就不一一展开,有兴趣的童鞋可以到本文末找到更具体的参考文档查阅。

参考文档:

NXP : 《MIMXRT1050/MIMXRT1060 处理器硬件开发指南 》(2—2019 年 2 月 )

评论