近些年来 ARM Cortex-M 阵营各厂商 (ST、NXP、ATMEL、Freescale……) 发布新产品的节奏越来越快,以及微控制器应用普及程度的加深,越来越多的开发者把更多精力投注在应用层开发上,花在对底层技术上的时间越来越少。

希望借助之前对底层的一些积累,可以帮到大家快速的建立对 Cortex-M 系列处理器 ( M0 / M0+ / M3 / M4 / M7 以及新的 M23 / M33) 的底层技术:芯片内核、编译器/开发环境底层、底层软件、调试技术等的快速积累,可以帮助大家更好、更快、更可靠的开发产品。

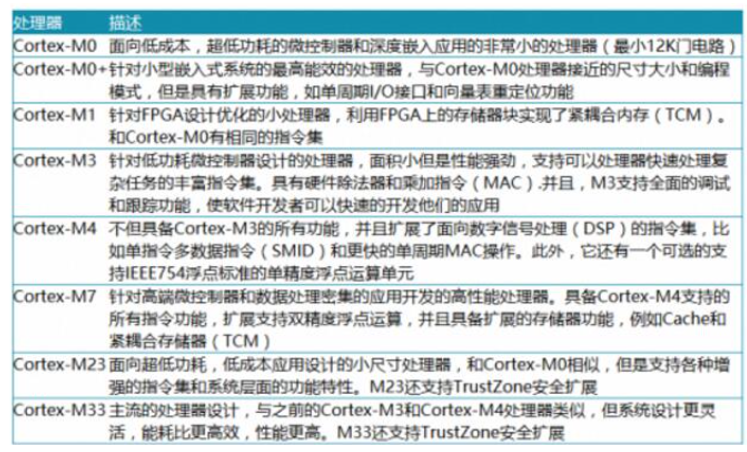

ARM Cortex-M 系列微控制器概况:

老的 ARM5、ARM7、ARM9、ARM11 时代的处理器都是历史,ARM 公司从 ARMv6-ARMv7时代开始 ARM 开始使用 A、R、M 系列来命名其新的处理器。

- A 系列为应用处理器,其中 A 可以理解为 Application,现在主流的智能手机几乎都是 ARM 的 A 系列内核,从早期的 A8、A9 到后来的 A15、A57 到现在的 A72、A73、A75 内核。主要用于运行 iOS、Android、Linux 等操作系统。

- R系列为实时处理器,其中 R 为 RealTime,R7、R8 等主要用于硬盘、4G 通信模块、相机等领域,这个系列处理器性能也非常彪悍,有兴趣的童鞋可以自己去 ARM 官网看看,蛮有意思的。

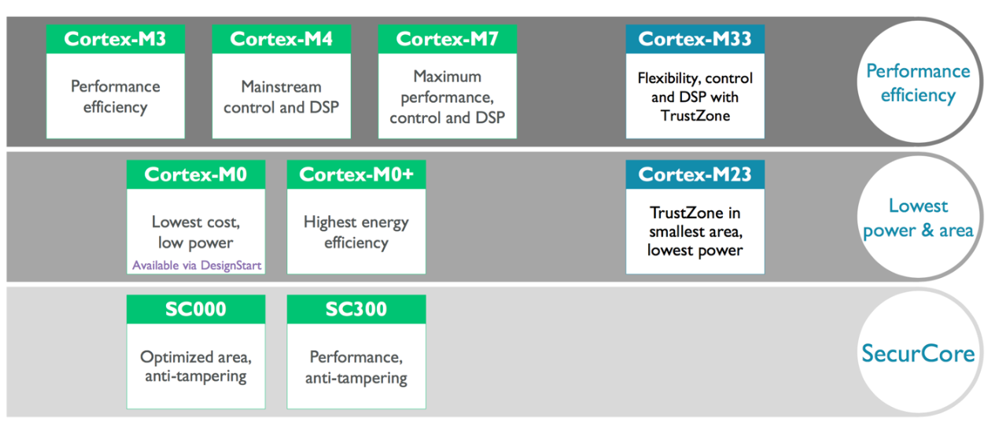

- M 系列处理器,其中 M 指的是 Microcontroler 目前主要有 M0、M0+、M3、M4、M7 以及新发布不久的基于 ARMv8-M 构架的 M23、M33,其中 M23 为 M0 & M0+ 的升级,M33 为 M3、M4 的升级。

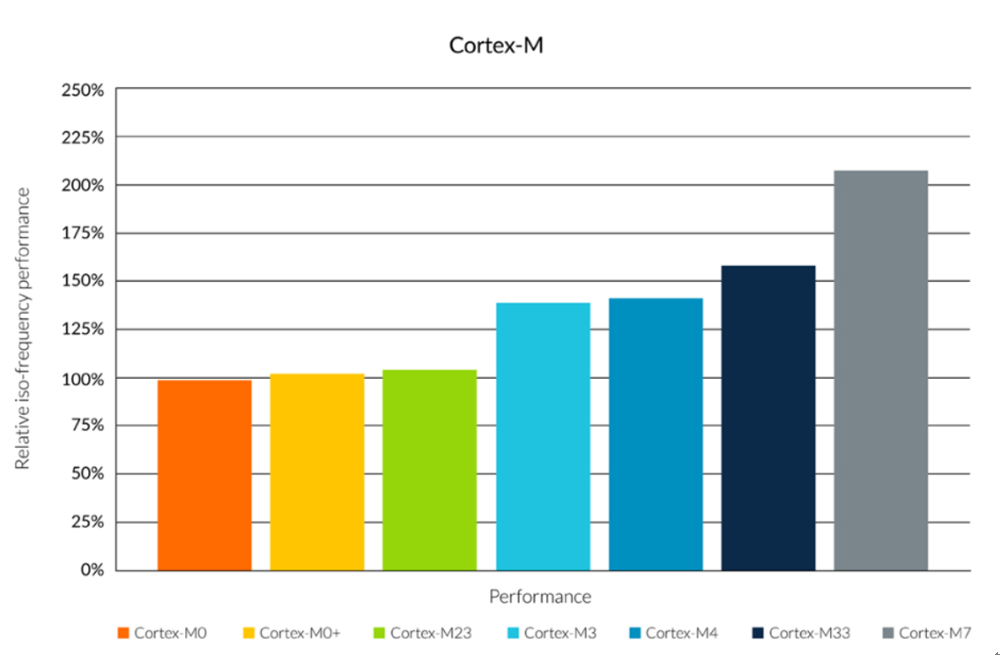

Cortex-M 性能天梯如下图:

上图为同等主频下,各个内核可以提供的运算性能的大概的对比关系,评判一个处理器处理性能一直是一个难题,有很多的评判标准,上图是 ARM 官网提供的,

Cortex-M 系列在ARM官网上一直是以 Coremark 分数为主要评测标准,大家可以参考,真实的性能对比还要看具体应用。

① M23 是基于最新的 ARMv8-M 构架的主要关注低功耗应用的微控制器,未来会是M0、M0+ 的替代品。

② M33 是基于最新的 ARMv8-M 构架的主要关注高能效应用的微控制器,未来会替换 M3、M4 。

③ M7 是老一点的 ARMv7-M 构架专注高性能的微控制器,从上图中也看得出, M7性能最强。

具体参考下图:

M0+ 简述

下面简单说一下 M0+、M0 作为过去时的微控制器这里略过,以 90nm 工艺为例M0+ 与 M0 的主要区别大家能用到的主要是以下几点:

1、M0+ 功耗更低,比 M0 低约 30%,这里说的只是内核功耗,真正落到芯片上还要算上外设、时钟系统等功耗,差距并没有 30% 那么大。

现在大家看到的 M0+ 功耗更低更多的是来自工艺的精进上,M0 早些年上市时主要是130nm/140nm/180nm 工艺,而导了 M0+ 时代更多的变成了 90nm,内核 & 工艺两方面的改进使得 M0+ 相比 M0 功耗要低得多。

现在 ARM 官网上也挂出了 40nm 工艺的 M0+ 功耗数据,几乎只有 90nm 工艺 M0+ 的 40%,但目前市面上还没有看到 40nm 工艺的 M0+ 产品,不过估计离上市不远了。早期 M0 的动态功耗多集中于 110uA/MHz~160uA/Mhz 之间,

而现在的 M0+ 处理器,功耗已经可以做到 65uA/MHz 甚至更低了;

2、流水线由 3 级改成 2 级;

3、在 M0+ 芯片中,GPIO 是直接挂在 M0+ 内核上的,而 M0 内核的芯片中,GPIO是挂在 APB 总线上的;这是什么意思呢?简单来说,M0+ 芯片中 GPIO 翻转速率可以达到系统内核时钟的一半,而 M0 的 GPIO 要慢得多,

因为 M0+ 内核直接访问 GPIO 并予以控制,M0 芯片则是 M0 内核要先访问 AHB 总线,再访问 APB 总线,再访问 GPIO 才能进行控制。

上图为 M0+ 处理器在三种不同工艺下内核面积、动态功耗以及性能的对比。

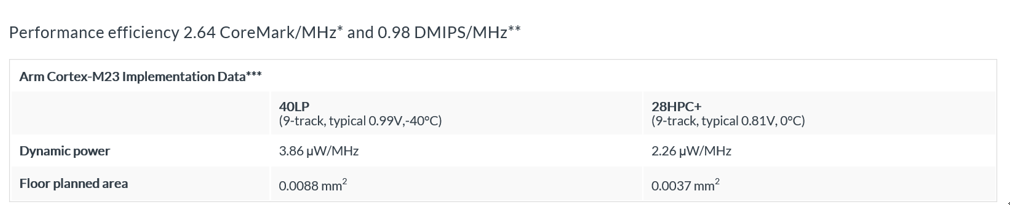

M23 简述

上图为 M23 处理器在三种不同工艺下内核面积、动态功耗以及性能的对比。

- Cortex-M23 最重要的特色是加入了 TrustZone 安全基础技术

- 极紧凑的架构与布线 · 强化的调试纠错和追溯能力(对开发商的生产力提高至关重要)

- 存储保护单元获得改善(该单元定义软件组件的访问许可,全新设计提升编程的效率,重新定义存储区域)

- 新增多条增强性能的指令

M4简述

先上 M4 的性能表:

上图为 M4 处理器在三种不同工艺下内核面积、动态功耗以及性能的对比。

现在主流的 M4 处理器基本都集中在 90nm 工艺的范畴上,内核动态功耗基本上是 M0+ 的 3 倍多,晶元面积是 M0+ 的 4 倍左右,同等主频下性能大概提升接近 40%。

考虑到具体应用,M0+ 的量产芯片大都主频较低,M4 相对高不少,所以实际功耗以及性能差距会更大。随着 M4 的出现 M3 现在在市场上面的新的应用越来越少,这里就不单独介绍 M3 了。

现在新的 M4 微控制器呈现了以下几个发展方向,代表未来几年的微控制器发展方向:

1、高能效比:早期的 M3 / M4 功耗大都在 300+uA/MHz 左右,现在新的 90nmLP工艺下新的 M4 微控制器的功耗已经下降到 100-200uA/MHz 的水平,未来会更低,能效比会更高;

2、向着更高的工艺挺进:目前我了解到NXP已经开始着手设计 40nm 工艺的 M4处理器,国内的 GD 也开始尝试用 55nm 甚至更高的工艺设计 M3/M4 微控制器,一旦这些更先进工艺处理器落地,

M4 微控制器的价格 & 功耗会被大幅度拉低,M4 的能效比会比现在 90nm 工艺的 M0+ 更高,这会是一个相当重要的改变;

3、安全:最近 1-2 年各个大的半导体厂商设计的新的微控制器很多都加入了安全单元,各种对称 / 非对称加密的协处理引擎被加入到新的 M4 控制器中,AES、SHA、3DES 等,为了适应新的物联网应用,

安全都是未来微控制器的设计重点,这点在新的 ARMv8-M 中体现尤为明显,安全特性功能是 M33 与 M4 最大的区别,以后我们找机会单独说 M23 与 M33 。

4、SOC/SIP 化:这点体现的最早,基本上从 M3 时代,M0 / M3 就被大量 SOC化,市面上大量的无线 SOC 都是 M0 / M3 / M4 内核,国内近 1-2 年大量厂商开始试水 SIP,国内目前大量 SIP 芯片内部集成了 M0 / M3 / M4 裸片。

M33 简述

上图为 M33 处理器在三种不同工艺下内核面积、动态功耗以及性能的对比。

因为 Cortex-M33 设计是非常可配置的,某些指令也是可选的。

例如:

- DSP 指令 ( Cortex-M4 和 Cortex-M7 支持的)是可选的

- 单精度浮点运算指令是可选的,这些指令是基于 FPv5 的,并且比 Cortex-M4 多几条。

Cortex-M33 也支持那些 ARMv8-M Mainline 引入的新指令:

- 支持 TrustZone 安全扩展的指令

- 载入获取及存储释放指令 (支持 C11)

M7 简述

目前市面上量产的 M7 芯片并不多,只有 ST、ATMEL、NXP 有少数几个型号;

M7 性能非常彪悍,几乎比同主频下的 M4 提升近 50%( M7 的六级超标量流水线真不是盖的~),NXP 新量产的 i.MXRT1050 (据说是 40nm 工艺)系列 M7 处理器甚至飙到了 3000+ 的 CoreMark,

以前的传统 M3 / M4 的 CoreMark 超过 300 的都凤毛麟角,M7 一下子把 Cortex-M 系列微控制器的性能提升了至少 10 倍,但目前从市场占有率来说,M7 还比较新应用还偏狭窄,未来可以畅想的空间还很大。

Cortex-M 系列介绍:

————————————————

版权声明:

- 本文为 CSDN 博主「Solaris_超」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_39118482/article/details/79424316

- 来源:ARM

评论