一、 内容简介

本文主要介绍了 S32K 系列的内核与外设,将分为《内核篇》与《外设篇》两篇连载。本文《【S32K 开发指南】内核与外设-内核篇》介绍了 S32K 系列的内核:ARM Cortex-M0+/M4 ,和与之相关的中断异常处理、存储器映射。本文还介绍了 S32K 系列 MCU 中的总线矩阵:crossbar switch ,和 S32K 系列内部的存储器:P-Flash、FlexNVM、EEEPROM 和 SRAM。

二、 S32K 系列内核:ARM Cortex-M0+/M4F

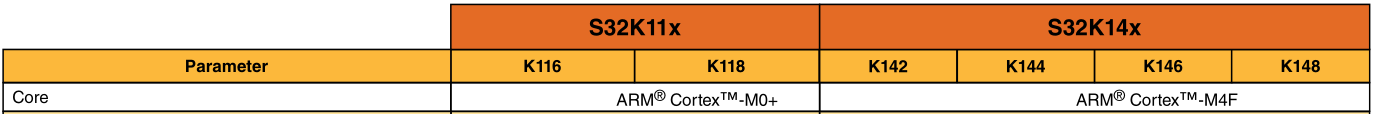

图 1 S32K 系列 MCU 内核

S32K 系列 MCU 基于 ARM®Cortex®-M0+/M4F 内核,如图 1,S32K11x 系列采用 ARM®Cortex®-M0+内核,而 S32K14x 系列采用 ARM®Cortex®-M4F 内核。

S32K11x:ARM Cortex-M0+

ARMv6-M,16-bit Thumb 指令集

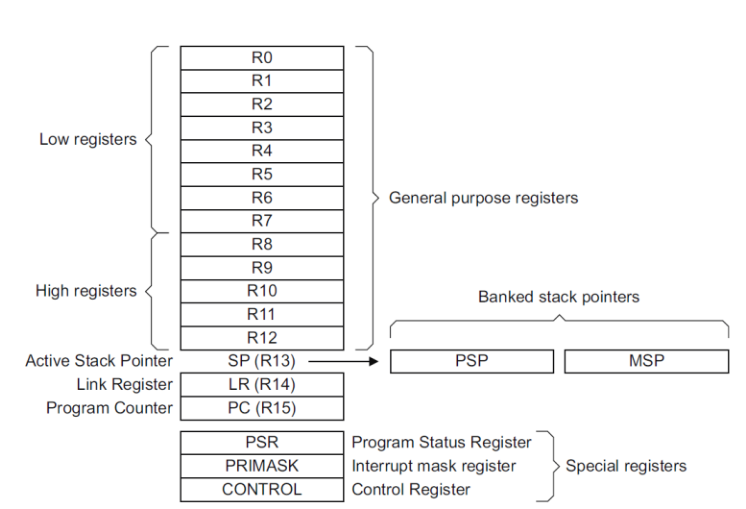

CPU 内核寄存器用于储存内核数据处理的中间结果,其访问速度是最快的,CPU 所有的数据都需要使用 load 指令先加载的 CPU 通用寄存器中,处理完成后,再使用 store 指令存回 SRAM 或者外设寄存器。

M0 内核具有以下特点:

- 功耗低:Cotex-M0 处理器的功耗仅有 85μW/MHz,在所有 ARM 处理器中最低。

- 简单:M0 指令只有 56 个,使得使用者可以快速掌握整个 Cortex-M0 指令集。

- 支持低能耗连接:可以适用于如 Bluetooth Low Energy(BLE)、IEEE 802.15 和 Z-wave。

图 2 ARM Cortex-M0 内核寄存器

S32K14x:ARM Cortex-M4F

ARMv7-M,16 bit+32 bit Thumb2 指令集

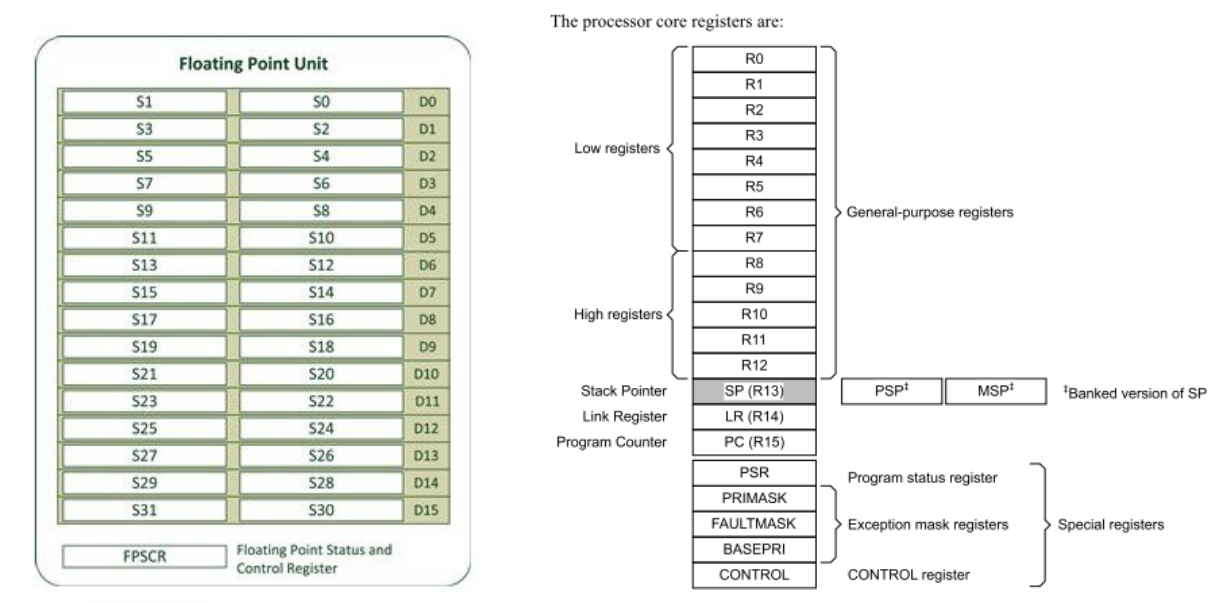

图 3 ARM Cortex-M4F 处理器与寄存器表

CM4F 内核有专门的 32-bit FPU 协处理器寄存器 S0~S31 及状态控制寄存器(FPSCR);

CM4F 内核 FPU 有浮点数指令集;工作时不占用 CPU 通用寄存器和 ALU 资源,更高效;且中断发生时,可以通过 lazy interrupt 处理自动判断是否压栈这些 FPU 寄存器。

M4F 相较于 M0,强化了运算能力,新加了浮点、DSP、并行计算等,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。其高效的信号处理能力与 Cortex-M 系列处理器的低功耗、低成本和易于使用的优点的组合,很好的满足了专门面向电动机控制、汽车、电源管理、嵌入式音频和工业自动化市场的新型类别的灵活解决方案。

三、 S32K 系列内核:中断与异常

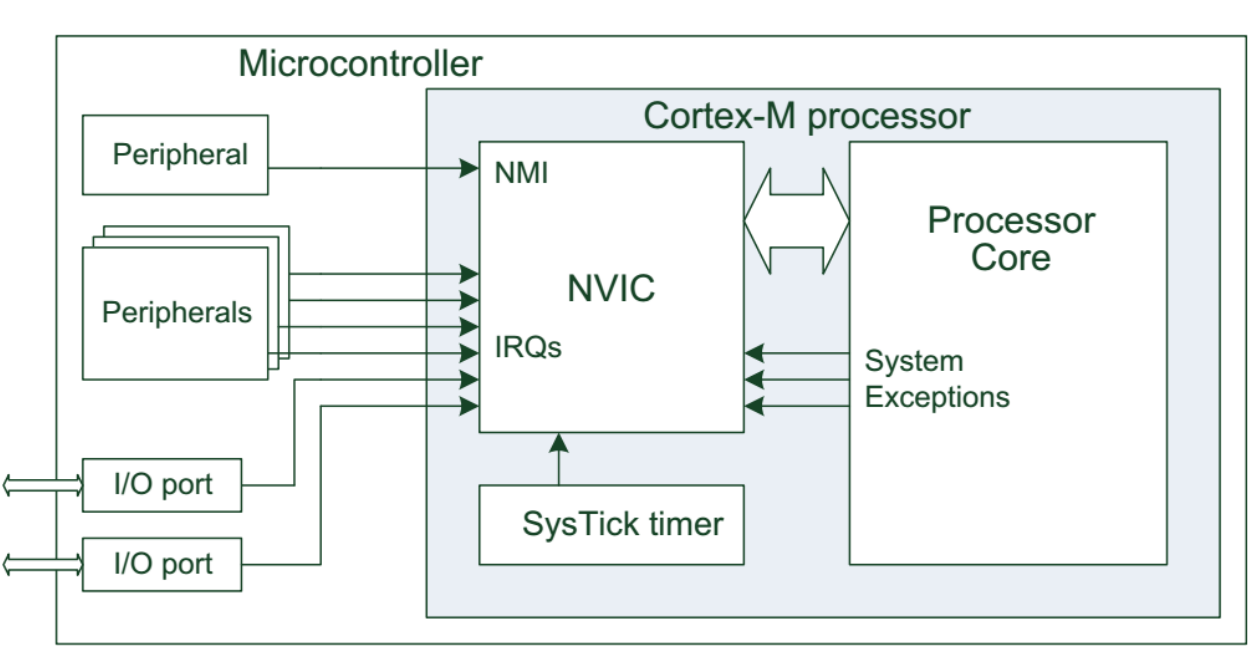

图 4 ARM Cortex M 系列 MCU 中断框图

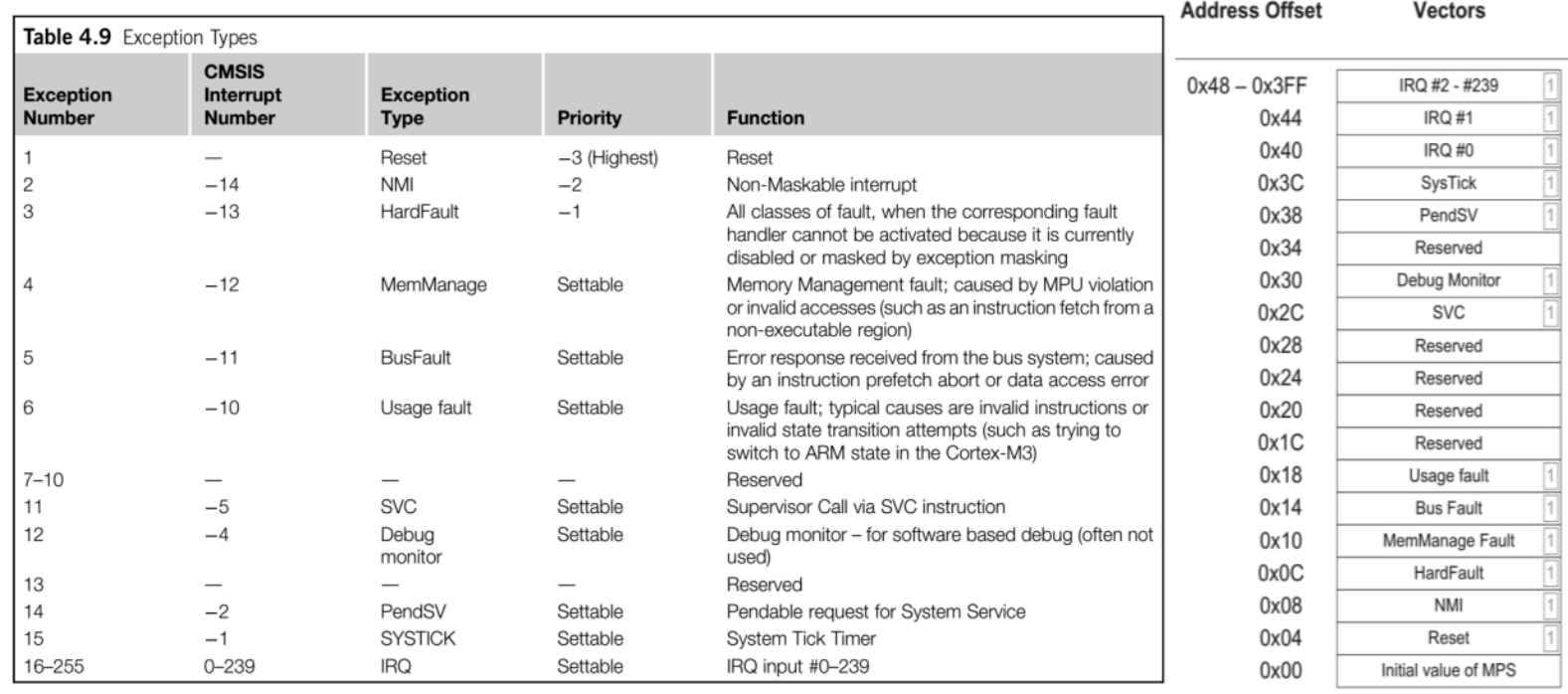

图 5 CM4F 中断类型和中断向量表

ARM Cortex M 系列 CPU 内核的所有系统异常和外设中断(IRQ 中断)都有 NVIC 统一管理;

相较于 CM4F,ARM Cotex M0+ 没有 MemManage、BusFault 和 UsageFault 异常;

Reset(-3)、NMI(-2) 和 HardFault(-1) 异常是默认是能的,且优先级固定,其余异常和 IRQ 中断的优先级可配置,数字越小优先级越高,默认优先级为 0 ——可配置最高优先级;

默认复位后中断向量表基地址在 0x0000 地址,通过修改 NVIC-> 寄存器可以将中断向量表重映射到其他地址(比如 SRAM 中);

ARM Cortex M 系列 CPU 内核都继承了 24-bit SysTick Timer 定时器和 SCV 及 PendSV 异常,前者用于产生 RTOS 的内核(Kernel)心跳,后者用于实现 RTOS 的任务上下文(context)切换,从而方便不同 ARM Cortex M 系列 CPU 内核带 RTOS 的应用层代码移植;

一个外设 IRQ 中断要被 CPU 响应,需要配置:

- 配置外设设能外设功能中断;

- NVIC 中响应的 IRQn 使能;

- 配置该 IRQn 中断优先级(可选);

- 将该 IRQn 的中断 ISR注册到中断向量表中

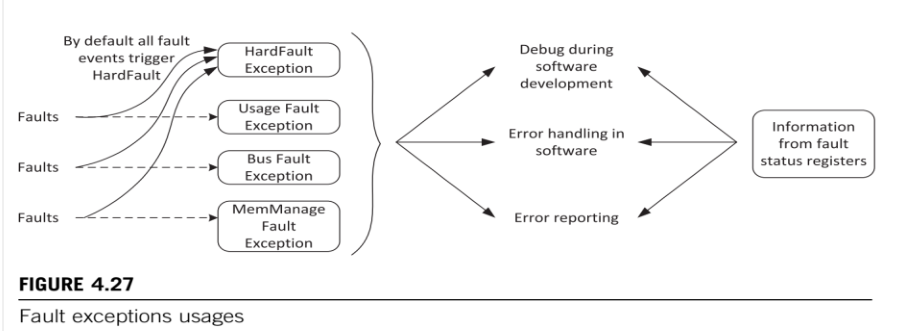

在 CM4F 内核中,默认配置 MemManage、BusFault 和 UsageFault 异常关闭,相应的异常都会触发 HardFault 异常;通过 SCB 模块相关寄存器可以查到具体的的异常源。

图 6 ARM Cortex M 系列 CPU 内核 异常处理

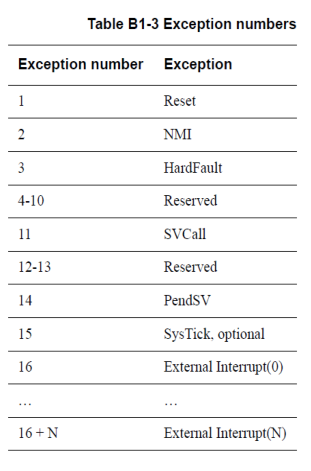

图 7 ARM Cortex M0+ 内核中断管理

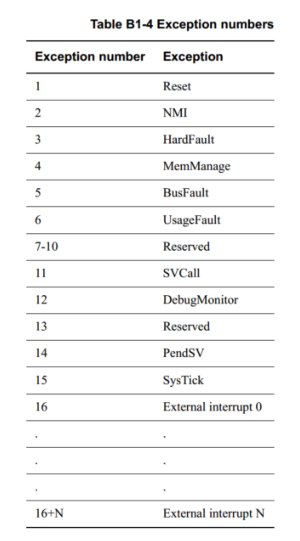

图 8 ARM Cortex M4F 内核中断管理

ARM Cortex M0+ 内核支持最多 64 个中断管理;

ARM Cortex M4F 内核支持最多 256 个中断管理;

在 ARM Cortex M0+ 内核中未实现 MemManage(#4)、BusFault(#5)、UsageFault(6#) 和 DebugMonitor(#12)异常。

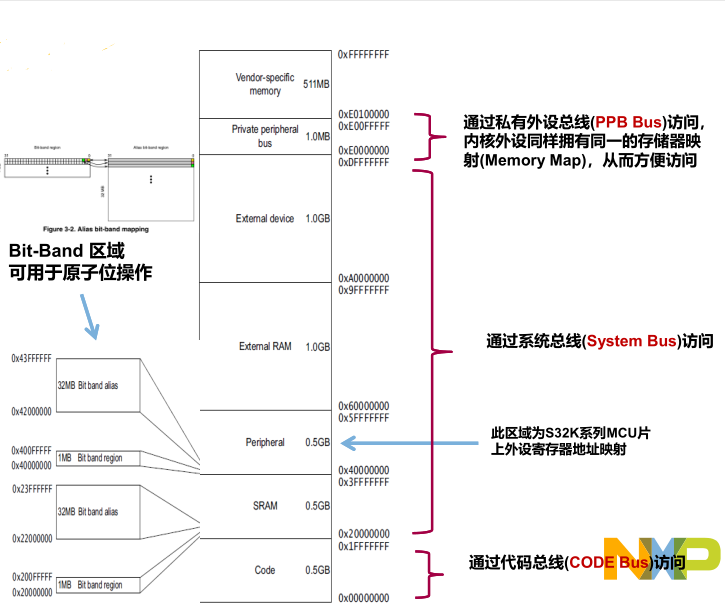

四、 S32K 系列内核:存储器映射

图 9 S32K 系列内核存储器映射

由 ARM 公司预定义的 Cortex M 系列 CPU 内核存储器地址映射;

P-Flash、D-Flash/FlexNVM 和 FlexRAM/EEE 映射到代码区,SRAM 和外设映射到 SRAM 和外设区,这样程序运行时,可实现真正的哈弗架构;

统一的 PPB 和 复位中断向量表(0 地址)映射方便应用程序代码在不同的 ARM Cortex M 系列内核之间移植。

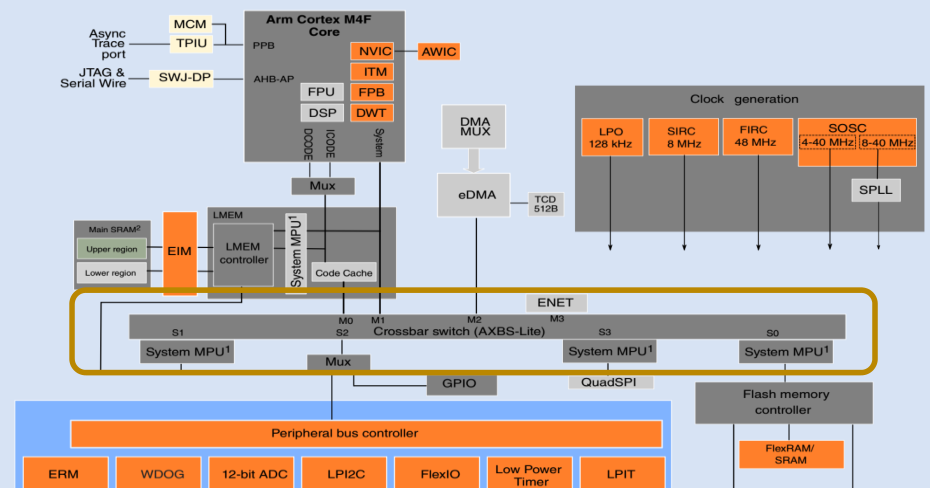

五、 S32K 系列 MCU 内部互联矩阵(crossbar switch)

图10 S32K 系列 MCU 内部互联矩阵(crossbar switch)

S32K 系列 MCU 的 Crossbar Switch(AXBS-Lite)是改进的 ARM AMBA 总线矩阵,用于互联 CPU 内核与系统存储器及外设模块的访问(读写);

AXBS-Lite 的 Master 可以主动发起数据访问请求,而 Slave 则只能被动接受访问;

- 每个 Crossbar Switch 的端口都有自己的控制总线、地址总线额和数据总线;

- Master 的工作频率高于 Slave,eg.CM4F core @max 112MHz vs. Flash @max 28MHz in HSRUN 模式;

- 所有片上模块(比如 GPIO、ADC、定时器和通信外设)都是统一挂在外设桥(S2-AIPS-Lite)上的;

- 两个 Crossbar 的 master 可以同时访问不同的 slave,从而保证 MCU 系统工作带宽;

- Master 对 Slave 的访问受 MPU 的保护。

S32K11x:

- 2 个 master 和 3 个 slave

S32K14x:

- 3 个 master 和 3 个 slave(S32K142/4/6)

- 4 个 master 和 4 个 slave(S32K148)

六、 参考文献

[1] NXP 官方网站 S32K144 开发板页面:https://www.nxp.com/design/development-boards/automotive-development-platforms/s32k-mcu-platforms/s32k144-evaluation-board:S32K144EVB

[2] PS32K144HFT0VLLT-datasheet.pdf,NXP

[3] S32K144RM_Rev1_DraftH.pdf,NXP

评论

DING

2021年6月25日