PF502x 系列是 NXP 推出的一款多通道电源管理芯片,其安全等级达到了 ASIL-B。PF502x 适用于各种应用,包括信息娱乐、ADAS、Vision 和雷达,既可作为独立电源解决方案,也可作为另一个 NXP PMIC(如 PF8200) 或 SBC(如 FS8500)的配套产品。

下面就来介绍下系列中的其中一款 - PF5020 的特点及其在硬件设计上的注意点。

1. 芯片介绍

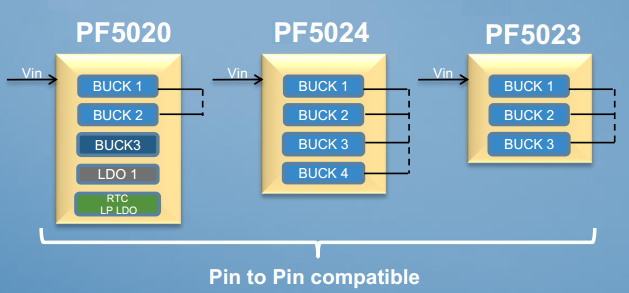

PF5020 是 NXP 推出的 PF502x 系列中的一款,整个 PF502x 系列目前一共有三款分别是:PF5020、PF5023 和 PF5024,它们除了输出资源有区别外基本特性都是相同的,且是 Pin 对 Pin 兼容的,具体框图及区别如下图:

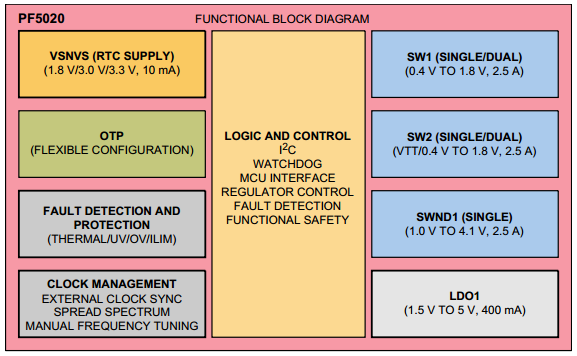

PF5020 主要性能特征如下:

- 三路高效降压转换器

- 一路可切换为负载开关的线性调整器

- 一路开关/线性调整器提供给 RTC 电源

- 符合 ASIL-B 安全级别

- 支持 OTP,用于灵活的设备配置

- 40-pin 6x6 QFN 封装

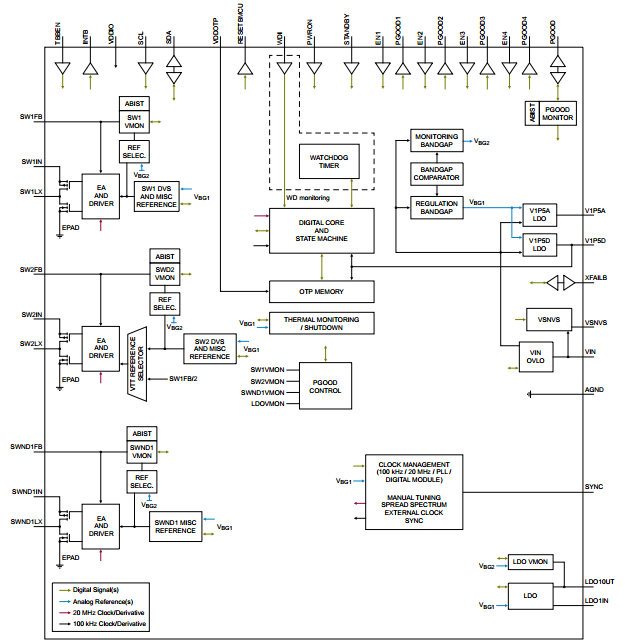

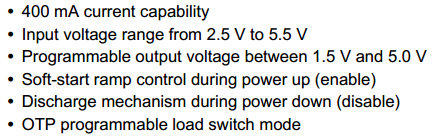

1.2 PF5020 内部框图如下:

1.3 PF5020 功能框图如下:

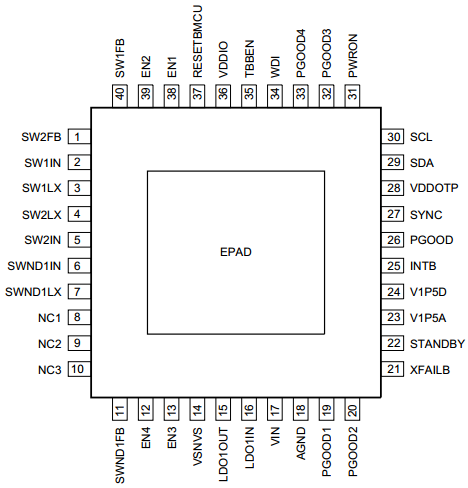

1.4 封装及管脚介绍

PF5020 封装为 HVQFN40(SOT618-14),其封装引脚分布图如下:

2. 模块功能简介

2.1 VSNVS

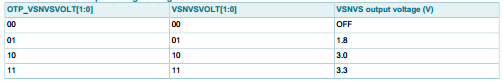

VSNVS 是一个 10 mA 的 LDO/switch,用于为处理器中的 RTC 域供电。VSNVS 在其输入源 VIN 正常的情况下可以在各种状态下保持其输出,包括系统开机、关机、复位等。它可以通过寄存器 OTP_VSNVSVOLT[1:0] 来配置其输出电压,具体配置如下表:

2.2 SW 1 & 2

2.2.1 BUCK 模式

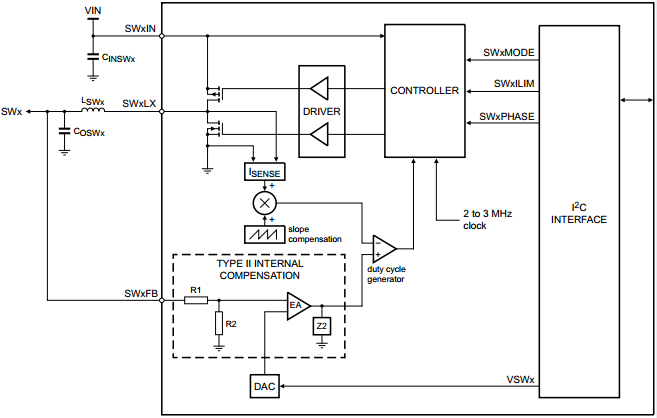

SW 1 & 2 是两个低压稳压器,输入电压为 2.5 V 到 5.5 V,输出电压为 0.4 V 到 1.8 V,电压调整步进为 6.25 mV。每个稳压器的输出为 2.5A。

其内部及应用框图如下图:

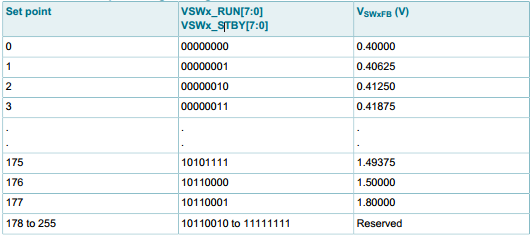

各稳压器分别通过寄存器 VSWx_RUN[7:0] 来设定其在“Run”模式下的输出电压,

通过 VSWx_STBY[7:0] 来设定其在“Standby”模式下的输出电压。如下图:

2.2.2 SW 1 & 2 双相模式

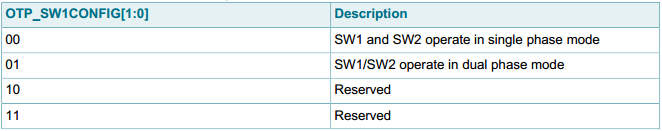

SW 1 & 2 可以配置成双相模式,在这种模式下,由 SW1 的寄存器控制输出电压和其他配置。同样,SW1FB 引脚成为产生的电压轨的主要反馈节点,但是两个 FB 引脚应该连接在一起。

寄存器 OTP_SW1CONFIG[1:0] 用来设定 SW1 & 2 的工作模式,如下图:

2.2.3 SW2 VTT 模式

SW2 提供了一个可选择的 VTT 模式来为 DDR 存储器创建 VTT 终端。当 SW2_VTTEN = 1 时,将启用 VTT 模式。在这种模式下,SW2 参考电压从内部通过一个 2 分频器连接到 SW1FB 输出。通过 OTP_VTT_PDOWN 控制其输出使能。

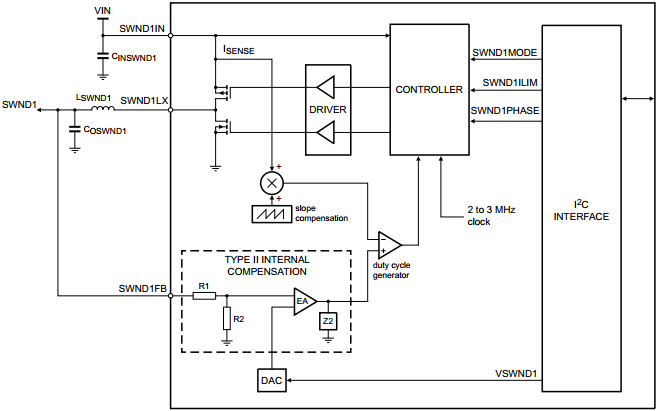

2.3 SWND1

SWND1 是一个低压降压稳压器,输入电压为 2.5 V 到 5.5 V,输出电压为 1.0 V 到 4.1 V,其内部及应用框图如下图:

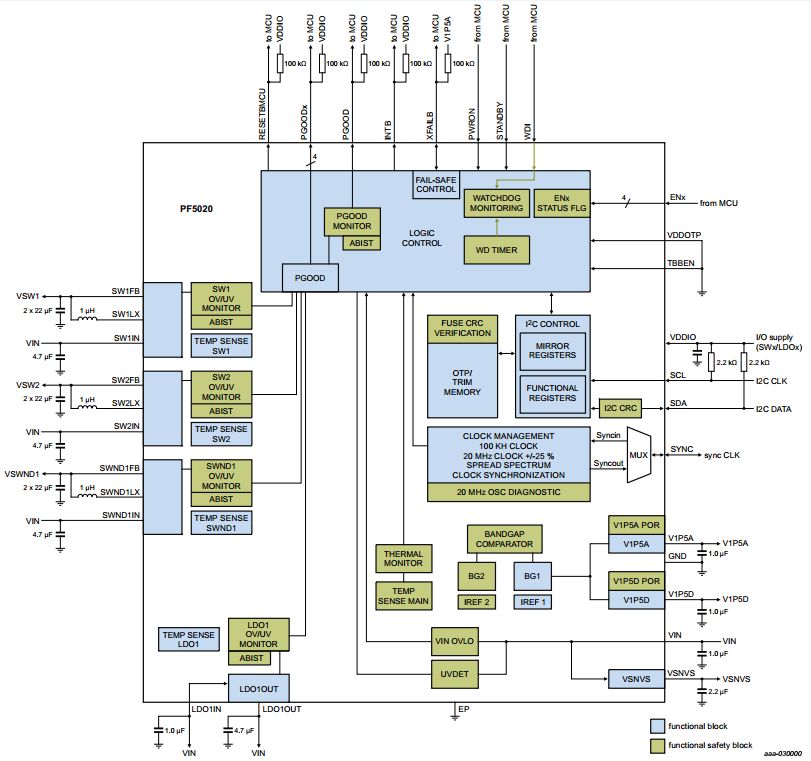

2.4 LDO1

LDO1 是一个低压差线性稳压器,其具有以下几个特点:

2.5 典型应用图

3. 硬件设计指南

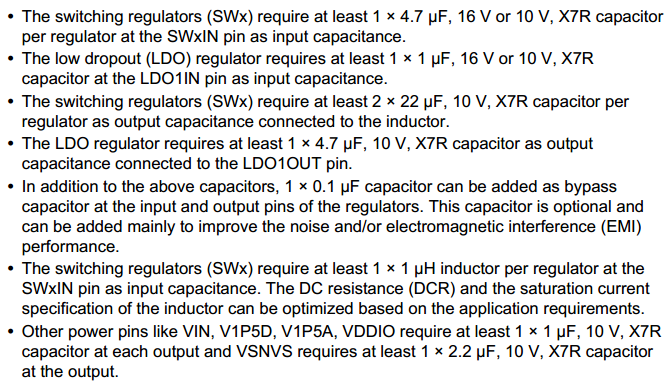

3.1 原理图 和 BOM 建议

3.2 PCB 叠层建议

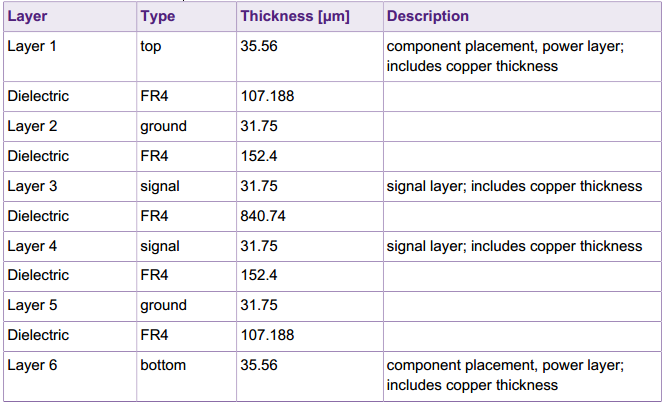

PF502x PMIC 是一种高功率密度 PMIC,具有多个 I/O 功能和信号。因此,布局必须根据功率和噪声灵敏度进行优化。推荐使用 6 层板设计(两层 GND 在中间),也可以根据实际情况改变层数,以下为 6 层板的堆栈参考:

3.3 PCB Layout 建议

- 所有与开关稳压器(SWx)相关的部件必须靠近稳压器,并尽量使用短而宽的导线连接引脚。

- 所有输入电容,包括旁路电容,尽量靠近芯片的 SWxIN 引脚和 GND 之间,保证输入电流路径中的寄生电感最小,以及电流回路更短。

- 所有的输出电容都必须放置在离集成电路不远的地方,同时也要放置在离负载最佳的位置。输出电容必须提供足够的散热通孔到 GND 层。

- SWxFB 引脚必须用细导线连接到输出电容附近,并且须通过内部信号层走线,以屏蔽外部噪声。在多相配置中,建议将所有反馈管脚连接在一起。

- 连接 SWxLX 引脚和输出电感器的线路是一个关键的功率线路,它必须尽可能的短和宽,以减少功率损耗。

- 对于多相配置,确保所有的建议在所有的调节器之间得到对称的遵循。

本期的《PF5020 硬件设计指南》到这里就结束了,值得注意的是:同 FS85 系列一样,PF5020 也支持 OTP 自定义烧录配置,且不同的是目前 PF5020 只有提供到“A0”版本,意味着目前它没有针对于特定应用的特定版本,这也符合了 PF502x 系列芯片的定位 – 轻量化、灵活搭配。可以配合自定义 OTP 配置输出灵活的搭配组合以满足各种系统电源的需求。

PF5020 的 OTP 制作及烧录方法与 FS85 系列相似,具体可以参考往期博文《FS85 OTP 文件设计指南》以及《FS85 OTP 文件烧录指南》,对应的工具可以前往 NXP PF5020 专区下载:

4. 参考资料

- PF5020 数据手册:《PF5020 - Power management integrated circuit (PMIC) for high performance applications (REV 1.0)》

- PF5020 设计指南:《AN12825 - PF502x device design guideline (REV 1)》

评论