一、概述

1.1低功耗概述

上次我们分享了 LPC54101 E-Lock 的软件框架设计,本次我们分享 LPC54101 E-Lock 低功耗软件配置。目前的穿戴式、手持式智能产品,在设计的时候都需要考虑低功耗,我们本次就探究一下 E-Lock 的低功耗设计。

前面的博文“LPC5101 E-Lock 硬件设计概要”中提到,E-Lock 的应用,静态电流需要达到 50uA 以内,我们就来看看如何能达到这个目标。

首先需要拿到芯片的数据参考手册,看到它在不同功耗时的数值,做一个简单的估计。比如工作多长时间,紧接着让哪些外设进入休眠的状态,休眠的时候让哪些外设去工作,什么条件唤醒,要把这些变为程序化的过程,把这个过程输到数学建模的模型中,这样就可以帮我们算出值,算出来之后我们就可以很明显的得到一个数值,也就是说我们使用这样一个电池去给应用供电大概可以使用多久,可以看到功耗是不是能够满足应用需求。

从工艺的角度来说,一般芯片的工艺越先进,动态功耗会越低,但是静态的漏电流会相对高一些。

低功耗芯片与不是低功耗的芯片,两者最大的区别是专门为低功耗设计的芯片它的低功耗模式一定会比没有为低功耗设计的芯片模式多很多种,它会考虑到各种可能性的低功耗组合,在这种组合下用更多的组合模式来达到更低的功耗。

1.2 查看芯片最小系统功耗

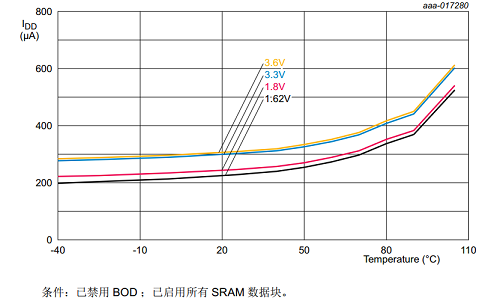

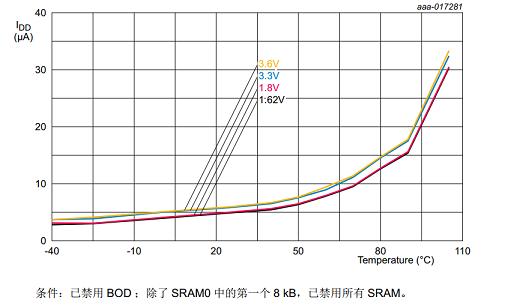

LPC54101 的 Datasheet 里面的静态特性和动态特性,详细描述了不同状态下 LPC54101 的功耗特性。

举个例子,其中静态特性的功耗数值,是在下列条件下测量工作、睡眠、深度睡眠和掉电模式的功耗:

(1) 在 IOCON 模块中禁用上拉电阻,将所有引脚配置为 GPIO。

(2) 使用 GPIO DIR 寄存器将 GPIO 引脚配置为输出。

(3) 向 GPIO CLR 寄存器写入 1,驱动输出至低电平。

(4) 禁用所有外设。

如图 1.1、图 1.2 所示,在不同的静态模式下,最小系统的电流 IDD 随着温度和电压的变化,可以看出,正常 3.3V 的状态下,深度睡眠模式的 IDD 在25 摄氏度时候大约在 300 uA,这个功耗确实远远超出 E-Lock 的目标范围,所以我们会采用掉电模式,在掉电模式下,同样 3.3V,25 摄氏度,最小系统的 IDD 在 10uA 左右,基本符合我们 E-Lock 的静态电流目标。

二、LPC54101 E-Lock 低功耗配置

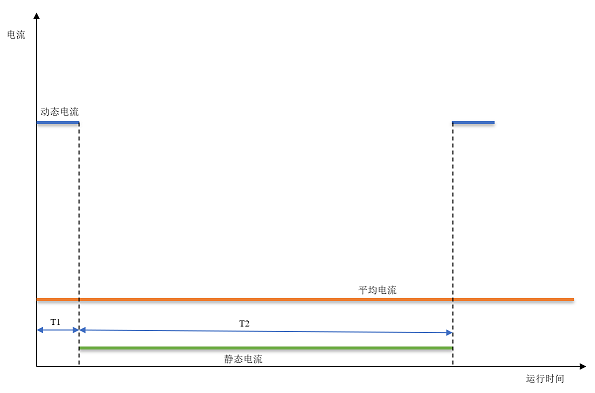

前面提到了 MCU 的静态模式和动态模式,那么对应的就是静态电流和动态电流,还有一个指标是平均电流,如图 2.1 所示,T1 代表 MCU 正常工作状态的动态电流时间,T2代表进入低功耗的静态电流时间,黄色的待变整个周期的平均电流。

2.1 LPC54101 低功耗模式

要配置 LPC54101 的低功耗,首先要看这款 MCU 都有哪些低功耗模式,LPC54101 支持多种电源控制功能。在工作模式下,当芯片运行时,可以对所选外设的电源和时钟进行优化,从而降低功耗。此外,处理器还有四种特殊的低功耗模式,可让不同外设分别运行在:睡眠模式、深度睡眠模式、掉电模式和深度掉电模式,并由功耗模式配置 API 激活。

(1) 睡眠模式

进入睡眠模式后,内核时钟以及任意未使用的外设上的时钟全都关闭。从睡眠模式唤醒不需要任何特殊的序列,只需要重新使能 ARM 内核时钟。

在睡眠模式下,暂停执行指令,直到发生复位或中断。睡眠模式下外设继续工作,且可能产生中断,导致处理器恢复执行状态。睡眠模式消除了处理器本身、存储器系统和相关控制器,以及内部总线和未使用外设的动态功耗。处理器的状态和寄存器、外设寄存器和内部SRAM 的值都会保留,引脚的逻辑电平保持静态。

(2) 深度睡眠模式

在深度睡眠模式中,所有外设时钟和所有时钟源都关闭,可以选择保持运行 32 kHz 时钟和 WDOSC。此外,所有模拟模块均关断, flash 处于待机模式。在深度睡眠模式下,应用可保持一些内部时钟和 BOD 电路在运行状态,以便自定时唤醒和 BOD 保护。

LPC5410x 可通过以下方式从深度睡眠模式唤醒:复位、选择用作引脚中断模块输入的数字引脚、 RTC 警报、 Micro-tick、看门狗定时器复位中断、 BOD 中断 / 复位或 USART 中断(如果 USART 配置为 32 kHz 模式或同步从机模式)、 SPI 或任意 I2C 外设。从深度睡眠模式唤醒时, SPI、 USART 和 I2C 外设必须配置为从机模式。从深度睡眠模式唤醒所采用的任何中断都必须使能一个 SYSCON 唤醒使能寄存器和NVIC。

在深度睡眠模式下,处理器的状态和寄存器、外设寄存器和内部 SRAM 的值都会保留,引脚的逻辑电平保持静态。深度睡眠模式支持极低的静态功率和快速唤醒选项。

(3) 掉电模式

在掉电模式中,所有外设时钟和所有时钟源都关闭,可以选择保持运行 32 kHz 时钟和 WDOSC。此外,所有模拟模块和 flash 均关断。在掉电模式下,应用可将 BOD 电路保持在运行状态,用于 BOD 保护。

LPC5410x 可通过以下方式从掉电模式唤醒:复位、选择用作引脚中断模块输入的数字引脚、 RTC 警报、 Micro-tick、看门狗定时器复位中断、 BOD 中断 / 复位或 USART 中断(如果 USART 处于 32 kHz 模式或配置为同步从机模式)、 SPI 或任意 I2C 外设。从掉电模式唤醒时, SPI、 USART 和 I2C 外设必须配置为从机模式。

在掉电模式中,处理器的状态和寄存器、外设寄存器和内部 SRAM 的值都会保留,引脚的逻辑电平保持静态。掉电模式比深度睡眠模式更能节省功耗,但唤醒时间较长。

(4) 深度掉电模式

在深度掉电模式下,整个芯片的电源关闭,但 RTC 电源域和 RESET 引脚除外。 LPC5410x可以通过 RESET 引脚和 RTC 警报从深度掉电模式唤醒。

2.2 低功耗模式选择

由于我们需要用触摸、指纹、防撬开关、初始化开关这些外部中断来唤醒 LPC54101,所以最省电的模式就是掉电模式,有的 MCU 也成为关断模式,对于图 2.1,如果我们需要得到的平均电流最小,那么分别需要对静态电流和动态电流进行优化。

(1) 静态功耗

传统静态功耗的定义是指系统时钟源关闭时数字电路的漏电流。但是在混合信号低功耗 MCU 的设计中要同时考虑下列多种漏电流来源,包含数字电路漏电流、SRAM 漏电流、待机时已关闭的仿真电路漏电流(例如 ADC,嵌入式闪存)、待机时不关闭的仿真电路工作电流(例如LDO、BOD)及 IO 引脚的漏电流。因为时钟源已关闭,影响静态功耗的主要参数为工艺、电压及温度。因此,降低静态功耗必须选择超低功耗工艺,但是低功耗工艺通常伴随较高的 Vt,导致低电压模拟外设设计困难。另外,以 MCU 待机电流 1 微安的规格,代表数字电路漏电 + RAM 保持电流 + LDO 工作电流 + BOD(掉电检测或重置电路)工作电流总和必须小于 1 微安,对于 Flash,RAM 越来越大及功能越来越多的低功耗 MCU 设计厂商而言,是十分艰巨的挑战。

(2) 动态功耗

我们把 E-Lock 的业务逻辑的模式变得模式化,也就是把它变成一个循环,如上一篇“LPC54101 E-Lock 软件框架设计”中使用状态机的软件框架,来对各个应用层软件的 Task 进行时间分配,比如哪个模块工作多长时间,紧接着让哪些外设进入休眠的状态,休眠的时候让哪些外设去工作,什么条件唤醒,要把这些变为程序化的过程,就实现了动态电流的最小化。

2.3 低功耗配置小结

总结一下,上面提到的方式就是包含低功耗应用中两个不同的阶段,一个是动态阶段,在规定的时间间隔,不管是 RTC 还是外部的事件、GPIO 中断等等,需要处理一些传感器收集过来的数据或者是无线传过来的数据;还有一个是静态阶段,这个时候系统是属于真正的低功耗状态,会等待各种唤醒源或者是中断来把它唤醒。低功耗设计就是要考虑这两个阶段,考虑的各种因素就是要从这两个阶段来进行考虑,在动态阶段,要求在给定的时间内能够执行一定数量的指令,所以有时候也不是说动态阶段频率越慢越好,要考虑性价比,在静态阶段,要保持最少的内容,比如数据要在 SRAM 里面保持,还要有一定的唤醒能力。两个阶段之间的转换要支持不同的约束条件,睡眠到运行的转换要求在转换时具有快速的唤醒时间,而且风驰电流是最小的,这样能够使用外部的电池来供电;从运行到睡眠的时候其实是不太关心转换时间的,但是需要关心的是要转换到最能够节约功耗的一个睡眠模式。

三、低功耗配置注意事项

3.1 LPC54101 的 ISP 引脚

ISP 功能大家都很熟悉,MCU 启动的时候,ISP 引脚拉低,代表进入 ISP 模式,我们在设计原理图的时候,一定要注意,这个引脚不能接到外设的上电低电平端,也就是说,外设假如是不熟悉的芯片,ISP 引脚接到这个芯片的引脚,恰巧上电为低电平,那么 MCU 始终进入不了正常的开机,这个需要尤其注意。

3.2 空引脚处理

表 3.1 显示如何端接未在应用中使用的引脚。在很多情况下,未使用的引脚需要通过外部连接,或者通过软件正确配置,以便最大程度降低器件的总功耗。

带 GPIO 功能的未使用引脚应配置为输出,将其设为低电平,且禁用它们的内部上拉电阻。如需将 GPIO 引脚配置为输出并驱动至低电平,可在 IOCON 寄存器中选择 GPIO 功能,选择 GPIO DIR 寄存器中的输出,然后针对该引脚将 0 写入 GPIO PORT 寄存器。在引脚的 IOCON 寄存器中禁用上拉电阻。

此外,建议将所有较小封装上未外焊的 GPIO 引脚配置为输出驱动至低电平,且禁用内部上拉电阻。

|

引脚

|

默认状态

|

空引脚的端接建议

|

|

复位

|

I ; PU

|

如果应用程序不使用 RESET 引脚,可将其保持未连接状态。

|

|

所有 PIOn_m (非开漏)

|

I ; PU

|

如果驱动至低电平且通过软件配置为 GPIO 输出和上拉禁用,则可以保持不连接状态。

|

|

PIOn_m (I2C 开漏)

|

IA

|

如果驱动至低电平且通过软件配置为 GPIO 输出,则可以保持不连接状态。

|

|

RTCXIN

|

-

|

连接至地面。接地时,禁用 RTC 振荡器。

|

|

RTCXOUT

|

-

|

可保持未连接状态。

|

|

VREFP

|

-

|

连接至 VDD。

|

|

VREFN

|

-

|

连接至 VSS。

|

|

VDDA

|

-

|

连接至 VDD。

|

|

VSSA

|

-

|

连接至 VSS。

|

3.3 如何唤醒

在唤醒过程里,我们要确认系统的脉搏,就是要总体来审查应用的工作方式,找到系统时钟最大的节拍,然后根据这个需求来确认芯片所需要使用的唤醒源。

除此之外,还要研究应用的需求,明白系统工作的模式,比如拿采样模式来说,需要先采样,然后进入低功耗休息状态,再采样,再进入低功耗休息状态,所以整个系统是类似于像一个状态机一样,以采样事件作为驱动来工作的,采样不仅是提供信息,也提供系统的脉搏,这类系统在采样的同时可能还会涉及串口要进行通信等问题,因为信息的本源是采样,所以还是要采样的周期本身决定信息的有效性,要明确系统对唤醒源和唤醒模式的需求,以便确定系统最基础的休眠方式。进一步来说,比如基础的休眠方式和所应用的场景需求确定了,就可以给出这个系统设计的一个初步评估结果,从而达到是否能够确定是这个芯片、确定适用系统设计的结果。

四、参考文献

(1) NXP 官网:www.nxp.com.cn

(2) LPC5410X Datasheet

(3) MFRC630 Datasheet

(4) https://www.21ic.com/app/mcu/201805/760805.htm

(5) https://zhuanlan.zhihu.com/p/85543578

(6) https://blog.csdn.net/jiangjunjie_2005/article/details/47272017

评论