上一节我们简单介绍了CMOS Sensor 成像原理,这一节我们主要介绍CMOS Sensor 的硬件设计方面的内容,常用的CMOS Sensor 从数据输出类型来分的话,有两种,DVP接口和MIPI接口;DVP总线PCLK极限大约在96M左右,而且走线长度不能过长,所有DVP最大速率最好控制在72M以下,故PCB layout会较好画,但是DVP接口在信号完整性方面受限制,速率也受限制。500W还可以勉强用DVP。MIPI接口比DVP的接口信号线少,由于是低压差分信号,产生的干扰小,抗干扰能力也强,800W及以上都采用MIPI接口。

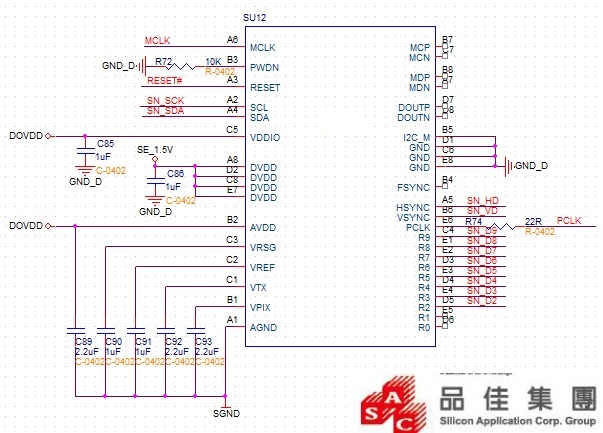

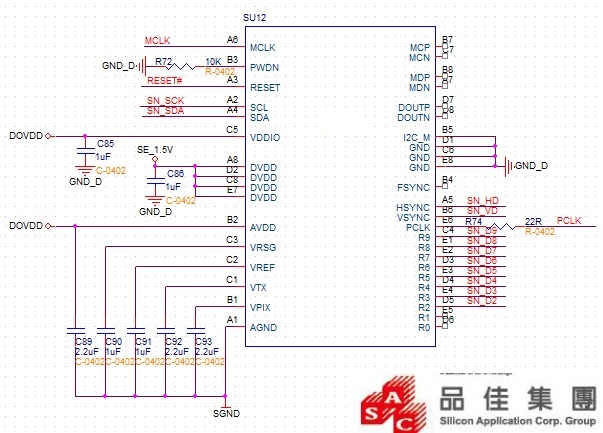

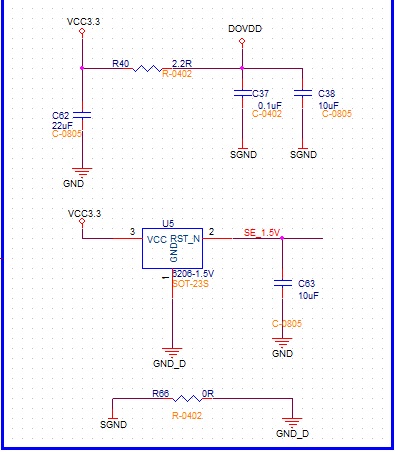

一、 DVP接口的Sensor通常需要PCLK、VSYNC、HSYNC、D[0:11],I2C以及复位信号和电源供电组成一个完整电路。如下图:

DVP接口类型的CMOS Sensor在电路上要注意电源的要求较高,不能有超过50mV的纹波输入,模拟地和数字地要分开连接。否则影像会有噪声干扰;I2C数据线于丹要上拉电平到VDDIO; 两个时钟信号都要经过RC电路后再接入到芯片。布线时要包地且不要和数据线并行和靠近敏感器件;

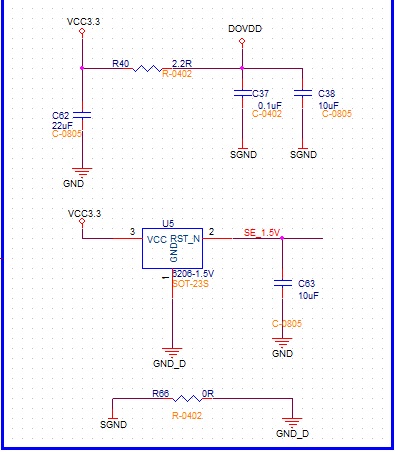

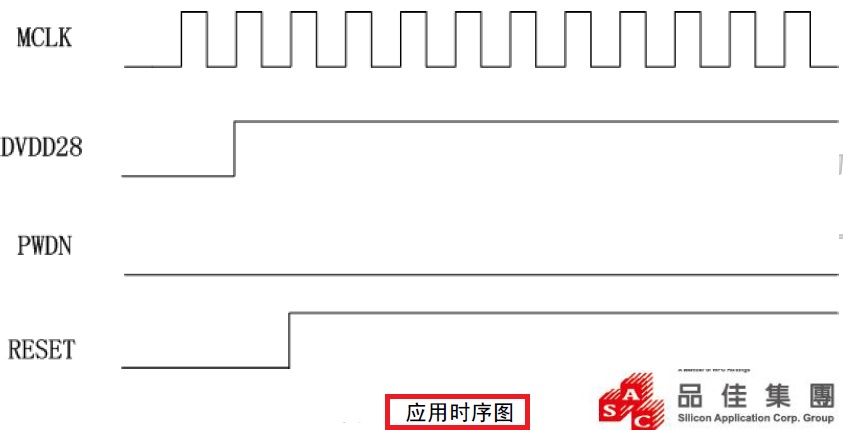

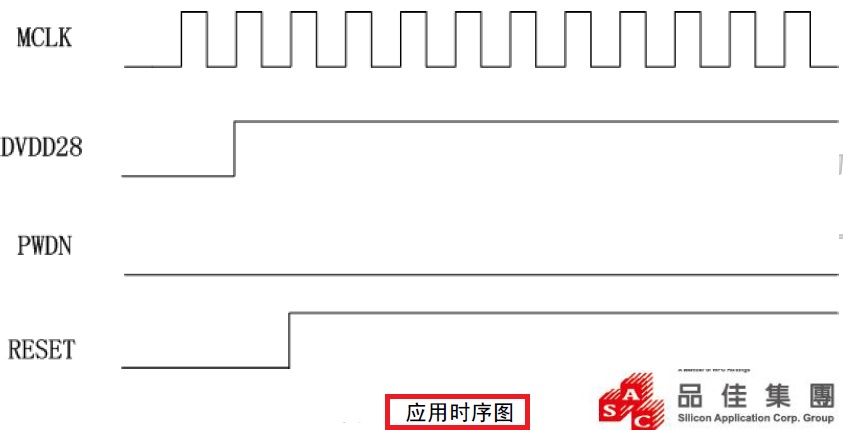

二、时序电路的应用设计:

1) PWDN 与RESET 均是异步设计,生效时不需要MCLK pin 有时钟提供。

2) PWDN 高有效,Low -> 正常工作,High -> 省电模式RESET 低有效,Low -> reset 芯片,High -> 正常工作

3) 主时钟必须在 sensor two-wire serial interface 读写前提供。

一、 DVP接口的Sensor通常需要PCLK、VSYNC、HSYNC、D[0:11],I2C以及复位信号和电源供电组成一个完整电路。如下图:

DVP接口类型的CMOS Sensor在电路上要注意电源的要求较高,不能有超过50mV的纹波输入,模拟地和数字地要分开连接。否则影像会有噪声干扰;I2C数据线于丹要上拉电平到VDDIO; 两个时钟信号都要经过RC电路后再接入到芯片。布线时要包地且不要和数据线并行和靠近敏感器件;

二、时序电路的应用设计:

1) PWDN 与RESET 均是异步设计,生效时不需要MCLK pin 有时钟提供。

2) PWDN 高有效,Low -> 正常工作,High -> 省电模式RESET 低有效,Low -> reset 芯片,High -> 正常工作

3) 主时钟必须在 sensor two-wire serial interface 读写前提供。

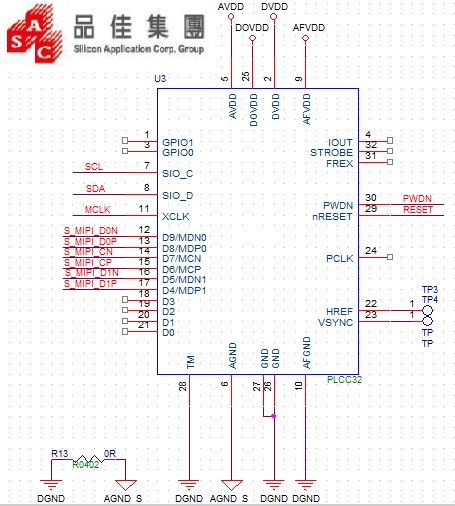

三、MIPI接口的电源部分和DVP没有太大差别,注意电源分开供电及电源稳定性,MIPI接口的CMOS Sensor采用差分线方式来传输数据和控制指令,所谓差分方式传输,就是发送端在两条信号线上传输的幅值是相等的,相位是相反的电信号。通常需要一对时钟差分对和1到4组数据差分对来完成图像的数据和控制命令的传输。以及芯片的控制信号(复位和休眠控制,地址选择等),如下图:

四、MIPI的差分对布线需要等长等距,等长是为了保证两个差分信号时刻保持相反极性,减少共模分量;等距则主要是为了保证两者差分阻抗一致,减少反射。“尽量靠近原则”有时候也是差分走线的要求之一。

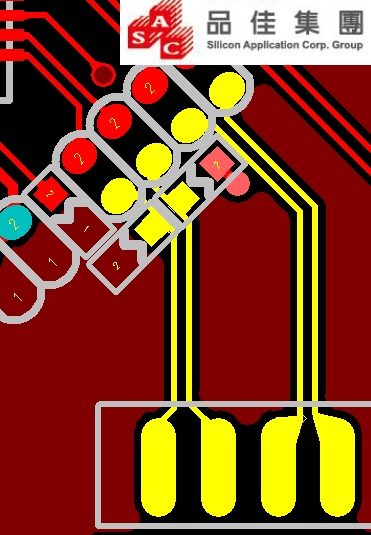

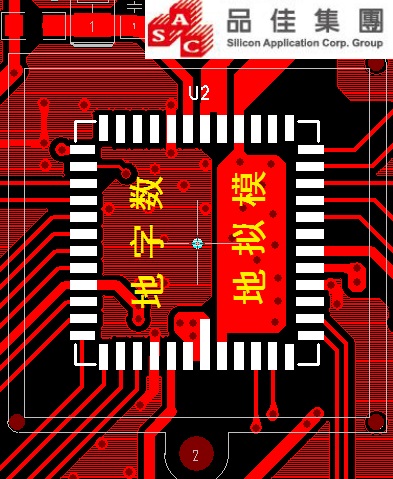

五、CMOS Sensor 是PLCC封装的布线请参考下图,数字地和模拟地尽量大面积的铺铜,这样的好处是减小串扰,并能给芯片散热。

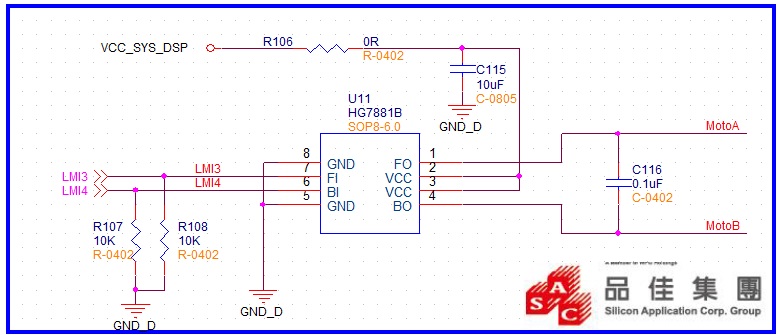

六、有的CMOS Sensor芯片还要应用到电子快门功能,电路设计如下:

到此,CMOS Sensor的硬件设计介绍完成,下一节,将介绍CMOS Sensor的调试。

评论