- 1.概述

- 2.硬件连接框图

- 3.MCU 端信号连接

- 4.FPGA 端信号连接

- 5.RT1020 SDRAM 地址分配

- 6.RT1020 SDRAM 接口配置数据存放位置

- 7.RT1020 SDRAM 接口 DCD(Device Configuration Data) 生成

- 概述

在伺服驱动系统中需要比较高的 PWM 分辨率和高带宽的电流环,FPGA 用于处理电流环用的时间比用 MCU 计算少很多,在多轴方案中,用 FPGA 处理电流环,

在 MCU 中处理速度环和位置环,会有比较大的优势,同时 MCU 和 FPGA 之间的通信应该尽可能的快,本文讲述 RT1020 MCU 与 Lattice FPGA 的 ECP5 进行通信的设置过程。

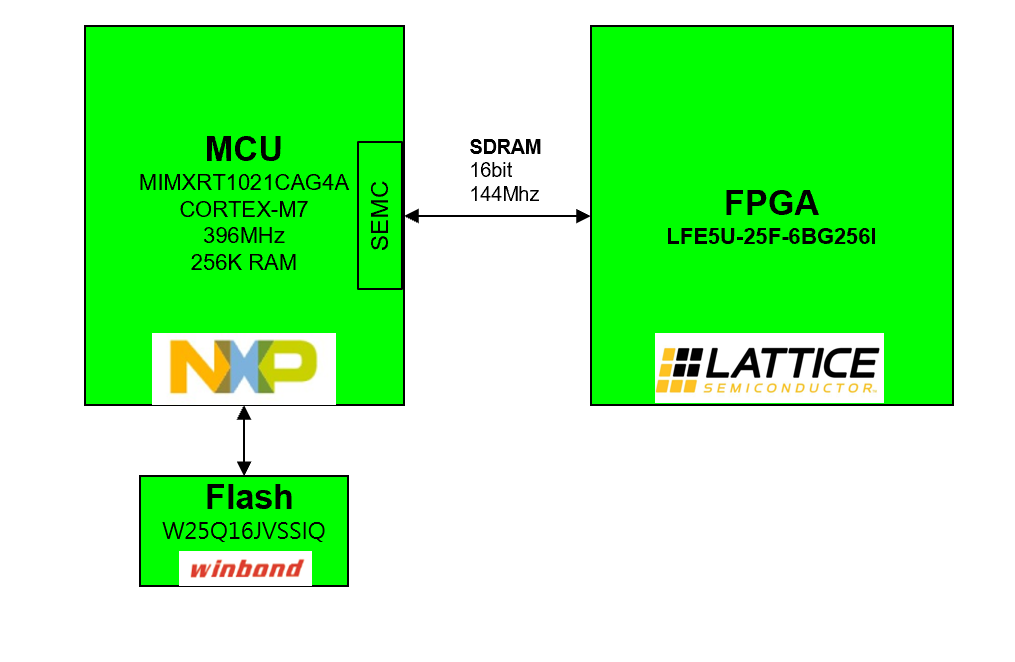

- 硬件连接框图

通过配置 RT1020 的 SEMC 外设为 SDRAM 模式,与 FPGA 进行通信,支持 8BIT 或 16BIT总线,运行最高频率为 166MHZ。

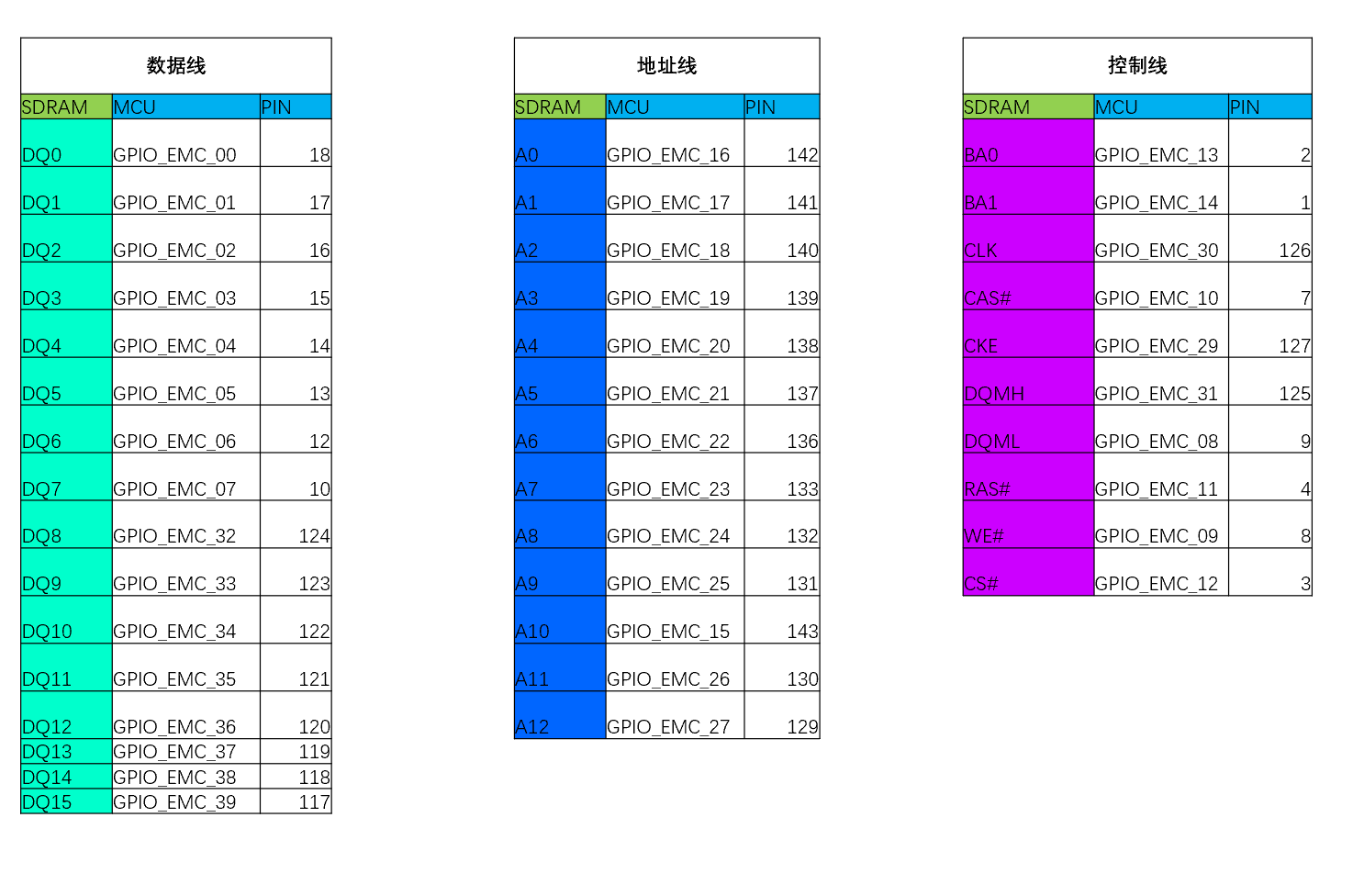

- MCU 端信号连接

MCU 端 SDRAM 接口信号对应的 MCU PIN 名称和引脚号。

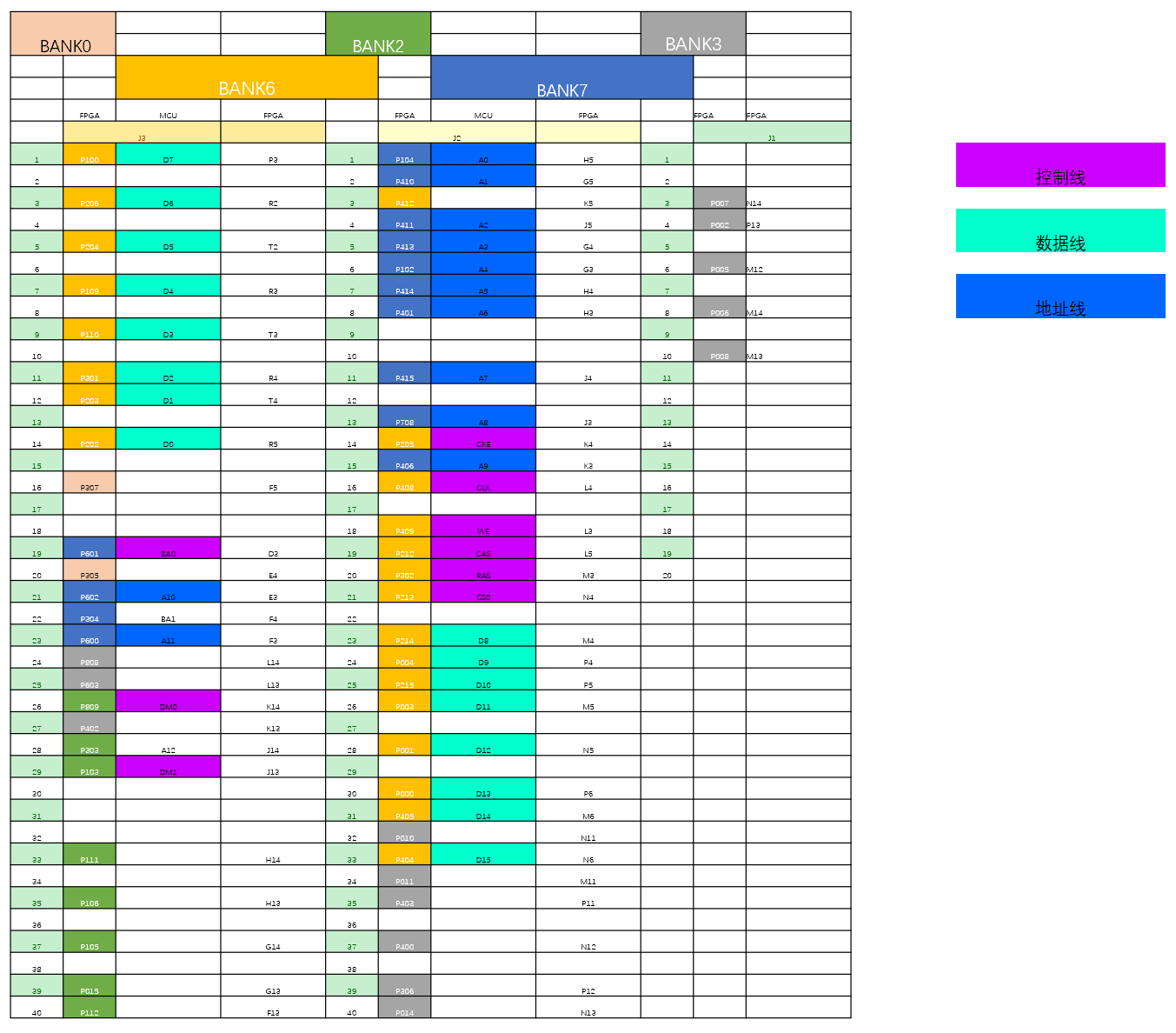

- FPGA 端信号连接

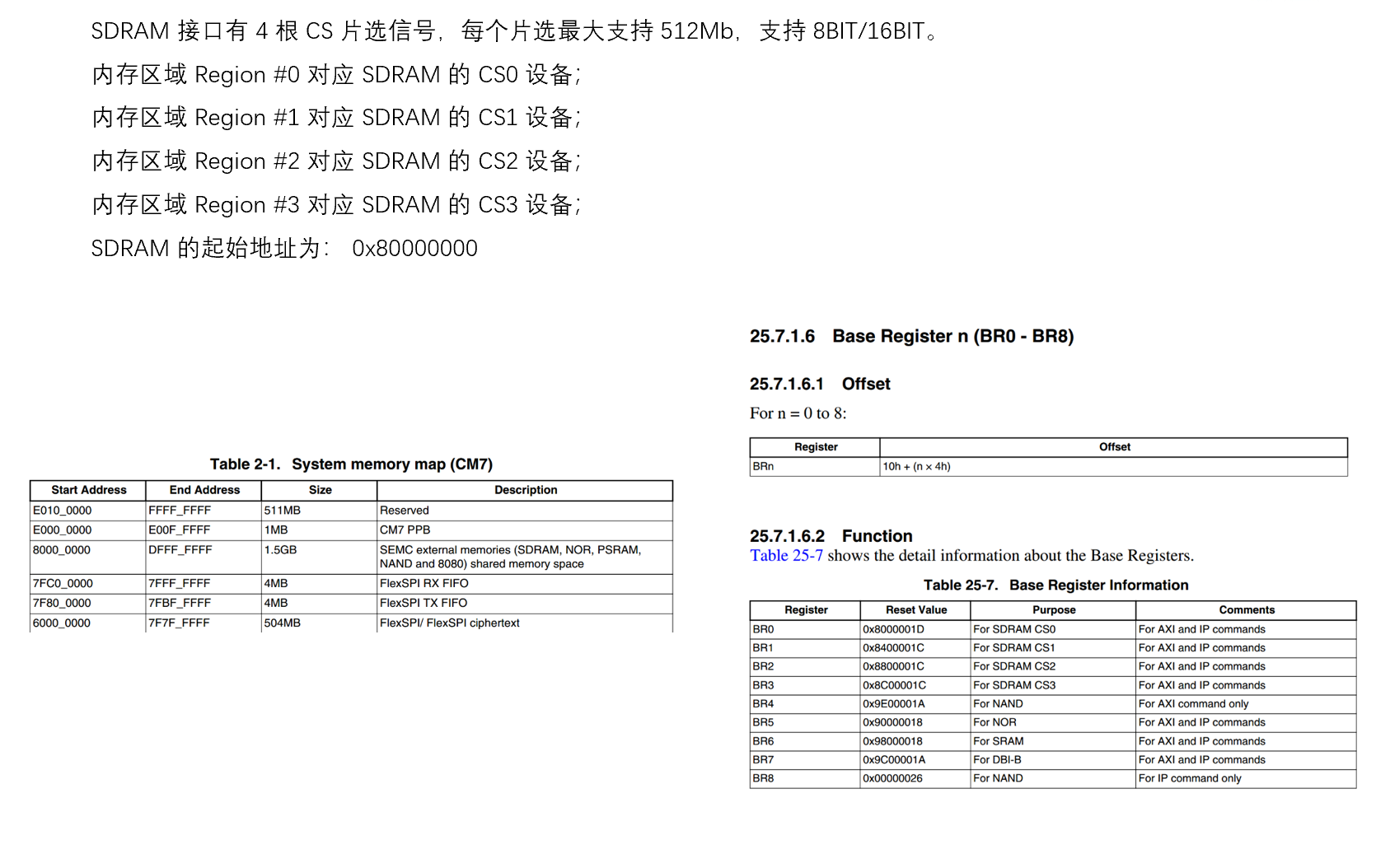

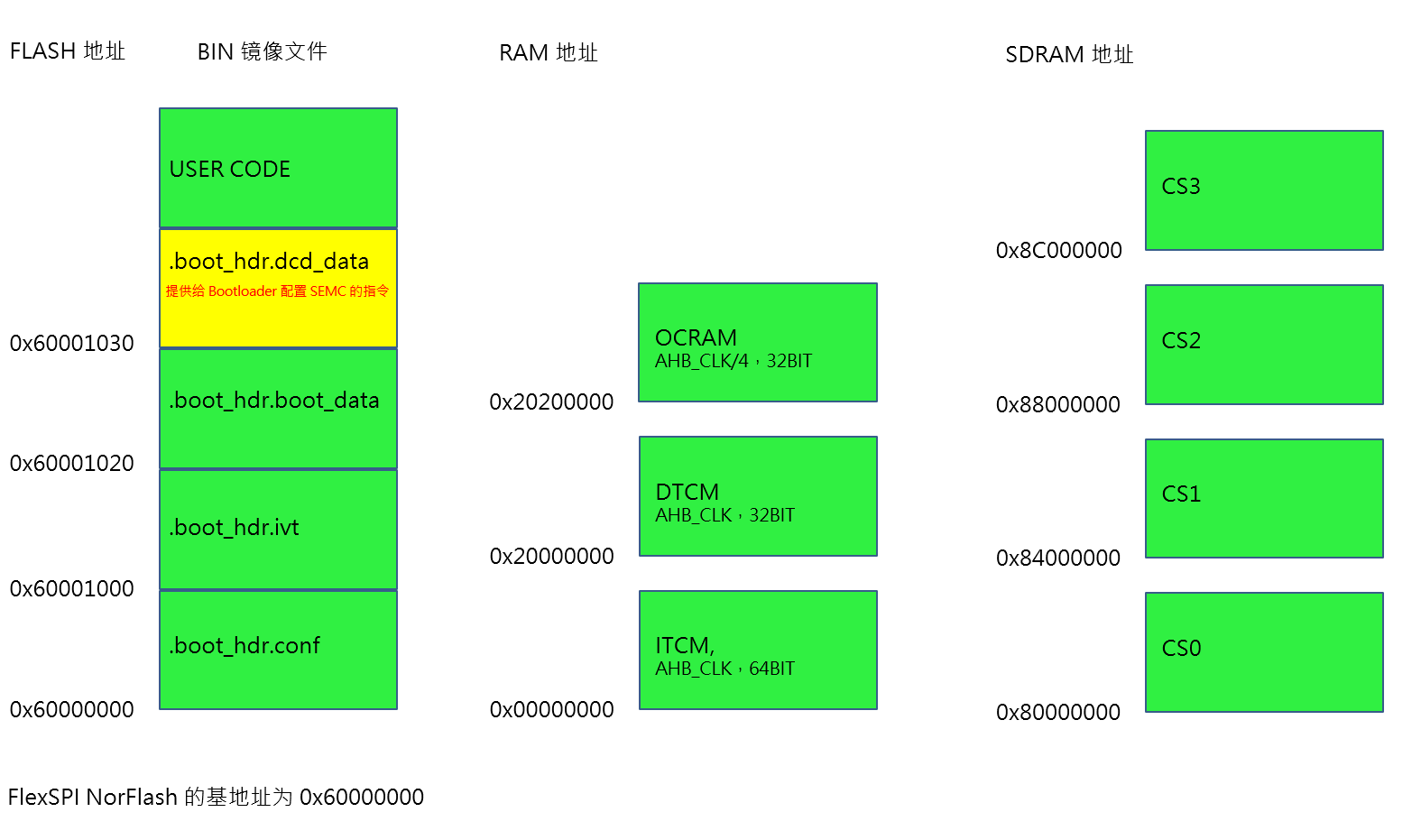

- RT1020 SDRAM 地址分配

SDRAM 接口有 4 根 CS 片选信号,每个片选最大支持 512Mb,支持 8BIT/16BIT。

内存区域 Region #0 对应 SDRAM 的 CS0 设备;

内存区域 Region #1 对应 SDRAM 的 CS1 设备;

内存区域 Region #2 对应 SDRAM 的 CS2 设备;

内存区域 Region #3 对应 SDRAM 的 CS3 设备;

SDRAM 的起始地址为: 0x80000000

- RT1020 SDRAM 接口配置数据存放位置

RT1020 在启动时,Bootloader 读取节区 .boot_hdr.dcd_data 的数据对 SDRAM 接口进行初始化,比如初始化 GPIO 口、SDRAM 时序参数、基地址。此节区地址在链接文件中指定。

- 7. RT1020 SDRAM 接口 DCD(Device Configuration Data) 生成

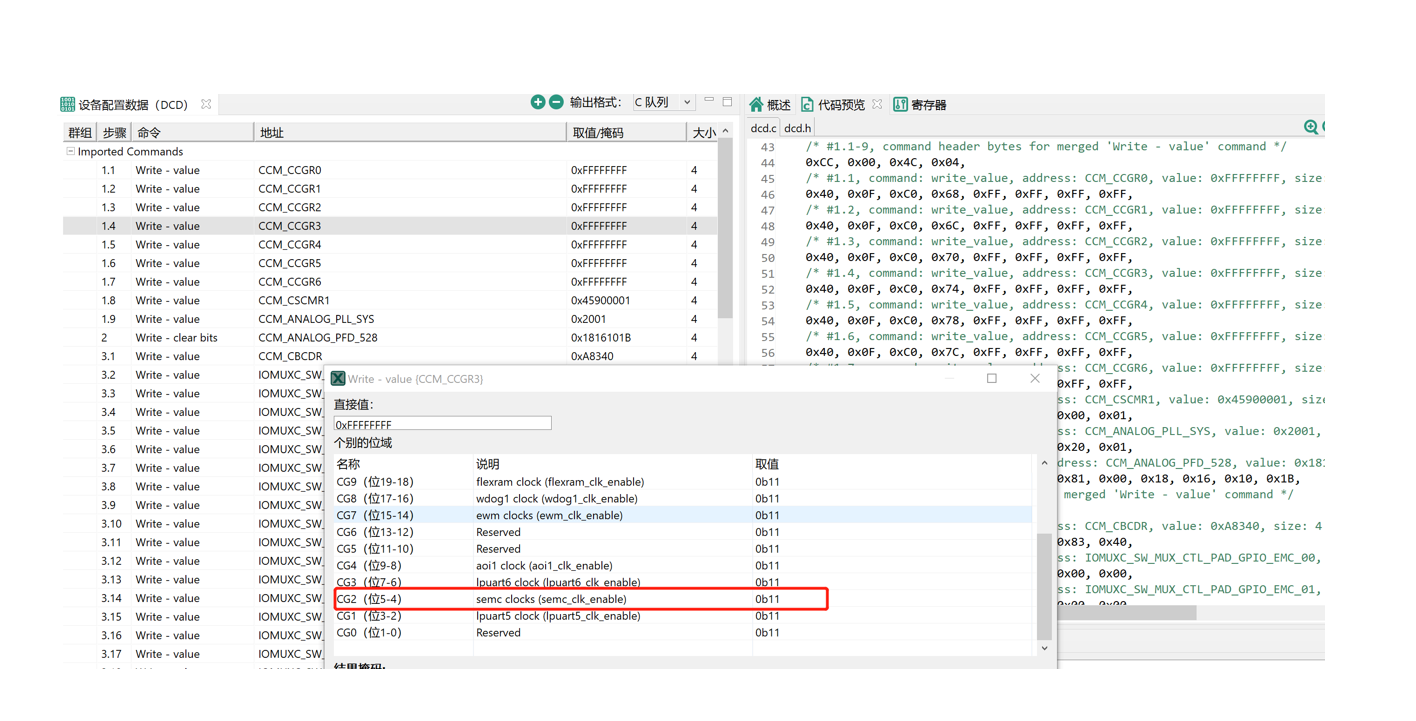

7.1 SEMC 外设时钟使能

节区 .boot_hdr.dcd_data 中的 DCD 数据可以用 MCUXpresso Config Tools 生成, DCD 指令格式参见参考手册的 Chapter 9 System Boot DCD 章节,

MCUXpresso Config Tools 可以图形化配置 DCD 指令,

通过其菜单栏的 工具 -> 设备配置 打开配置界面,SEMC 的时钟使能由 CCM_CCGR3 的第 4、5 位控制,使能 PLL2 和 PFD 分频器。

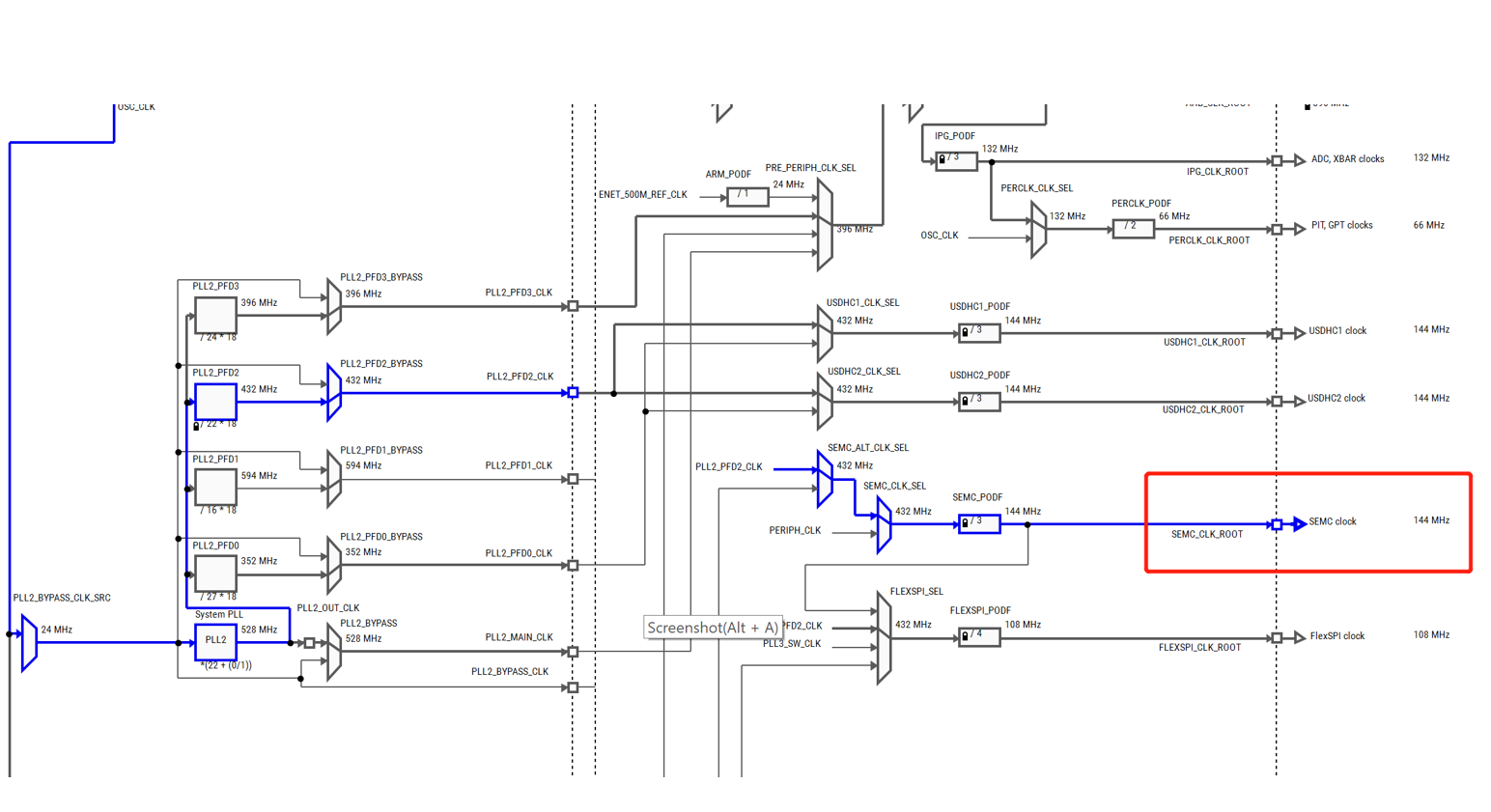

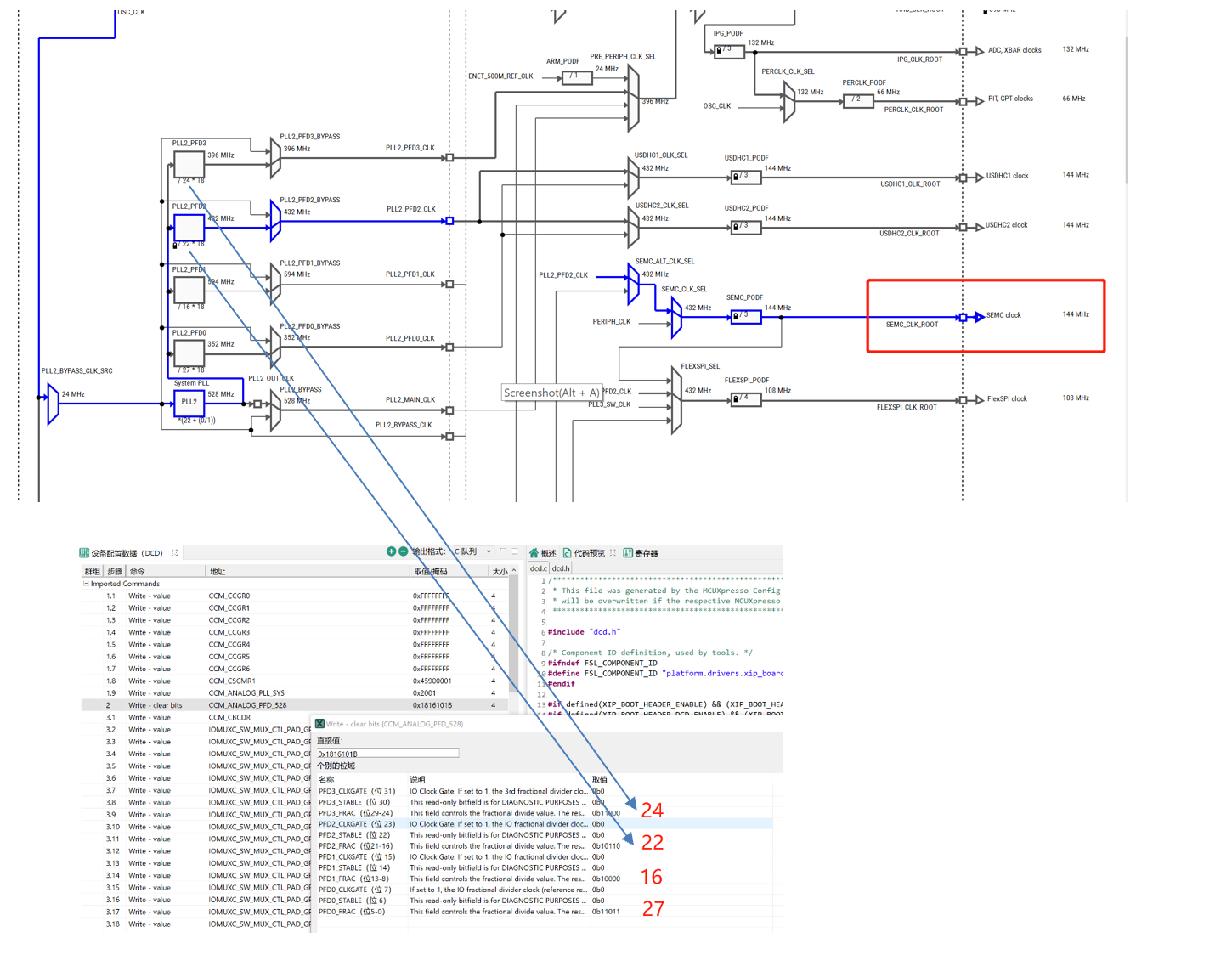

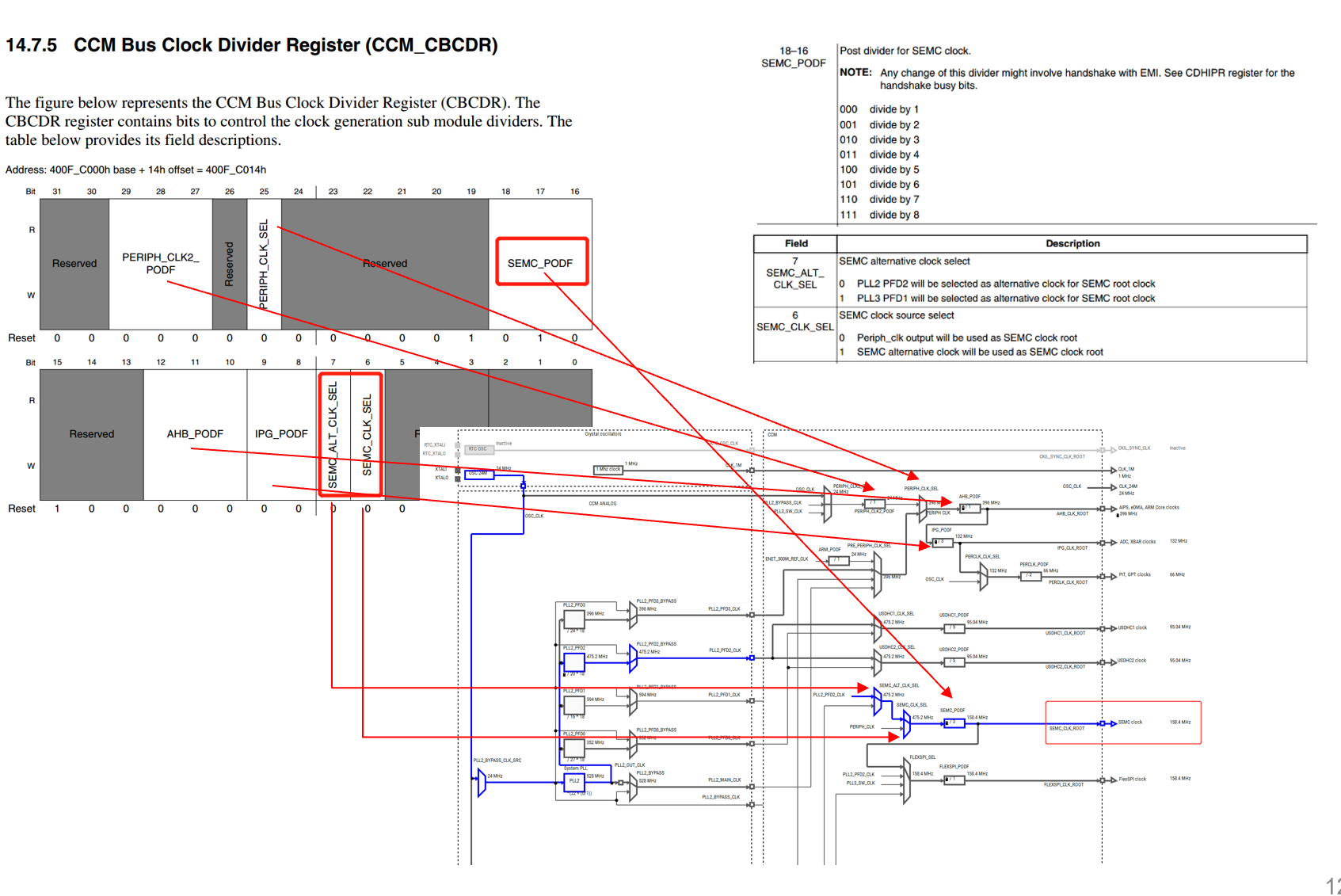

7.2 SEMC CLK 时钟配置

工业级 RT1020 的 SEMC 最大能工作于 166MHz,SEMC 的 CLK 信号配置为 144MHz,在时钟树中的配置图如下:

根据时钟树配置 PLL2 和其 PFD3、PFD2、PFD1、PFD0 分频器的值,由 CCM_ANALOG_PFD_528 寄存器配置,

对应关系如下图:

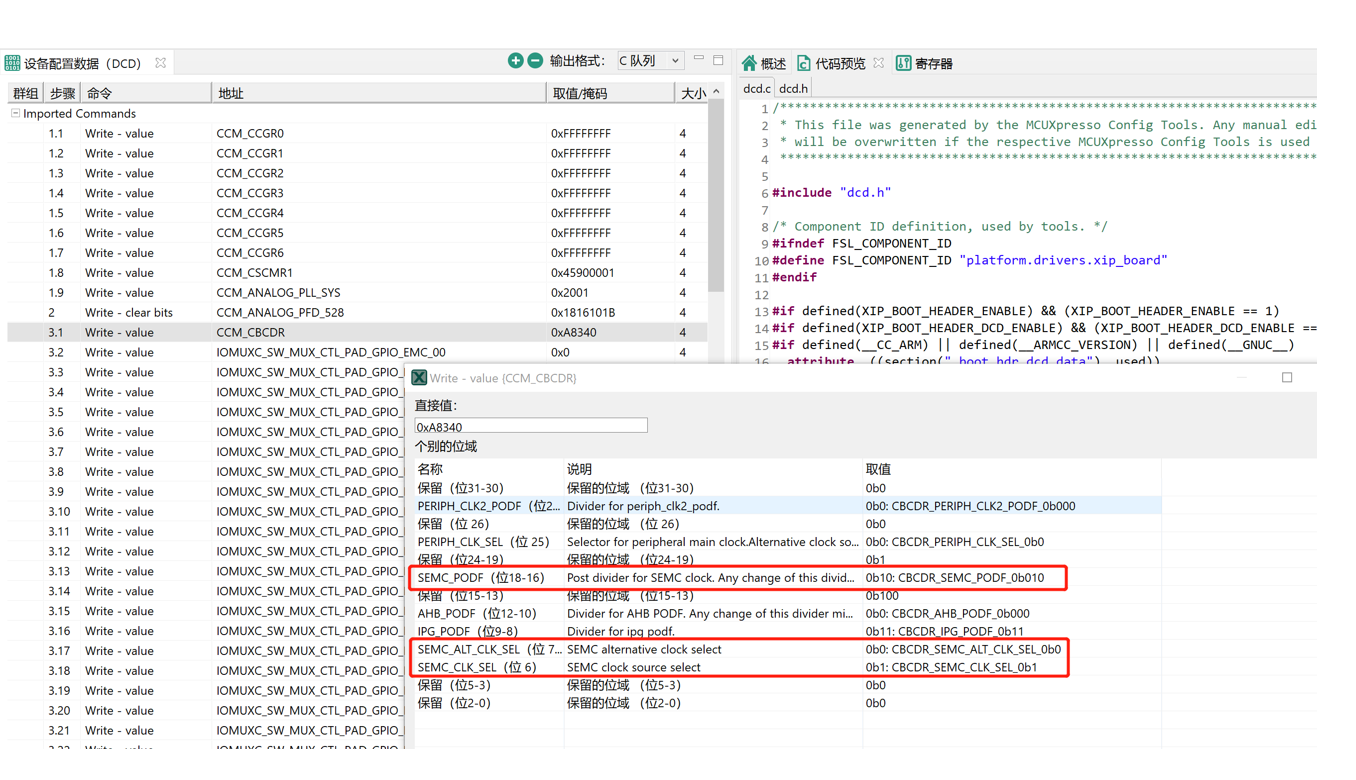

CCM_CBCDR 控制 SEMC CLK 的时钟源和分频值,

SEMC_ALT_CLK_SEL、SEMC_CLK_SEL、SEMC_PODF 在参考手册的描述和在时钟树的关系如下图:

在 MCUXpresso Config Tools 中的配置。

7.3 GPIO 口复用配置

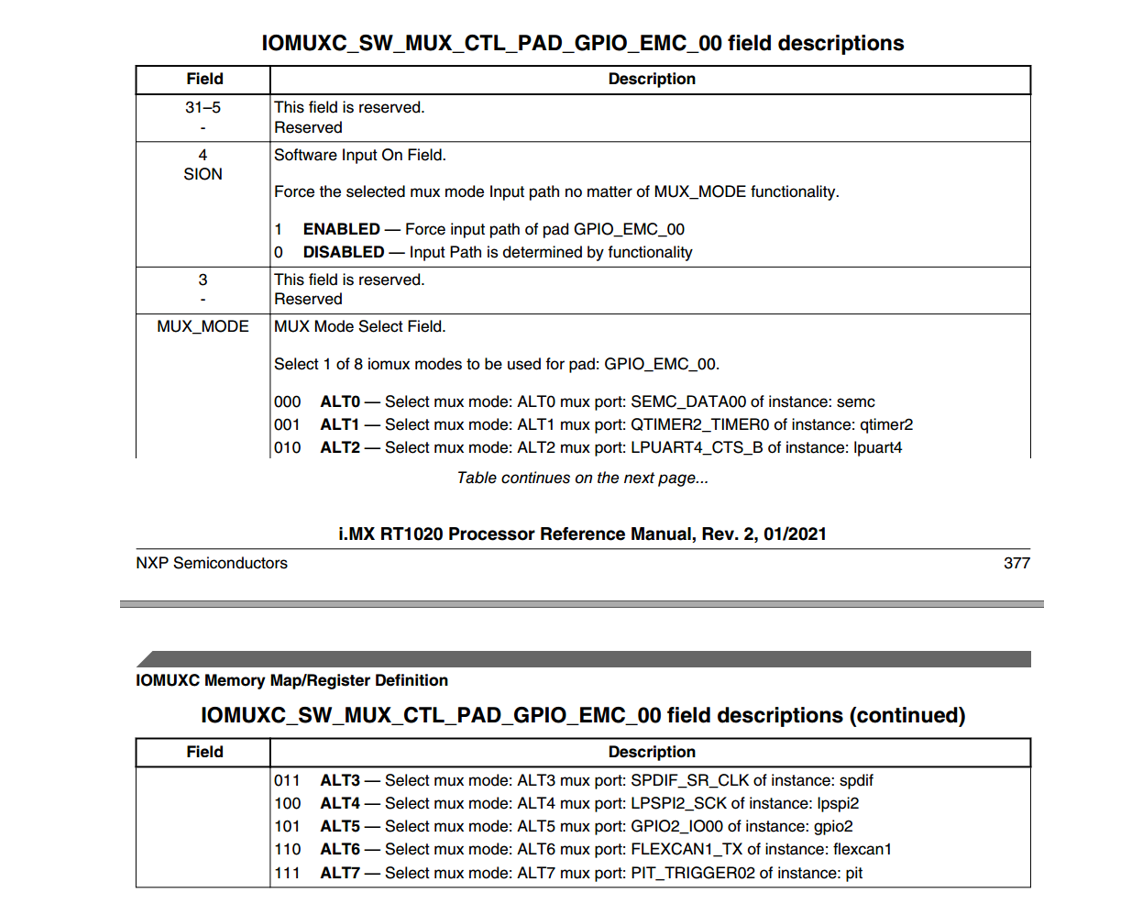

将 GPIO 口复用配置为 ALT0,即连接至 SEMC 外设,通过配置 IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_XX 寄存器完成。

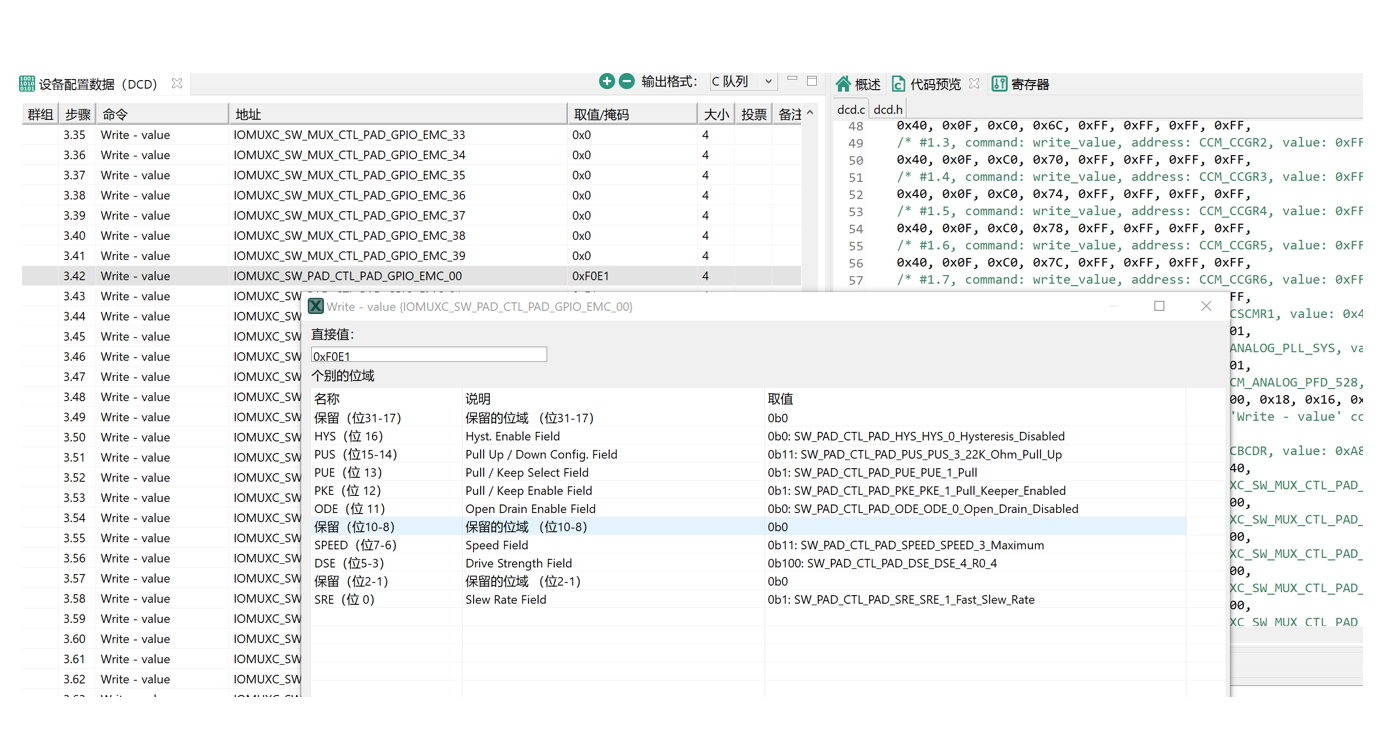

7.4 GPIO 口参数配置

GPIO 口配置为上拉、上拉阻值22K、开漏 Opendrain 禁用、速度 150-200MHZ、

滞回 Hysteresis 禁用、压摆率 Slew rate 最大、驱动能力 DSE 选 R0/4 (用于阻抗匹配和信号完整性)。

其中 DQS 不设置为 LoopBack,即 IOMUXC_SW_MUX_CTL_PAD_GPIO_EMC_28[4] = 0。 开发板是设置为 LoopBack 的。

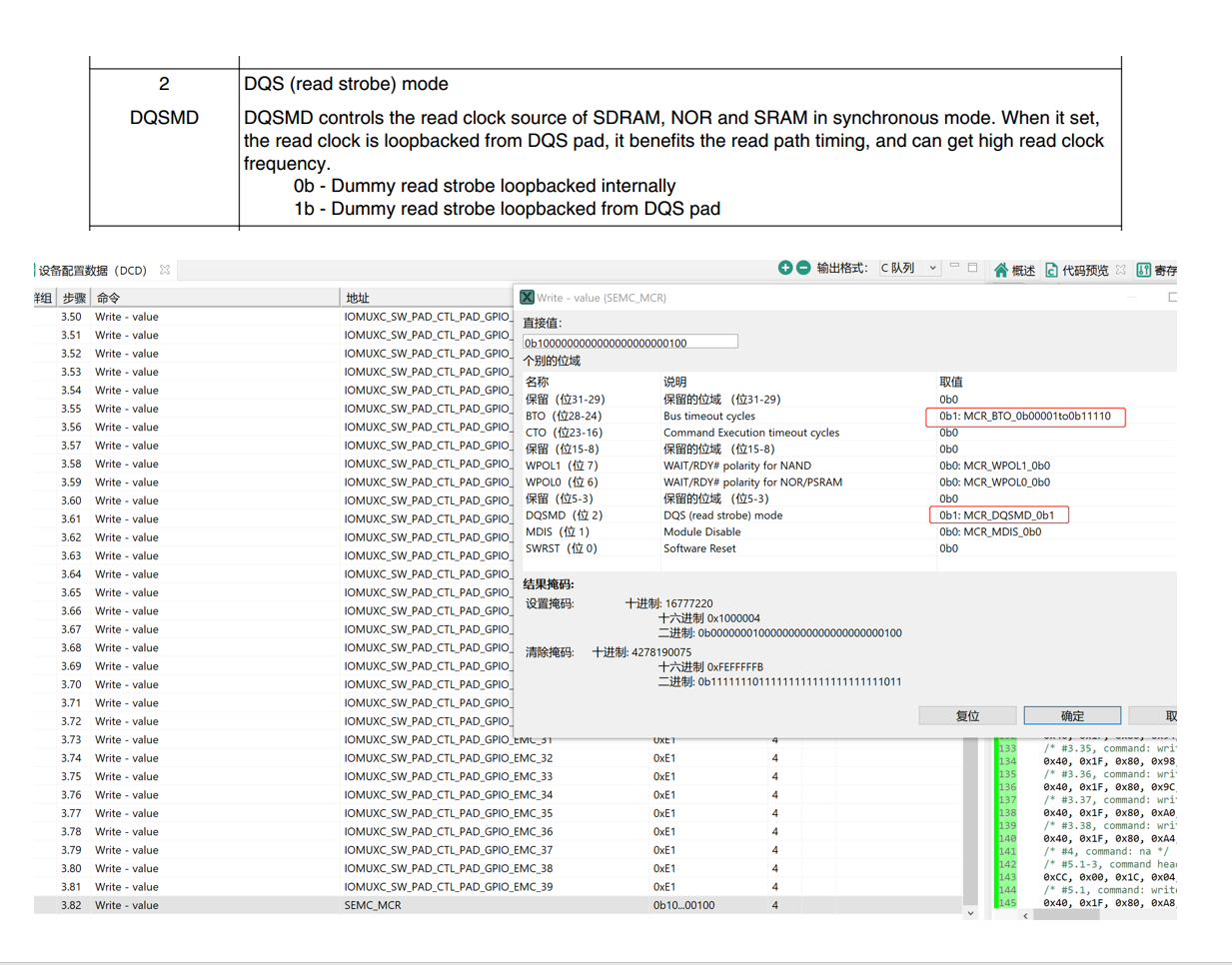

7.5 SEMC_MCR 寄存器参数配置

配置总线超时周期和 DQS 读锁存模式,超时时间计算公式:255*2^BTO,

DQS 通过外部 Pad 引脚信号来锁存。

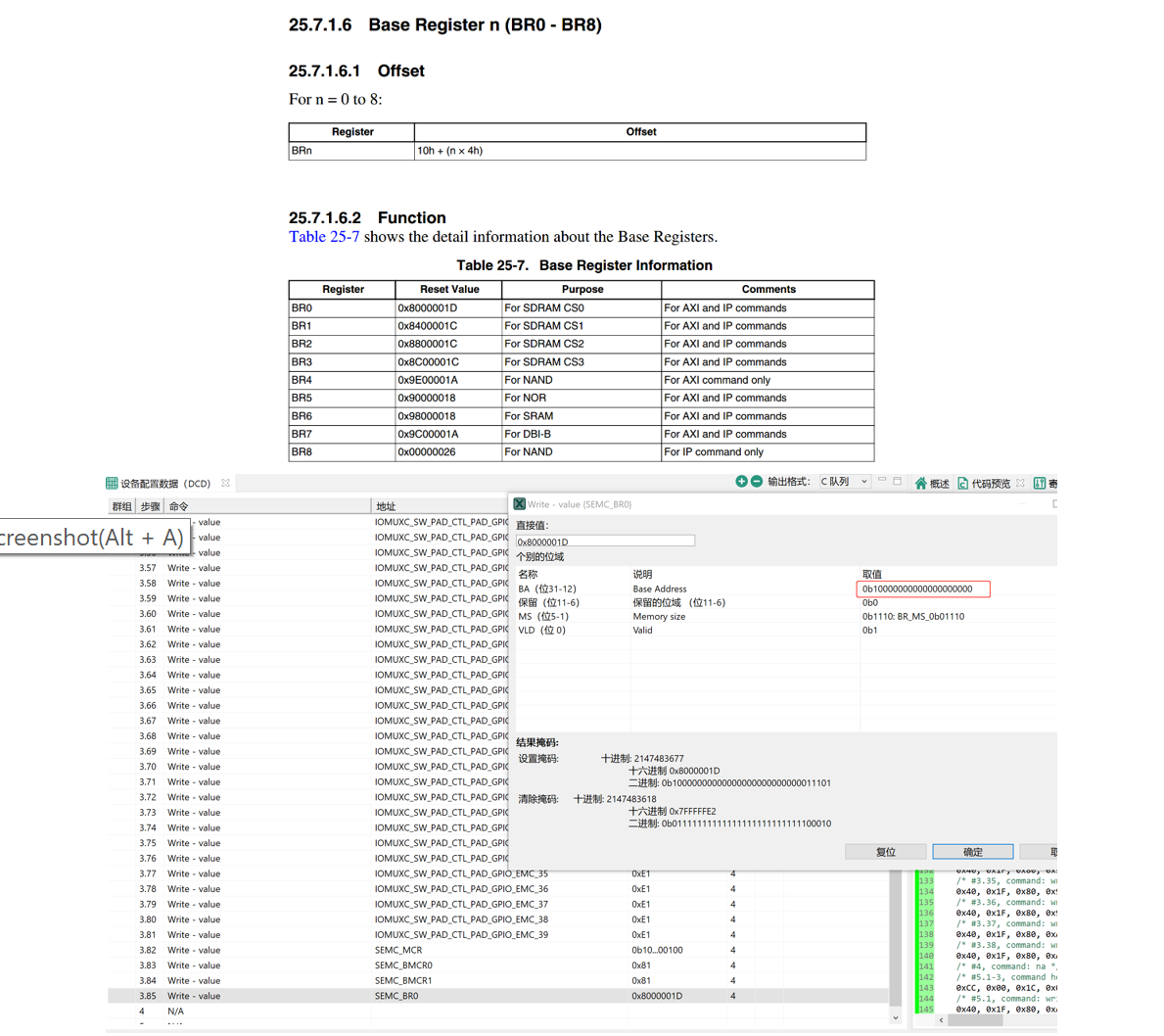

7.6 SEMC 基地址配置

SEMC 使用 CS0 进行片选,默认基地址为 0x80000000,可以通过设置 SEMC_BR0 寄存器进行初始化,并配置为 32MB,即 MS 位为 0x1101,如果是 64MB,则为0x1110。

参考手册的描述和配置如下图:

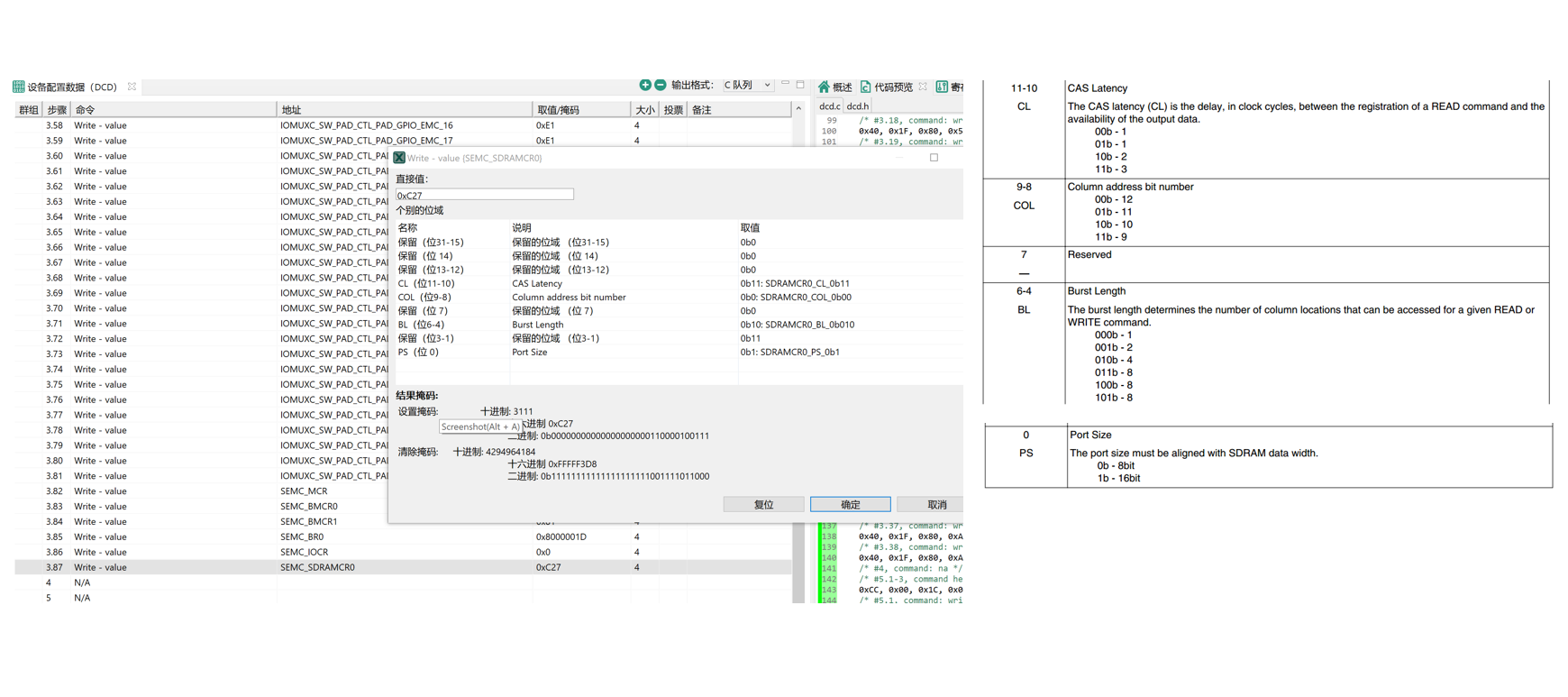

7.7 SEMC 时序配置

SDRAM 的 CL、COL、BL、Port Size 由 SEMC_SDRAMCR0 配置,

CL = 0,即 CAL Latency 为 1 个 CLOCK。

COL = 0 ,即 Column address bit number 为 12BIT。

BL =011b,即 Burst Length 为 8 字节,FPGA 中可连续读的寄存器地址为 6 个。

PS = 01b,接口位数 Port Size 为16位。

SEMC_SDRAMCR1、 SEMC_SDRAMCR2、 SEMC_SDRAMCR3 大部分为自刷新的配置,

在此关闭自刷新。

7.8 使用 IP 命令初始化 SDRAM 芯片

可以在 DCD 中生成 IP 指令,通过 IP 指令初始化外设,

比如给 SDRAM 发送预充指令,现在是 FPGA,不是实际的 SDRAM,不用执行预充指令。

IP 总线上的任何命令将用于 SEMC_IPCR0 设置的地址:0x80000000

配置完成后,使用 MCUXpresso Config Tools 的导出功能导出设备配置文件,拷到程序中替换 DCD.C 和 DCD.h

评论