介绍

包括多个数据位和时钟的源同步接口已经成为电子系统中移动图像数据的常用方法。

一个通用的标准是7:1 LVDS接口(用于通道连接,扁平电缆连接和摄像机连接),这已成为许多电子产品(包括消费电子设备、工业控制、医疗和汽车远程信息处理)中的通用标准。

在许多此类应用中,使用低成本 FPGA 进行图像处理的做法已变得相当普遍。特别是,LatticeXP2™,LatticeECP2™,LatticeECP2M™ 和LatticeECP3™ 非常适合支持7:1 LVDS标准。

本文档描述了实现 7:1 LVDS 接口的要求以及在此类接口中使用这些 FPGA 的优势。此外,这些设备中对 7:1 LVDS 接口的支持也证明了所有其他 LVDS 源同步要求的硬件实现的可行性。

本文档的讨论包括两种设计。第一个设计是一个简单的环回测试,它说明了7:1发送器和7:1接收器的使用。第二个设计就是通过 7:1 接收器将视频数据带入 FPGA 设备、处理和通过 7:1 发送器传输出去的示例。这两种设计都使用 Lattice 7:1 LVDS 视频演示套件进行了验证。

7:1 LVDS 接口要求

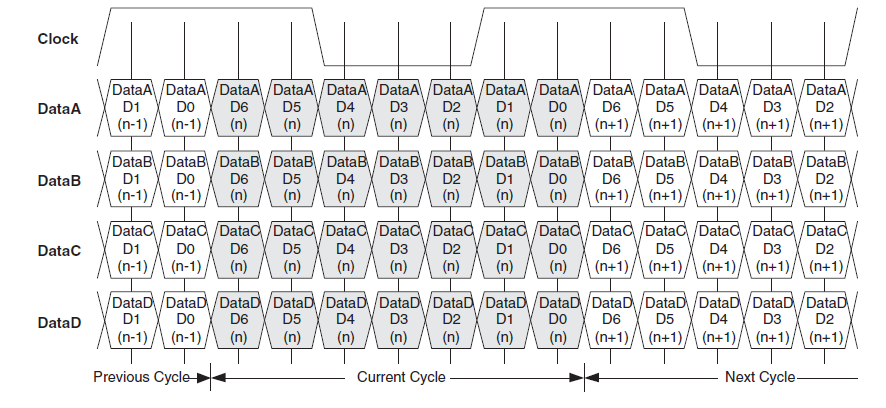

7:1 LVDS 接口是一个源同步 LVDS 接口。如图 1 所示,在低速时钟的每个周期中,七个数据位被串行化。通常,接口由四个(三个数据,一个时钟)或五个(四个数据,一个时钟)LVDS 对组成。

这四对转换为 21 个并行数据位,5 对转换为 28 个并行数据位。注意,在时钟上升边缘和字边界之间有一个 2 位偏移量。每个字有 7 位长。

图1 7:1 LVDS 接口的基本时序

每个通道包括一个串行 LVDS 数据对和一个源同步 LVDS 时钟对。接收端接收这个串行 LVDS数据,对其进行反序列化,并将其对齐到原始的字边界,以生成 7 个并行的 LVTTL 数据位。

7:1 发送器将 7 个 LVTTL 并行数据位序列化为一个 LVDS 数据位,并将这个串行数据通道与 LVDS 时钟一起传输。

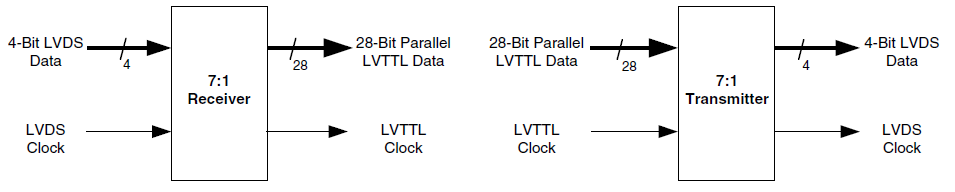

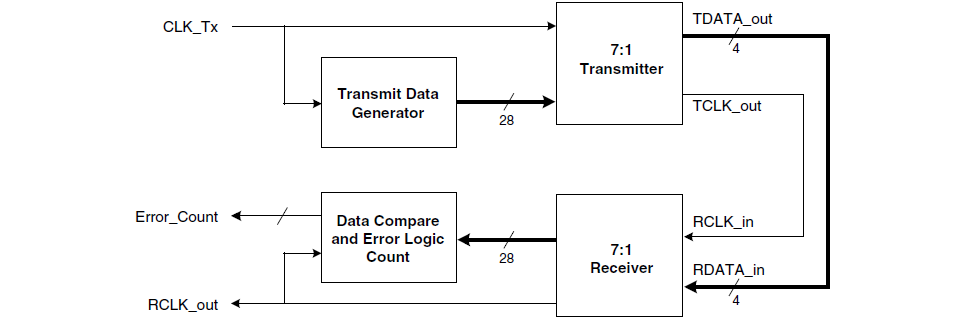

图 2 显示 7:1 接收器接收四个 LVDS 数据通道。当反序列化时,它生成 28 位宽的并行数据。同样,7:1 发送器序列化 28 位并行数据,生成 4 个 LVDS 数据通道。

图2 7:1 接收器和发送器功能

基于 FPGA 的通道连接和扁平电缆连接样式接口解决方案的要求包括四个关键组件:高速 LVDS 缓冲区,用于生成反序列化时钟的 PLL,输入数据捕获和齿轮,以及数据格式化。

FPGA 以 LVDS 格式接收或发送数据和时钟,数据速度相对较快。准确的速度取决于分辨率、帧率和显示器使用的颜色深度。

例如,800x600 到 1024x768 显示屏需要 LVDS 数据以 40MHz 到 78.5MHz 进行传输,从而达到 60Hz 到 75Hz 刷新率。这相当于 LVDS 数据速率为 280Mbps 至 549Mbps。

更高的分辨率显示器(如 1280x1024 60Hz)需要使用 108MHz 的 LVDS 时钟传输数据。对于此系统,数据将以 756 Mbps 的速度传输。

时钟生成

在 Lattice ECP3、Lattice ECP2/M 或 Lattice XP2 实现中,输入捕获电路使用双数据速率 (DDR) 寄存器,在时钟的上升和下降边缘捕获数据。

当作为一个接收器操作时,低速时钟提供的数据必须乘以 3.5 倍,以捕获两个时钟边缘的数据。如果输入捕获电路仅在时钟的一个边缘运行,则必须使用 7 的乘法因子。

作为一种替代方案,可以生成 7 个相移版本的低速时钟,并用 7 个不同的寄存器来捕获输入数据。然而,时钟产生和分布的挑战阻碍了这种方法用于 FPGA 实现。

时钟必须有相对较低的抖动,因为它的抖动必须在整个时序预算中考虑。同样,在任何时序分析中,都必须考虑到为输入或输出寄存器提供这个时钟的时钟分布网络的倾斜。

为了传输高速数据,发送器必须将用于将低速并行数据传输到接口的时钟乘以 3.5。同样,时钟的抖动及其分布的偏斜也很重要,因为它们会影响接口的时序预算。

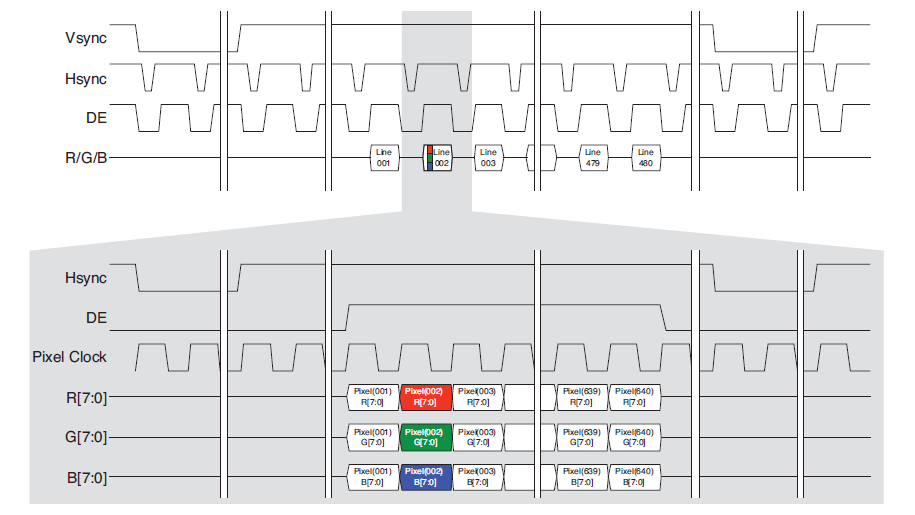

图 3 显示了 PLL 时钟产生,以及如何将视频帧第 2 行上的一个像素的 R、G、B 位、Vsync、Hsync 和 DE 分配给四个 LVDS 数据对。在 eclk 时钟的上升沿和下降沿采样数据位。

图3 视频信号的时序和 7:1 LVDS 通道连接接口

数据捕获

跟随 LVDS输入缓冲区的寄存器必须准确地捕捉数据。严格控制时钟和数据关系对于捕获传入的高速数据流非常重要。在数据传递到 FPGA 结构之前,还需要对数据的速度进行齿轮或降低。简体中文翻译。 让我们以LatticeECP2/M和LatticeECP3为例。LatticeECP2/M FPGA指定单个电路元件的工作频率为350MHz左右。对于LatticeECP3,它将在470MHz左右。在逻辑量合理的情况下,LatticeECP2/M的实际工作频率为225 MHz, LatticeECP3为350 MHz。因此,在I/O结构中可以实现的齿轮传动越大,FPGA结构对整体性能的限制的可能性就越低。类似的讨论也适用于传输路径。

数据格式化

最后一步是从 I/O 单元中取出数据,并将其格式化为由低速时钟计时的原始 7 位宽度。这种逻辑可以很容易地构建在 FPGA 结构中。

LatticeECP3, LatticeECP2/M 和 LatticeXP2 7:1 LVDS 接口

LatticeECP3、LatticeECP2/M和LatticeXP2架构为此接口提供了理想的解决方案。本节描述了使用LatticeECP3、LatticeECP2/M和LatticeXP2器件I/O结构实现7:1接收器和7:1发送器。简体中文翻译。

7:1 接收器

图 4 显示了在 LatticeECP3、LatticeECP2/M 或 LatticeXP2 设备内的系统间显示接口的接收端框图。接收器接收四个 LVDS 数据通道(每个 7 位)和一个 LVDS 时钟。

图4 7:1 接收器框图

数据和时钟通过可编程 I/O 单元 (PIC) 块中的 LVDS 缓冲区进入 LatticeECP3, LatticeECP2/M 或 LatticeXP2 设备。当使用 2 倍齿轮功能时,对于 LatticeXP2 和LatticeECP2/M 设备,这些缓冲区的工作频率高达 420MHz (即 840Mbps),对于 LatticeECP3 设备,这些缓冲区的工作频率高达 500MHz (即 1.0Gbps),支持最高的分辨率和显示刷新率。

LVDS 数据被馈送到 I/O 逻辑 DDR 寄存器,源同步 LVDS 时钟被馈送到锁相环 PLL。PLL 用于将时钟乘以 3.5,并产生一个通常为 90 度的相位移位。这个相移允许将时钟放置在数据有效窗口的中间。这种更快的相移时钟然后通过一个低斜边缘时钟网络分布到双数据速率输入捕获寄存器。PLL 也被用于产生一个较慢的时钟,它的频率是较快的边缘时钟的一半。这个时钟被馈送到使用主时钟树的 I/O 逻辑块中的 DDR 寄存器的第二阶段。

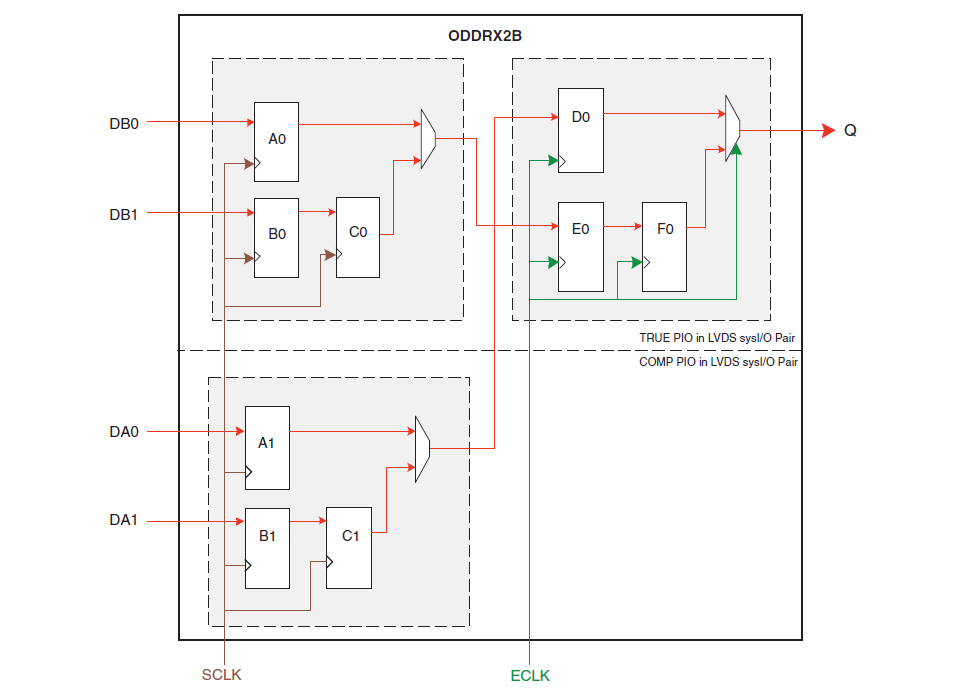

具有 2x 齿轮功能的 I/O DDR 寄存器 (IDDRX2B) 用于设计 LatticeXP2 和 LatticeECP2/M FPGAs。一个 2x DDR 元件以一半的时钟速率为每个 I/O 侧数据位提供四个 FPGA 侧数据位。齿轮允许使用高速边缘时钟(ECLK)将 I/O 数据多路复用/解复用到速度较慢的 FPGA 时钟速率(SCLK)。最后,所有的数据都在 SCLK 的上升边缘接收。图 5 是 IDDRX2B 的详细图。

图5 IDDRX2B 详细框图

IDDRX2B 模块在边缘时钟的两个边缘输入 DDR 数据,并生成四个数据流,所有这些数据流都位于较慢的 FPGA 时钟的上升边缘。图 5 的阴影部分显示了用于执行 2x 传动模式的 I/O 寄存器。互补 PIO 的 I/O 寄存器用于 DDR 齿轮模式。有关 DDR 寄存器和各种模式的更多信息,请参阅:TN1105, LatticeECP2/M High-Speed I/O Interface, TN1138, LatticeXP2 High-Speed I/O Interface and TN1180, LatticeECP3 High-Speed I/O Interface。

图 6 显示了使用 IDDRX2B 块进行输入齿轮的示例。

图6 IDDRX2B 的输入齿轮的示例

4 位并行数据然后在 4:7 解串器模块中以正确的速度转换为 7 位数据。解串器将IDDRX2B 的 4 位输出存储在 28 位宽移位寄存器中。

输入的 LVDS 时钟然后被用作一个分帧信号来检测 7 位数据帧的开始和结束。如果需要,可以在设计文件中修改 7 位数据的顺序。

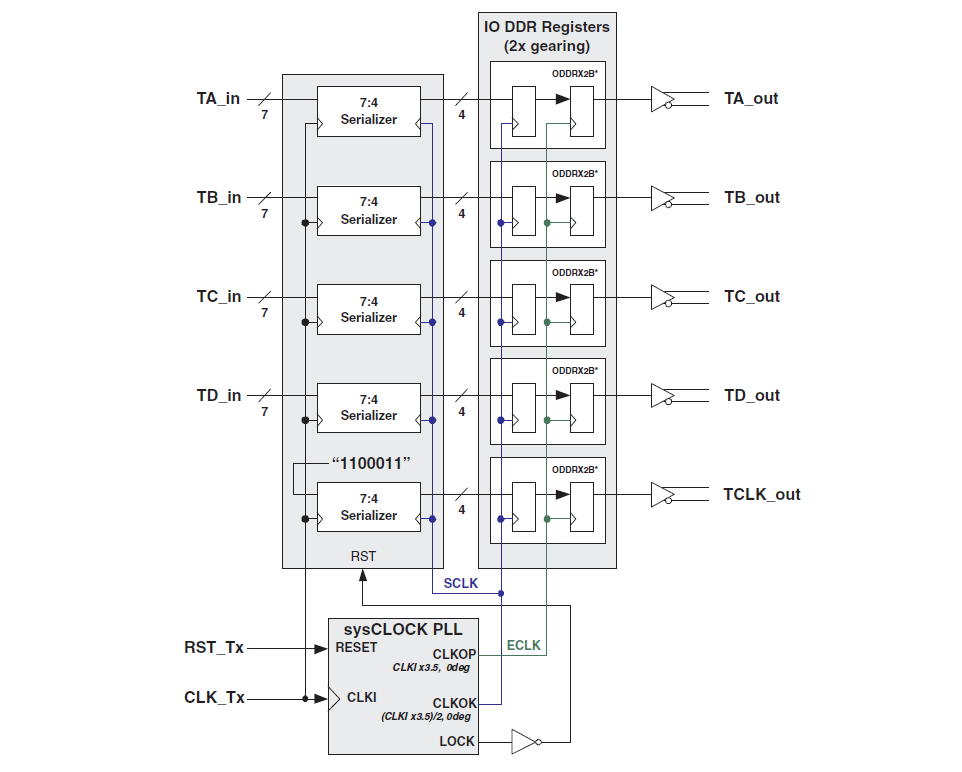

7:1 发送器

图 7 显示了 7:1 实现的传输端。在这种情况下,LatticeECP3、LatticeECP2/M 或LatticeXP2 设备接收 4 个通道的 7 位并行数据和慢时钟。

所有的 28 位并行数据与接收的慢时钟对齐。慢输入时钟被输入到 PLL。PLL 用于将时钟乘以 3.5 倍 (ECLK)。

PLL 还用于产生 3.5 倍时钟频率一半的时钟。这个时钟由图 7 中的 SCLK 表示。

I/O 逻辑模块中的 DDR 寄存器用于生成串行数据输出。LatticeXP2 和 LatticeECP2/M FPGAs 支持输出 DDR 寄存器模块,具有类似于输入 DDR 寄存器的 2x 齿。

使用带有 2x 齿轮(ODDRX2B) 而不是 1x 齿轮的输出 DDR 寄存器的优点是 FPGA 核心可以以输出 DDR寄存器所使用时钟速度的一半运行。

在发送到每个输出 DDR 寄存器之前,并行数据的 7 位需要转换成 4 位串行数据。

7:4 串行器模块用于完成此任务。这 7 位并行数据中的每一位都存储在 28 位宽的缓冲区中,与 SCLK 时钟对齐的 4 位数据被发送到 ODDRX2B 模块。

图7 7:1 发送器框图

ODDRX2B 还从 PLL 接收更快的 ECLK 并执行齿轮功能。齿轮允许用慢速 FPGA 时钟 (SCLK) 时钟的 I/O 数据多路复用到高速边缘时钟。所有的数据都是在 ECLK 的上升边缘传输的。

图8 显示了 ODDRX2B 的详细图。

图8 ODDRX2B 齿轮功能

ODDRX2B 模块输入来自慢速 FPGA 时钟 (SCLK) 两边 FPGA 织物的四位数据。这些输入还会在快速边缘时钟 (ECLK) 的两个边缘生成单个数据流。图 8 的阴影部分显示了在 2 倍齿轮模式下使用的 I/O 寄存器。

补充 PIO 的 I/O 寄存器用于 DDR 2x 齿轮模式。

图 9 显示了使用 ODDRX2B 块进行输入齿轮的示例。

图9 使用 ODDRX2B 进行输出齿轮的示例

ODDRX2B 的序列化数据输出使用高速 LVDS 缓冲区从设备发送出去。LatticeECP3 I/O 结构不同于 LatticeXP2 和 LatticeECP2/M 器件。

DQSBUF 原语(例如,用于 2x 齿轮的 DQSBUFE)必须被用来产生频闪逻辑和延迟用于输出 DDR 模块来正确复用 DDR 数据。

这个 DQSBUF 原语是通用 DDR 实现 (如 7:1 LVDS ) 的输出所必需的。由于 DQS 组中的所有 I/O 共享相同的 DQSBUF,因此建议将同一 7:1 LVDS 总线的尽可能多的 I/O 分组到一个 DQS 组中。

由于每个 DQS 组只包含有限数量的真 LVDS 引脚 (通常每个 DQS 组两个 I/O),如果真 LVDS I/O 用于7:1 LVDS 输出,更多的 DQSBUF 原语将需要将真 LVDS 输出扩展到相邻的 DQS 组。

注意,这不适用于使用模拟 LVDS 输出的设计。此外,LatticeECP3 设备 (IDDRX2D1/ODDRX2D) 中的I/O DDR 原语与端口定义中的 LatticeXP2 和 LatticeECP2/M 设备 (IDDRX2B/ODDRX2B) 中的 I/O DDR 原语也不同。

设计示例1: 环回测试

本文档包含的环回测试设计使用 Lattice FPGA 实现 7:1 发送器和接收器。图 10 显示了设计实现。有关 7:1 发送器和接收器的详细信息,请参阅图 4 和图 7。

在 FPGA 逻辑中使用计数器值生成 28 位传输数据。然后,该数据被串行化,并使用7:1发送器逻辑作为 4 位 LVDS 数据传输。4 位 LVDS 数据然后循环回 LatticeECP3, LatticeECP2/M 或 LatticeXP2 设备接收端,并使用 7:1 接收逻辑反序列化。

然后,这个反序列化的数据被送入数据比较逻辑模块,该模块将反序列化的接收器数据与传输的原始计数器值进行比较。当检测到两个数据值之间的每一个不匹配时,错误计数就会增加。在上面的章节中详细解释了 7:1 的发送器和接收器逻辑。

图10 环回测试框图

环回测试的实现结果

使用 LatticeECP2 高级评估板、LatticeXP2 高级评估板和 LatticeECP3 视频协议板对环回设计进行了测试。Lattice FPGA 发送和接收端均成功运行于LatticeECP3、LatticeECP2/M 和 LatticeXP2 的 108 MHz 发送和接收像素时钟。

对于 LatticeECP3,它可以运行到 135MHz。表 1 显示了该设计所利用的资源。

表1 环回测试设计性能和资源利用率

- 性能和利用率特性是通过使用 LFE3-95EA-7FN1156C 和 Lattice Diamond™1.2 设计软件生成的。当在不同的设备、密度、速度或等级中使用这种设计时,性能和利用率可能会有所不同。

- 使用 LFE2-50E-6F672C和 Lattice Diamond 1.2 设计软件生成性能和利用率特性。当在不同的设备、密度、速度或等级中使用这种设计时,性能和利用率可能会有所不同。

- 使用 LFXP2-17E-6F484C和 Lattice Diamond 1.2 设计软件生成性能和利用率特性。当在不同的设备、密度、速度或等级中使用这种设计时,性能和利用率可能会有所不同。

在本设计中,Lattice FPGA 兼有发送器和接收器的功能。

设计实例2: 展示 7:1 LVDS 接口,具有视频处理功能

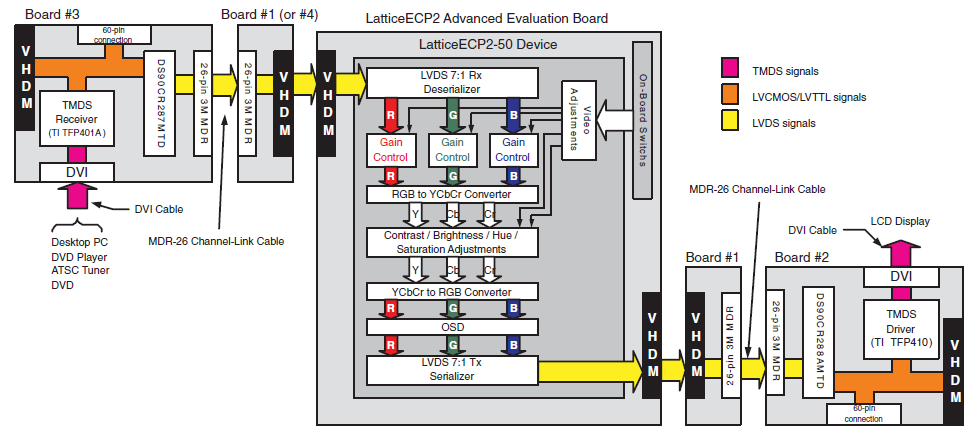

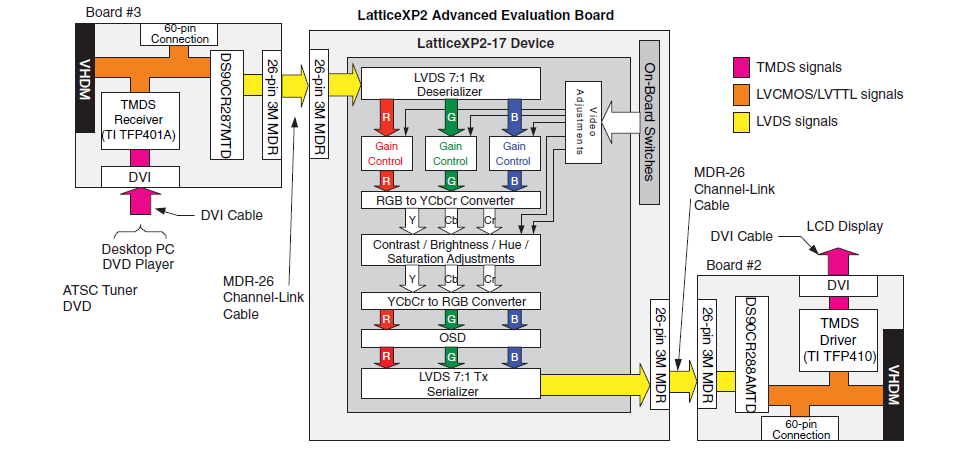

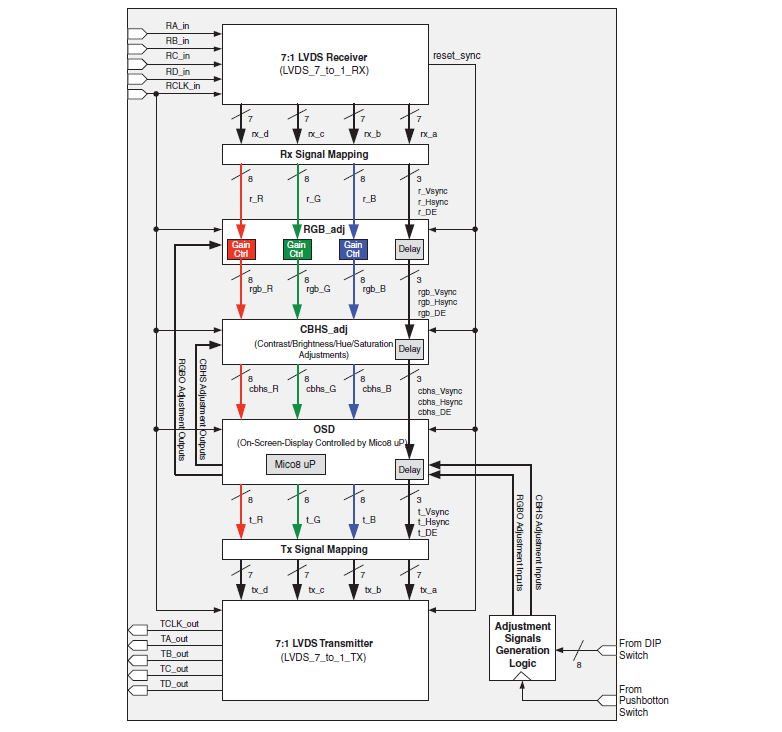

为了验证 Lattice FPGA 内 7:1 LVDS 接口的运行情况,Lattice 开发了如图 11 和 12 所示的测试系统。

该系统从 PC 机或 DVD 播放器等源中获取 DVI 格式的视频数据,并使用国家半导体通信链路发送器设备将其转换为 7:1 LVDS 源同步格式。

该图像数据被馈送给Lattice FPGA,其中 7:1 接收模块用于反序列化数据。然后,使用 Lattice FPGA 设备内的 7:1 发送器模块将该数据转换回串行数据。

然后,它使用源同步 7:1 LVDS 接口传输到一个国家半导体通道链路接收器设备,并最终显示。

图12 7:1 LatticeXP2 高级评估板上的接口测试系统

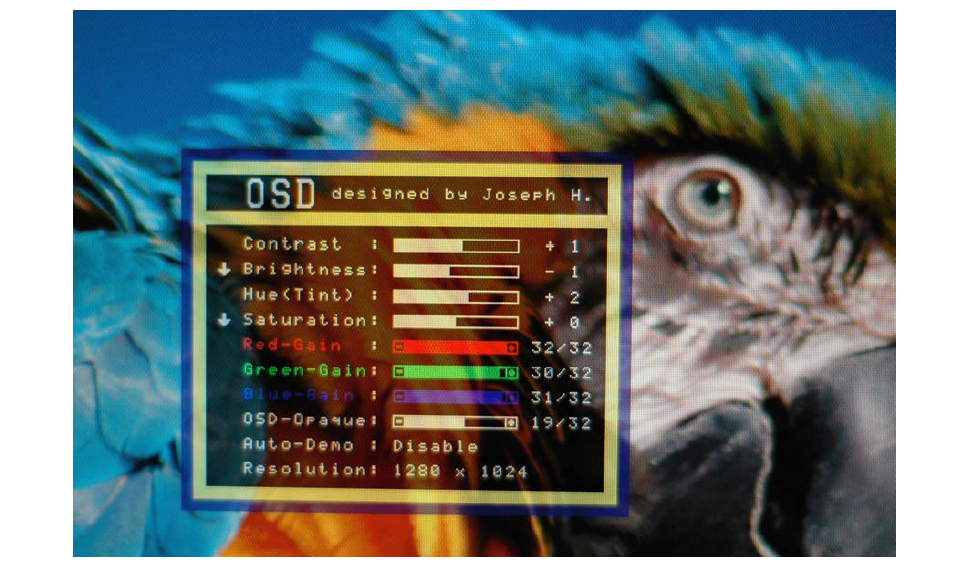

图 11 和 12 显示了 FPGA 器件内部设计的简化框图。除接收器和发送器模块外,中心逻辑块可以是任意定制的视频处理设计。为了演示目的,创建了图 11 和图 12 中所示的设计,以包括以下特性。

- R 增益、G 增益、B 增益控制

- 对比度、亮度、色调、饱和度控制

- 屏幕显示由 LatticeMico8 微处理器控制

- 屏幕显示不透明度控制

图13 视频处理设计示例

这个设计示例的框图如图 13 所示。该设计包括五个子模块:接收器、RGB_adj、CBHS_adj、OSD 和发送器。在 LatticeECP2 高级评估板上,8 位 DIP 开关 SW5 用于调整 R、G、B 增益、对比度、亮度、色相、饱和度和 OSD 不透明度。当特定的控制被选择时,需要拨动按钮 SW4 (即控制开关)来激活调整。SW5 还用于启用和禁用 OSD 和自动演示特性。表 2 列出了 SW5 引脚的功能。在 LatticeXP2 和 LatticeECP3 评估板上,相应的开关及其功能也列在表 2 中。

表2 切换视频颜色调整、演示和 OSD 控制

注: LatticeECP2高级评估板控制开关为 SW4, LatticeXP2 高级评估板控制开关为 SW5, LatticeECP3 视频协议评估板控制开关为 SW6。

视频处理设计实现结果

使用Lattice 7:1 LVDS演示套件验证了视频处理演示设计,该演示套件附带了LatticeECP3、LatticeECP2和LatticeXP2评估板和其他子板。视频源的运行频率为108MHz,图像分辨率为1280x1024。表3显示了该设计所利用的资源。

表3 视频处理设计性能与资源利用

- 使用 LFE3-95EA-7FN1156C 与 Lattice Diamond™1.2 设计软件生成性能和利用特性。当在不同的设备上使用本设计时,密度、速度或等级、性能和利用率可能会有所不同。

- 使用 LFE2-50E-6F672C 与 Lattice Diamond 1.2 设计软件生成性能和使用特性。当在不同的设备上使用本设计时,密度、速度或等级、性能和利用率可能会有所不同。

- 使用 LFXP2-17E-6F484C 和 Lattice Diamond 1.2 设计软件生成性能和利用特性。当在不同的设备上使用本设计时,密度、速度或等级、性能和利用率可能会有所不同。

模块 RGB_adj

使用sysDSP块实现9x9乘法器,RGB_adj模块将8位R, G, B颜色数据与R-, G-, B-增益相乘。这些增益是实数,值介于0和1之间。9个数据位表示实数,第8位表示整数部分,其余位表示实数的小数部分。小数部分,第7位表示2-1(即0.5),第6位表示2-2(即0.25),第5位表示2-3(即0.125),以此类推。例如,9位数据“011000000”将表示实际值0.5 + 0.25 = 0.75;9位数据“100000000”将表示真实值1.0。在设计的许多模块中都采用了类似的表示非整型实值的方法。整数位和小数位的数量可以改变来表示不同范围的实数。

模块 CBHS_adj

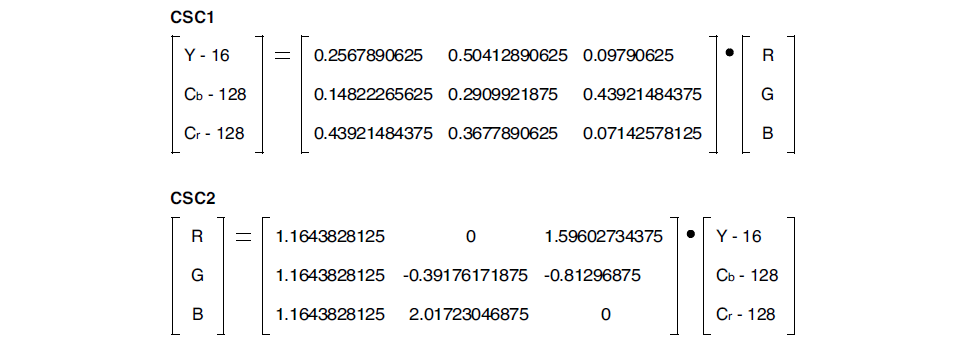

为了调整视频图像的对比度、亮度、色调和饱和度,RGB颜色空间中的像素数据需要转换为YCbCr颜色空间。图14显示了CBHS_adj模块的框图。调整后,YCbCr颜色空间中的像素数据将被转换回RGB颜色空间。YCbCr颜色空间中有偏移量。Y、Cb、Cr的偏移量分别为16、128、128。当执行对比,亮度,色调和饱和度调整时,这些偏移需要删除。因此,颜色空间转换器CSC1和CSC2可在RGB和YCbCr之间转换像素数据,而不需要添加Y、Cb和Cr偏移量。

图14 对比度、亮度、色调和饱和度调整

CSC1 和 CSC2 转换器中使用的方程是:

色调调整需要正弦和余弦函数。查找表ROM用于实现这两个功能。Tcl脚本用于创建用于正弦/余弦ROM内容初始化的内存文件。

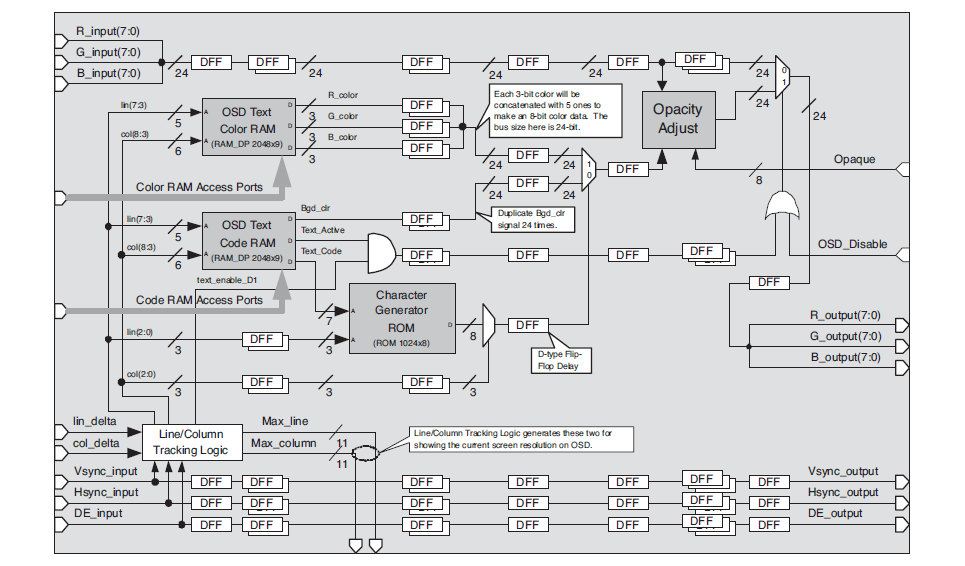

图15 屏幕显示模块

OSD_main 子模块的框图如图 16 所示。有两个双端口 RAM 来保存 OSD 上显示的字符代码和字符颜色。每当 LatticeMico8 微控制器更新 RAMs 内容时,OSD 内容就会发生变化。字符模式存储在字符发生器 ROM 中。

图16 OSD_main子模块

行/列跟踪逻辑块控制 OSD 的位置,还用于跟踪视频图像的当前分辨率。LatticeMico8 将读回 Max_行和Max_列,以在 OSD 上显示分辨率。

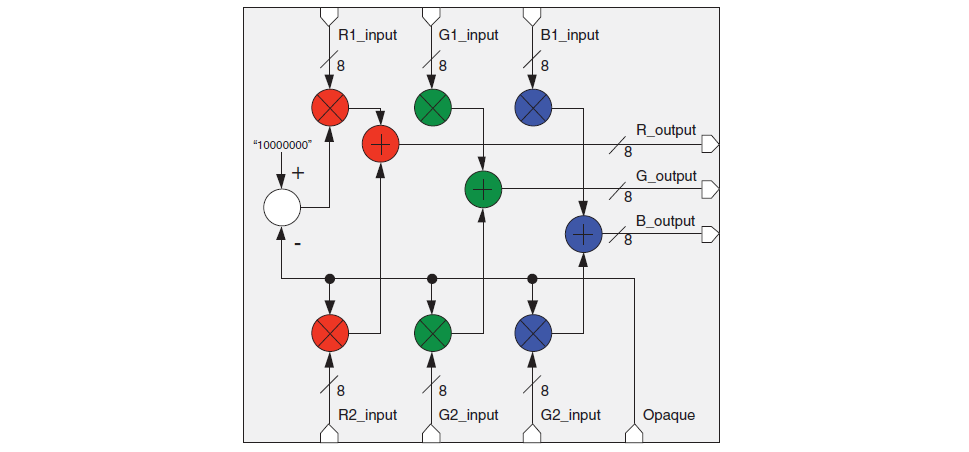

OSD 不透明度控制也在 OSD_main 子模块中实现。不透明值是介于 0 和 1 之间的实数,默认值为 1。当该值减小时,OSD 将变为半透明。图 17 显示了 OSD 不透明度控件的框图。

图17 OSD不透明度控制

图18 半透明 OSD 显示在显示屏上

总结

LatticeECP3、LatticeECP2/M 和 LatticeXP2 FPGA 系列非常适合高速 LVDS 视频应用。除了高速捕获视频数据外,这些系列还能够使用片上 sysDSP 块和嵌入式 RAM 块处理视频数据。

参考资料:

1. LatticeECP3, LatticeECP2/M and LatticeXP2 7:1 LVDS Video Interface

评论