一、 S32K144 ADC 介绍

1. ADC 模块特性

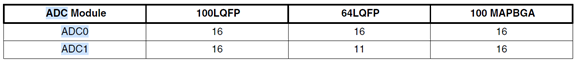

S32K144 芯片包含两个ADC模块,分别记为 ADC0 和ADC1。这两个模块都是线性逐次逼近型(Successive Approximation Register,SAR)A/D 转换器,最高转换精度(分辨率)为 12bit。 每个模块包含16个外部模拟输入通道:

- ADC连接/通道分配

引脚的ADC复用功能请参照S32K144_IO_Signal_Description_Input_Multiplexing.xlsx

- ADC硬件交错通道

在 S32K144 上有几个特殊的 ADC 通道支持 ADC 的硬件交错功能。例如 ADC0_SE4 和ADC1_SE14,这两个通道可以单独工作,但是也可以作为硬件交错来使用。在硬件交错模式,在 PTB0引脚上的信号可以同时被 ADC0 和 ADC1 采样。交错模式由 SIM_CHIPCTL[ADC_INTERLEAVE_EN] 位实现。

以下是可支持引脚交错模式的引脚:

ADC0_SE4和ADC1_SE14通道交错在PTB0引脚上;

ADC0_SE5和ADC1_SE15通道交错在PTB1引脚上;

ADC1_SE8和ADC0_SE8通道交错在PTB13引脚上;

ADC1_SE9和ADC0_SE9通道交错在PTB14引脚上。

- ADC参考选项

- VREFH/VREFL-连接作为初始的参考选项

- VALTH/VREFL-连接作为另选的参考选项

ADCx_SC[REFSEL]位可以选择ADC的参考电压源。

- ADC触发源

- 触发器通过 PDB 或者 TRGMUX 连接,并提供灵活的触发组合。

- 2xPDB 产生触发和预触发给 2xADC(ADC 和 PDB 都是成对动作的,例如 PDB0 和 ADC0,PDB1 和 ADC1),每个 PDB 通道最多有8个与处罚期给 ADC 通道控制。

- 每个ADC最少有1个外部引脚(通过TRGMUX支持)

- 软件必须确认相对的优先级

- 在上一个转换完成后开始下一个转换

- 通过 TRGMUX,CMP 输出,LPIT,RTC 和 LPTMR 都可以作为每个ADC的触发源。

- LPIT 支持最多4个与处罚期,来限制只在每个 ADC 的 ADHWTSO~ADHWTS3。对于剩下的外设,需要软件扩张来提供预触发器,这部分参照 SIM_ADCOPT[ADCxSWPRETRG] 设置软件预触发器。

- ADC 低功率模式

ADC 在 STOP,VLPR,VLPW 和 VLPS 模式都是可用的,在 VLPx 模式,ADC 时钟源只能是 OSC和 SIRC。

- ADC特征

- 12-bit精度的线性逐次逼近算法

- 最多16个单端模拟外部输入

- 输出模式:

- 单端12-bit,10-bit,8-bit

- 单端输出为右对齐的无符号形式

- 单次或持续转换

- 可配置的采样时间和转换速度/功率

- 转换完成/硬件平均值计算完成标志和中断

- 4种输入时钟源选择

- 低噪声低功率运行模式

- 可选的硬件转换触发器

- 自动产生多于,少于或等于的比较中断,或者是在范围内、范围外或一个可配置的值

- 温度传感器

- 硬件平均值计算功能

- 可选的电压参考值:外部的或可供选择的

- 自我矫正模式

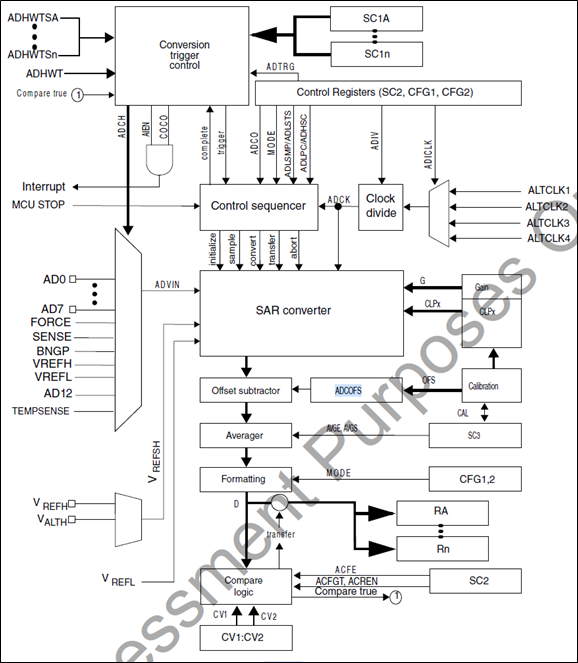

2. ADC结构框图

ADC 模块框图

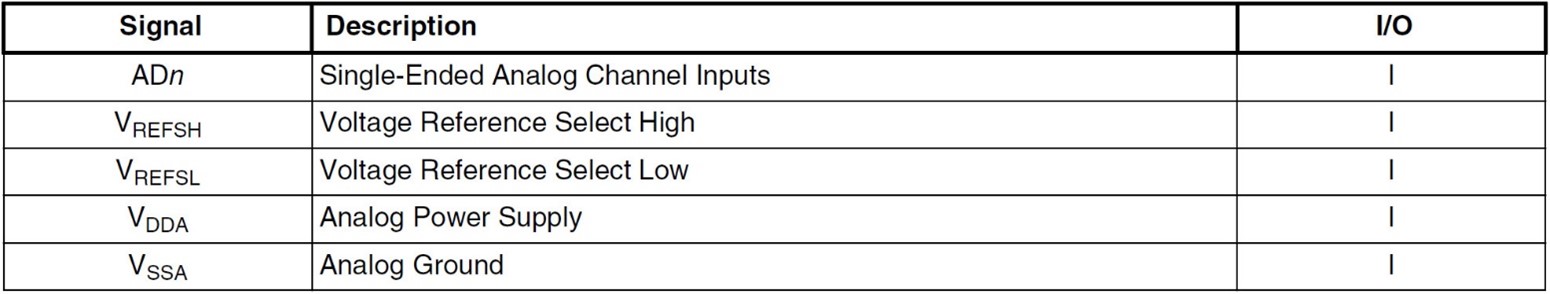

3. ADC 信号描述

ADC 模式支持最多 16 个单端输入,还需要4个电源/参考/地连接。

- 模拟电源(VDDA)

ADC 模拟部分使用 VDDA 作为电源连接。在一些封装中,VDDA 内部连接到 VDD。如果外部可用,则将 VDDA 引脚连接到与 VDD 相同的电压电位。

- 模拟地(VSSA)

ADC 模拟部分使用 VSSA 作为地连接。在一些封装中,VSSA 内部连接到 VSS。如果外部可用,则将 VSSA 引脚连接到与 VSS 相同的电压电位。

- 参考电压选择

VREFSH和VREFSL是ADC模块的高、低参考电压。通过将 VREFSH 配置为 VREFH 或 VALTH,可以将ADC配置为接受 VREFSH 和 VREFSL 的电压参考对之一。每对包含一个必须在最小 Ref 高压和 VDDA 之间的正基准,和一个必须在 VSSA 相同电位的地基准。这两对是外部(VREFH和VREFL)交替(VALTLH和VREFL)。这些参考电压使用SC2[REFSEL]来选择。备用电压参考,VALTH可以选择额外的外部引脚或内部电源取决于MCU的配置。查看芯片配置信息的电压参考具体到这个MCU。

在一些封装中,VREFH 连接到 VDDA, VREFL 连接到 VSSA。如果外部可用,正基准可以连接到与VDDA相同的电势,或者可以由外部电源驱动到最小 Ref 高压和 VDDA 电势之间的电平。VREFH 不能超过 VDDA。将接地参考点连接到与 VSSA 相同的电压电位。

- 模拟通道输入(ADx)

ADC模块支持多达8个模拟输入。一个模拟输入通过SC1[ADCH]通道选择位选择转换。

二、 S32DS ADC 例程简介与应用

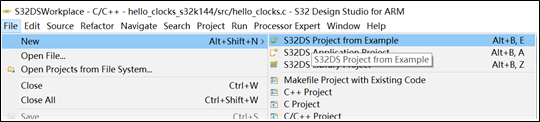

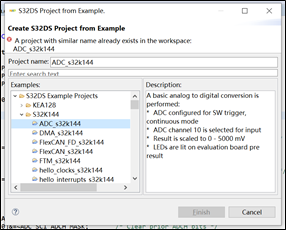

1. 例程导入

- 打开S32 Design Studio,点击:“File”->“New”->“S32DS Project from Example”。

- 在弹出的窗口选取 S32K144 目录下的 ADC 例程,点击“Finish”。

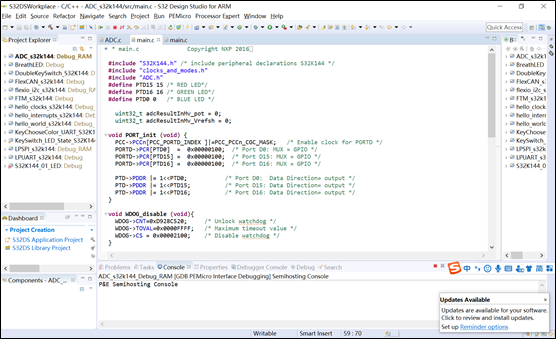

- 点击左上角“Build”按钮,编译例程。

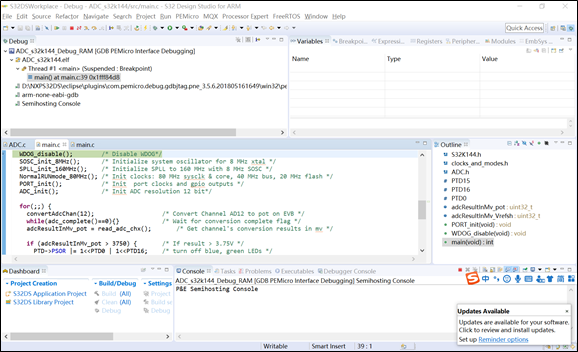

- 点击“Debug”按钮。进入例程Debug页面。

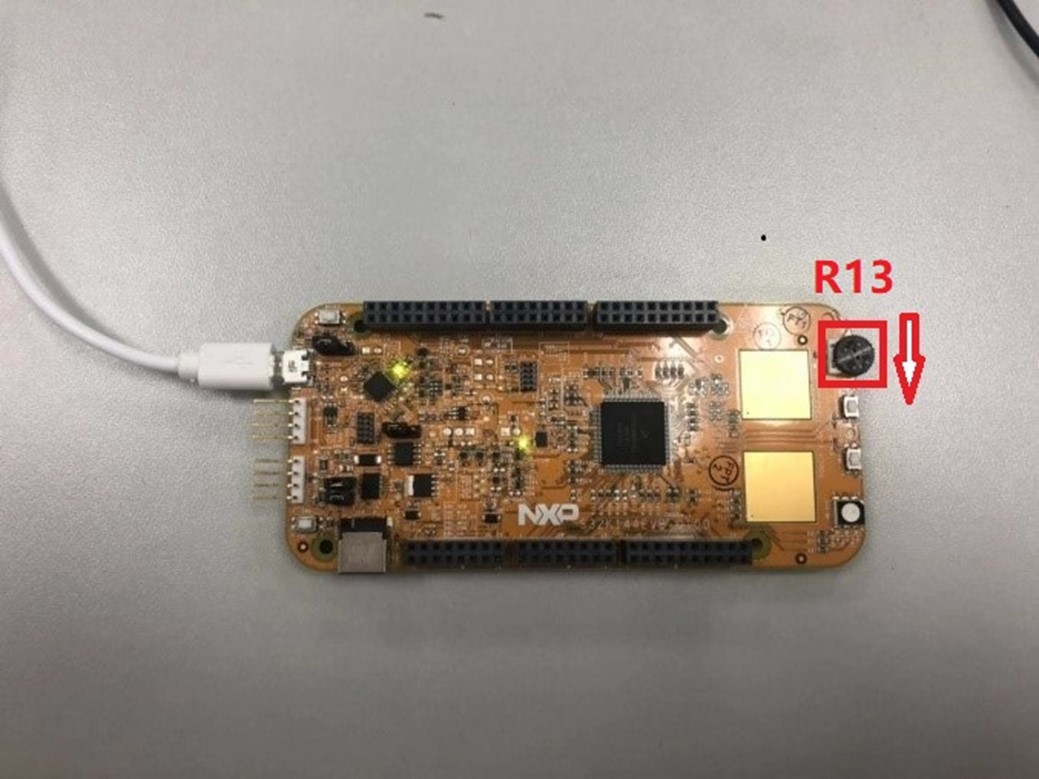

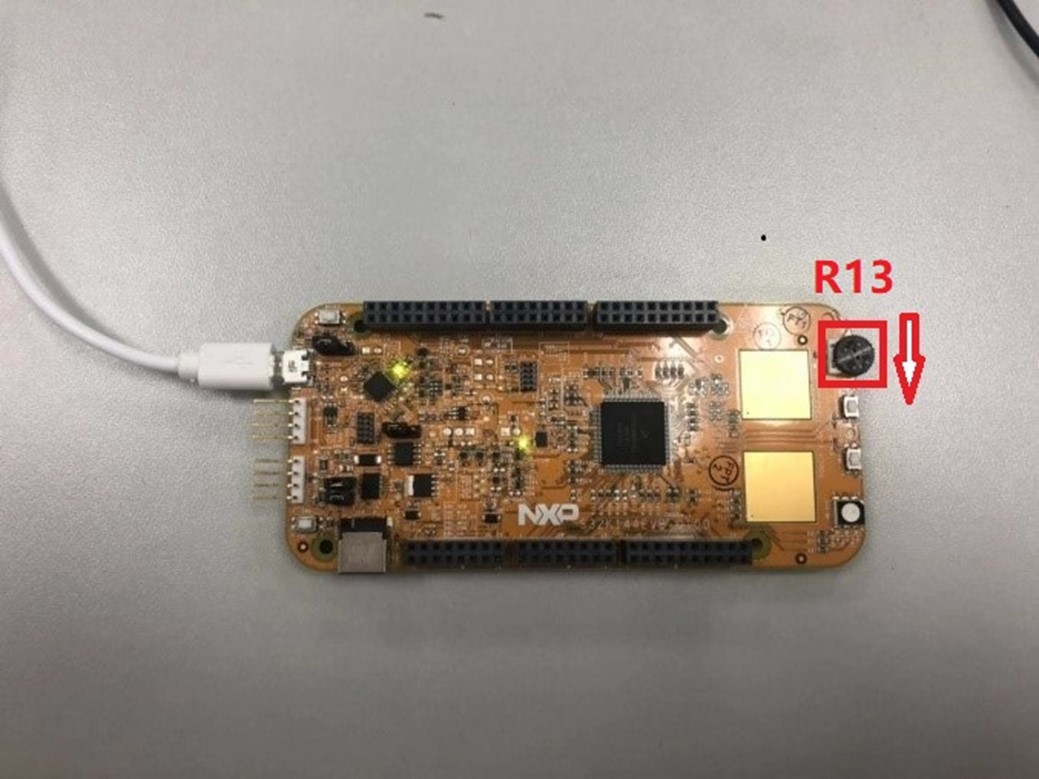

- 点击运行程序 按钮,顺时针旋转调整 EVM 板上电位计 R13 到最小,RGB 灯 D11 熄灭。

D11 熄灭

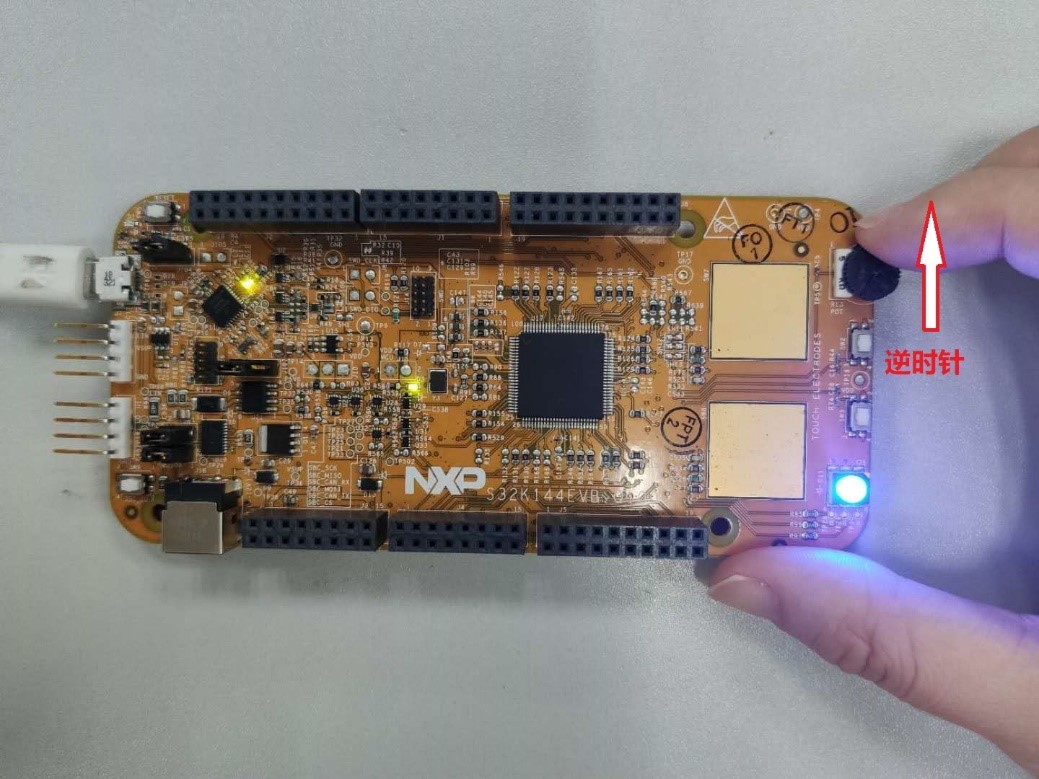

- 逆时针旋转电位计 R13,D11 由熄灭变为蓝灯。

旋转R13,D11 变为蓝灯

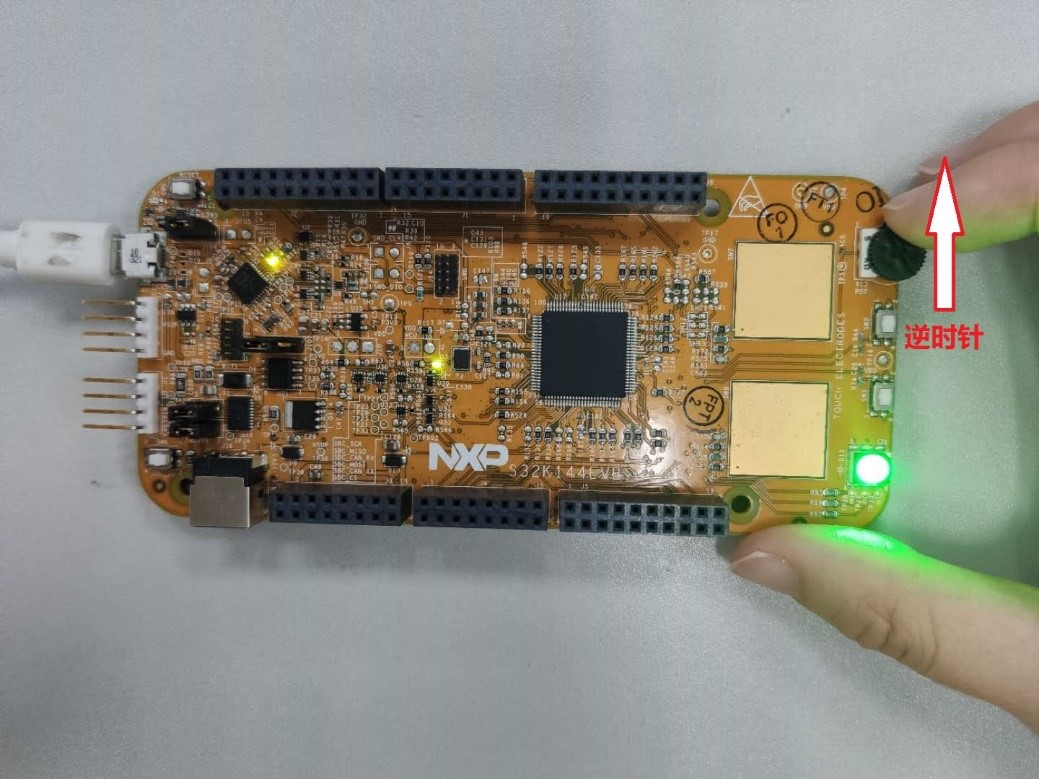

- 继续逆时针旋转电位计 R13,D11 由蓝灯变为绿灯。

旋转R13,D11 变为绿灯

- 继续逆时针旋转电位计R13,D11由绿灯变为红灯。

旋转R13,D11 变为红灯

旋转R13,D11 变为红灯

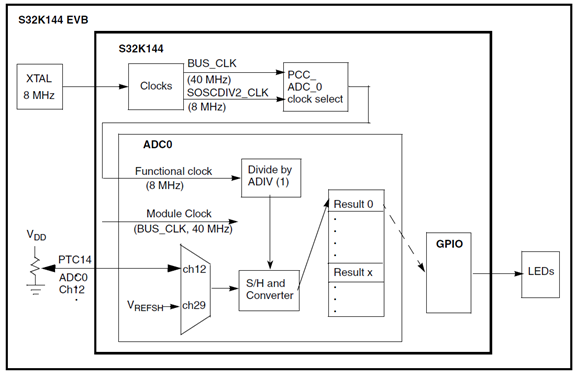

2. 例程简介

- ADC 例程介绍

此例程使用配置为一次转换的软件触发来转换两个 ADC 通道。每次转换需要自动的软件触发。一个ADC通道(ADC0_CH12)连接到 S32K144 EVB上的一个电位计,另一个连接到 VREFSH。ADC 转换的结果被缩放到 0~5000 mV。通过 LED 灯的显示颜色来表示 ADC 转化的结果,对应如下表。

|

缩放的转换结果 |

LED颜色 |

|

3750-5000mV |

红色 |

|

2500-3750mV |

绿色 |

|

1250-2500mV |

蓝色 |

|

0-1250mV |

熄灭 |

- ADC 例程框图

3. 例程设计思路

在这个简单的例程中没有使用ADC的矫正。转换的结果可能会比规定的精度稍低。初始化矫正机制可以查询 S32K144 的技术文档中的 ADC 部分。

程序设计思路:

- 禁止看门狗

- 系统时钟:初始化系统晶振(SOSC)为8MHz,系统时钟为80MHz,运行模式(RUN mode)为80MHz

- 初始化端口引脚:

- 为 PORT D 使能时钟

- PTD0:GPIO 输出使能,连接到蓝灯

- PTD15:GPIO输出使能,连接到红灯

- PTD16:GPIO输出使能,连接到绿灯

- (由于复位,不需要配置任何模拟引脚)

- 初始化ADC:

- 选择SOSCDIV2_CLK为时钟源,并使能给ADC模块

- 禁止模块功能,禁止模块中断请求(复位默认值)

- 配置ADC使用SOSCDIV2_CLK进行转换,分频系数为1

- 配置采样时间为13个ADCK时钟周期(复位默认值)

- 选择转换为软件触发,没有比较功能,没有DMA,使用默认的参考电压引脚-外部引脚VREFH和VREFL(复位默认值)

- 静止持续的转换(每次转换只有一次软件触发),禁止硬件平均值计算,静止矫正序列启动

- 主函数循环:

- 生成通道12ADC转换命令,通道12连接到开发板上的电位计(使用ADC_SC1[0]设置软件触发)

- 等到转换完成标志。当转换完成时:

- 读取结果,将结果缩放到0-5000mV(对于所有软件触发,结果在ADC_R[0]中)

- 在每一个电压范围中点亮LED灯

- 生成通道29装换功能并读取为ADC参考高电平(对于所有软件触发,使用ADC_SC1[0])

- 等待转换完成标志。当转换完成时:

- 读取结果,将结果缩放到0-5000mV(对于所有软件触发,结果在ADC_R[0]中)

三、 Tips

- 默认情况下,ALT0 模式对应禁用功能,pad 代表禁用(高阻抗)状态。如果 pad 包含模拟功能,则一旦将模拟模块配置为启用相应的通道/输入,ALT0 模式就与模拟功能对应,不需要再额外配置引脚信号。以下为例程所用 PTC14 的信号多路复用功能:

|

Pin Name |

DEFAULT |

ALT0 |

ALT1 |

ALT2 |

…… |

|

PTC14 |

ADC0_SE12 |

ADC0_SE12 |

PTC14 |

FTM1_CH2 |

…… |

- ADC 模块还具有的功能如下:

- 可配置自动和数值比较寄存器(ADC_CV1 和 ADC_CV2)比较转换结果。

- 设置 ADC_SC3[AVGE] 位后,在任何转换模式和配置信息下,都可使能硬件计算均值功能。

- 采用硬件触发模式时,在完成规定次数的转换后,ADC 模块会对每次的转换结果求均值,防止干扰,避免错误操作。

- 具有芯片校验功能和偏移量修正功能,从而提高 ADC 模块的精度。

四、 参考文献

[1] S32K144 Reference Manual.pdf,NXP

[2] Cookbook for SAR ADC Measurements.pdf,Freescale

[3] S32K1xx ADC guidelines, spec and configuration, NXP

评论