1, EMMC概述

eMMC,全称为embedded MultiMediaCard。MultiMediaCard即 MMC,是一种闪存卡(Flash Memory Card)标准,它定义了 MMC 的架构以及访问Flash Memory的接口和协议,而MMC前面加了个embedded,主要就是为了突出它是embedded 在电路板上的。 eMMC 是对MMC 的一个拓展,以满足更高标准的性能、成本、体积、稳定和易用等方面的需求,近年来在手机,平板电脑以及对体积、可靠性和性能要求高的嵌入式领域得到广泛的应用.

2, eMMC内部架构

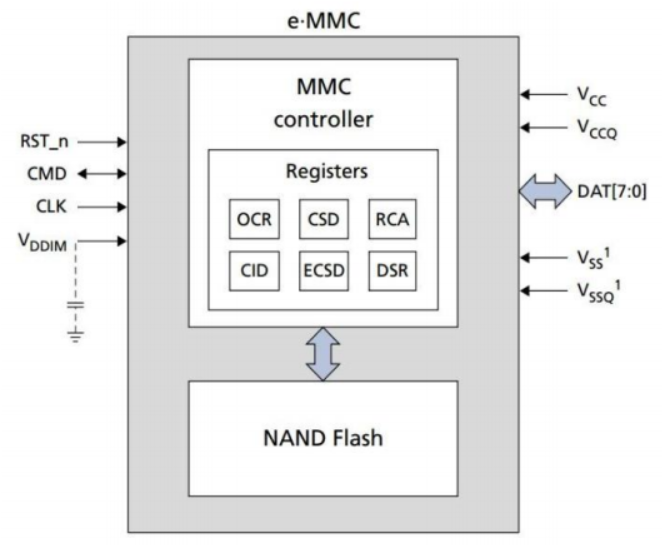

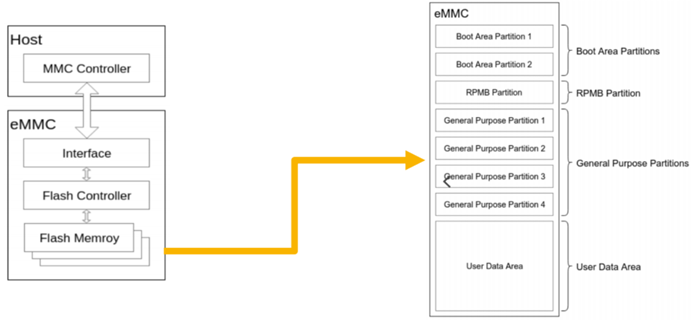

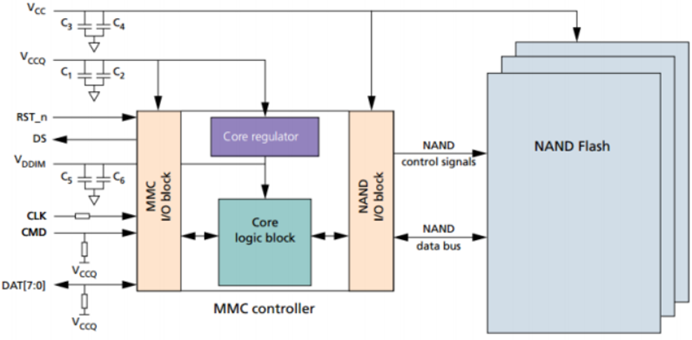

eMMC内部主要可以分为 Flash Memory、Flash Controller 以及 Host Interface 三大部分:

eMMC的Flash Memory都是使用的NandFlash作为存储介质,其内部又可分为BootArea(4MB), RPMB(4MB), General Purpose(默认不存在)和User Data分区(总容量 - 其他分区空间),注意这几个分区为硬件分区,每个存储空间都是独立寻址的,即访问地址范围为 0 ~partition size,具体访问哪个分区需要主机发送命令来选择PARTITION_ACCESS.

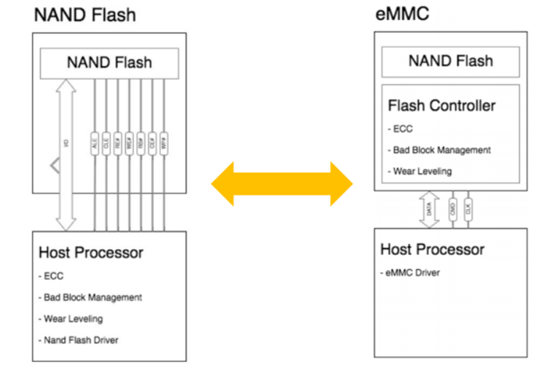

eMMC内部集成了Flash Controller,用于完成擦写均衡、坏块管理、ECC校验等功能。相比于直接将 NAND Flash 接入到 Host 端,eMMC 屏蔽了 NAND Flash 的物理特性,可以减少 Host 端软件的复杂度,让 Host 端专注于上层业务,省去对 NAND Flash 进行特殊的处理。同时,eMMC 通过使用 Cache和Memory Array 等技术,在读写性能上也比 NAND Flash 要好很多.

EMMC缺点:

- 相对NandFlash会贵.

- 封装BGA(因为EMMC速度比较快,BGA封装对信号完整性比较好).

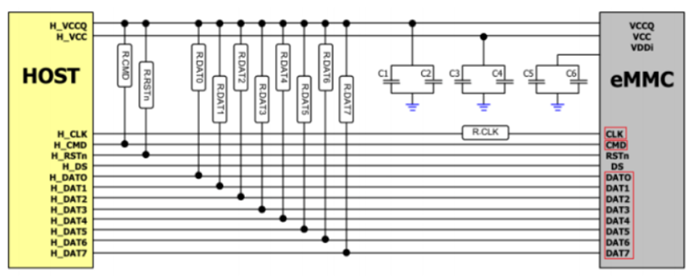

--eMMC与Host端的接口为8位并行接口:

I,Clk: 0~200MHz,每个cycle可以在上升沿或下降沿传输,也可以在上升沿和下降沿都传输;

II,Data_Strobe:由slave device 发送给host controller,主要用在HS400 mode(5.0规范以后版本才有),频率与clk一致,启用后可以提高数据传输的稳定性,省去总线 tuning 过程;

III,CMD:双向信号线,用于从host发送命令给device和device发送response给host,总线上的所有通讯都是由Host 端以一个 Command通过CMD信号发起;

IV,DAT[0:7]:双向信号线,工作在push pull mode,支持 1bit, 4bit, 8bit传输,默认上电或reset后只有DATA0用于数据传输,完成初始化后,可配置 为DAT0-3(4线模式)或者 DAT0-7(8线模式) 进行数据传输.

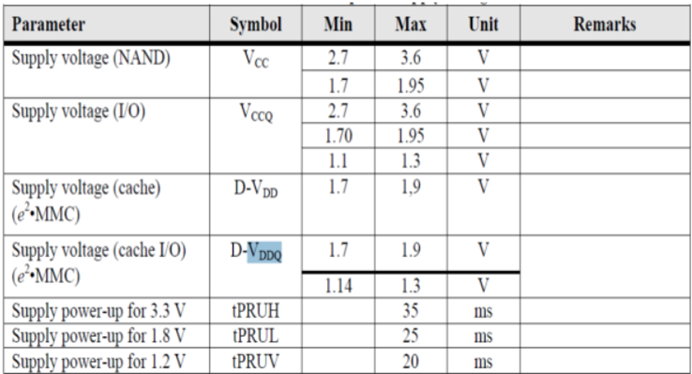

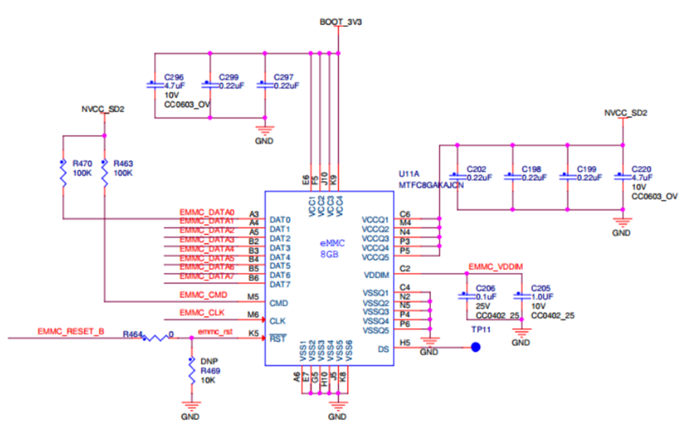

3,eMMC电源

eMMC有两组电源域,其中VCCQ主要用于eMMC IO BLOCK的供电也就是与host接口IO部分的供电,同时也给eMMC内部的Flash控制器供电,VCC则主要给eMMC内部的NandFlash存储介质以及eMMC Flash控制器与NandFlash的接口IO供电;

VCC支持两种电压,2.7v~3.6v和1.7~1.95v。而VCCQ则支持三种电压,2.7v~3.6v,

1.7v~1.95v和1.1v~1.3v,其中VCCQ(2.7v~3.6v)范围下不支持HS200和HS400速度模式;

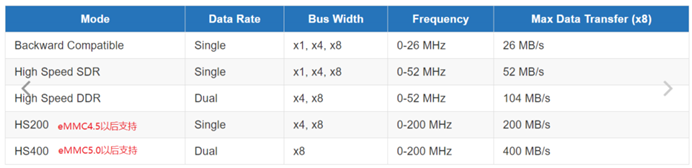

4,eMMC速率

随着eMMC 协议的版本迭代,eMMC 总线的速率越来越高。为了兼容旧版本的 eMMC Device,所有 Devices 在上电启动或者 Reset 后,都会先进入兼容速率模式(Backward Compatible Mode)。在完成 eMMC Devices 的初始化后,Host 可以通过特定的流程,让Device 进入其他高速率模式,目前支持以下的几种速率模式

--注意:I.MXRT105X,106X目前只能支持到EMMC4.5(HS200),I.MXRT117X能支持到EMMC5.0(HS400).

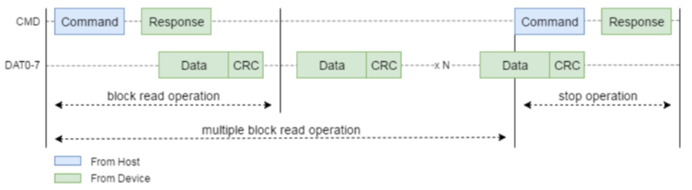

5,eMMC读写时序

Read Data:

Write Data:

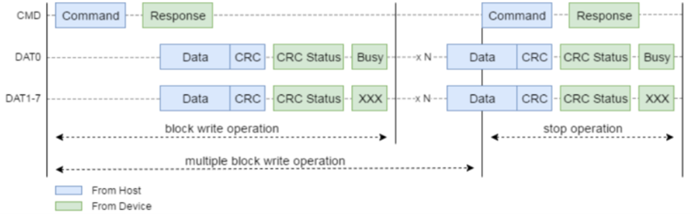

6, I.MXRT1052的EMMC接口

uSDHC databus and power domain:

--i.MXRT1052有两个uSDHC接口都可以接入eMMC device,uSDHC1和uSDHC2,

其中uSDHC1支持1-bit和4bit databus模式,

而uSDHC2支持1-bit,4-bit和8-bit databus模式,而IO接口则支持1.8v和3.3v电源,

--其中uSDHC1的接口电平由NVCC_SD0电源域管理,uSDHC2接口电平由NVCC_SD1管理,具体电平由外接设备决定也可以动态切换.

uSDHC supported spec. and speed mode:

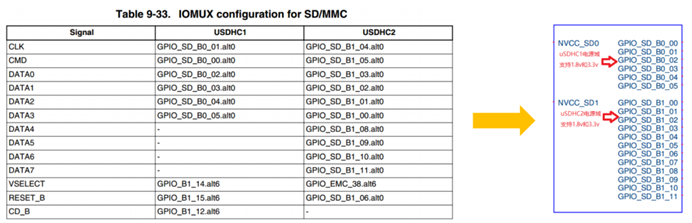

-- uSDHC的时钟源可选择PLL2_PFD0和PLL2_PFD2,最高时钟频率为208MHz;

uSDHC clock domain:

Note:uSDHC时钟推荐选择PFD0,因为RT1052的代码里默认都把PFD2作为SEMC的时钟源,而SDRAM最高为166MHz,这样uSDHC如果选择同一个时钟源则速度受限。

7,I.MXRT eMMC参考原理图

8,i.MXRT EMMC API函数.

--对i.MXRT系列的应用来说,更多的应用场景是涉及到对eMMC的数据读和写,所以无论是裸数据读写还是通过嵌入文件系统来管理读写,都是需要打通最底层对eMMC的读、擦和写,换句话说就是向上层提供如下图所示的Init,Read, Write和Erase的API并设计好传参.

--对eMMC来讲,其读写操作的最小单位与NandFlash一样为Block,每个Block的size默认为512 Bytes,而擦除则是以Group为单位,而每个Group的size则可以通过CMD命令读取eMMC的CSD寄存器来判断.

A, status_t MMC_Init(mmc_card_t *card);

B, status_t MMC_CardInit(mmc_card_t *card);

C, status_t MMC_ReadBlocks(mmc_card_t *card, uint8_t *buffer, uint32_t startBlock, uint32_t blockCount);

D, status_t MMC_WriteBlocks(mmc_card_t *card, const uint8_t *buffer, uint32_t startBlock, uint32_t blockCount);

E, status_t MMC_EraseGroups(mmc_card_t *card, uint32_t startGroup, uint32_t endGroup);

9,基于NXP提供的eMMC读写驱动示例工程,做板级的驱动移植注意事项.

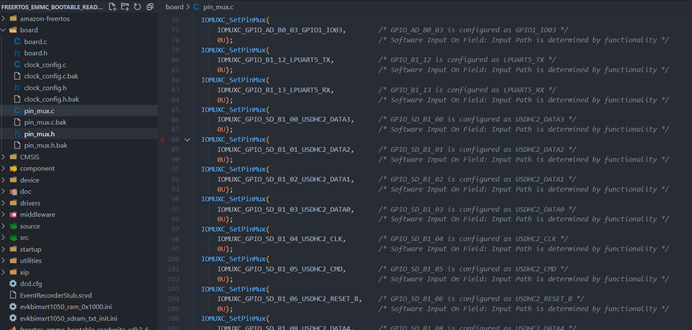

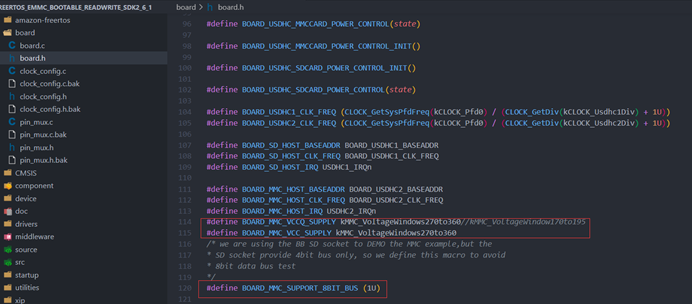

--首先修改板级支持文件,pinmux.c和board.h,将其修改成板子eMMC所连接的uSDHC接口,并且配置好eMMC的VCC和VCCQ电压,VCCQ电压为3.3v时最高速度只能支持到DDR52速度模式

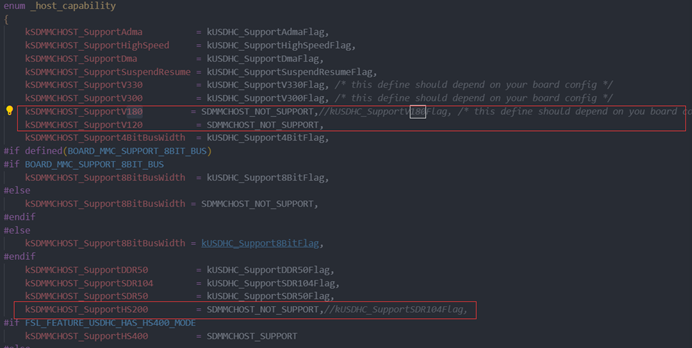

--如果VCCQ使用3.3v供电,则需要修改fsl_sdmmc_host.h文件,将V180,V120电压模式和HS200速度模式手动修改成 SDMMC_NOT_SUPPORT,避免sdmmc里面状态机切换成HS200;

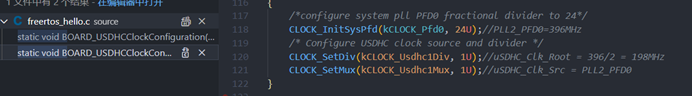

--uSDHC时钟部分,建议把uSDHC的时钟源选择PLL2_PFD0并且2分配为198MHz(uSDHC模块最高工 作频率为208MHz),避免跟SDRAM的时钟源选择同一个.

评论

访客

2021年8月14日