1,简介:

PLU可以简单理解为实现复杂功能的逻辑门电路.可以用来替换绝大部分74XX系列逻辑器件. 这些外部组件用于粘合微控制器和外部设备,简化 PCB 并节省设计成本.

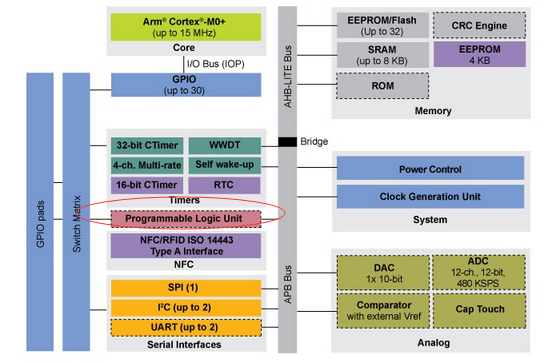

图 1 为 LPC80x MCU 系列

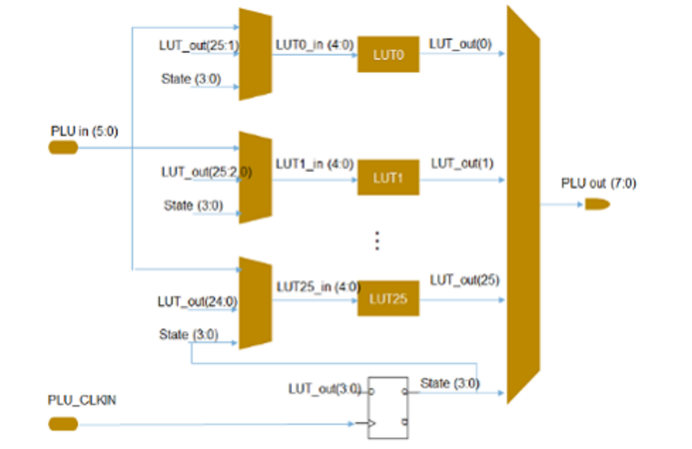

PLU 由 26 个英文字母相互连接成的数组、5 个输入查找表(LUT)和 4 个触发器组成。每个 LUT 包含一个 32 位真值表(查找表)寄存器和一个 32:1 多路复用器。在工作时,五个 LUT 输 入控制多路复用器的选择行。这种结构允许输入的五个 LUT 按任意逻辑组合。

2,特性:

-- PLU 用于创建包括简单状态机在内的小型组合和/或顺序逻辑网络。

-- PLU 由 26 个可互连的 5 输入查找表(LUT)和 4 个触发器组成。

--八个主要输出可以被一个多路复用器从所有 LUT 输出和 4 个触发器中挑出来。

--如果要实现顺序网络,则必须在 PLU_CLKIN 引脚上施加一个驱动 4 个触发器的外部时钟。

--可编程逻辑可以通过外部引脚与引脚的连接来驱动芯片上的输入/触发器。

--提供了一套工具来简化 PLU 的编程,以实现 Verilog RTL 设计中描述的逻辑网络。

3,优点:

--替换7400系列的组合逻辑。

--使用触发器进行状态机设计。

--地址解码器。

--模式匹配。

--低功耗应用,PLU 在深度睡眠和节电模式下工作。

--可编程的,因此 PLU可以重新编程和重用。

--使用SWM和PLU 进行无缝连接。

4,引脚说明:

LPC8XX PLU 模块中至多有六个主输入,一个时钟输入和八个主输出。 所有输入都通过芯片级 I / O 多路复用直接连接到封装引脚。 通过配置相关的 SWM 寄存器(PINASSIGN_FIXED0),可以启用所有这些引脚。

一个特定的逻辑网络可能并不需要所有有效的输入或输出。用户可以指定使用哪些输入和输出,以及这些输入和输出将连接到哪个封装引脚才能配置成最高级别 IO 的一部分。

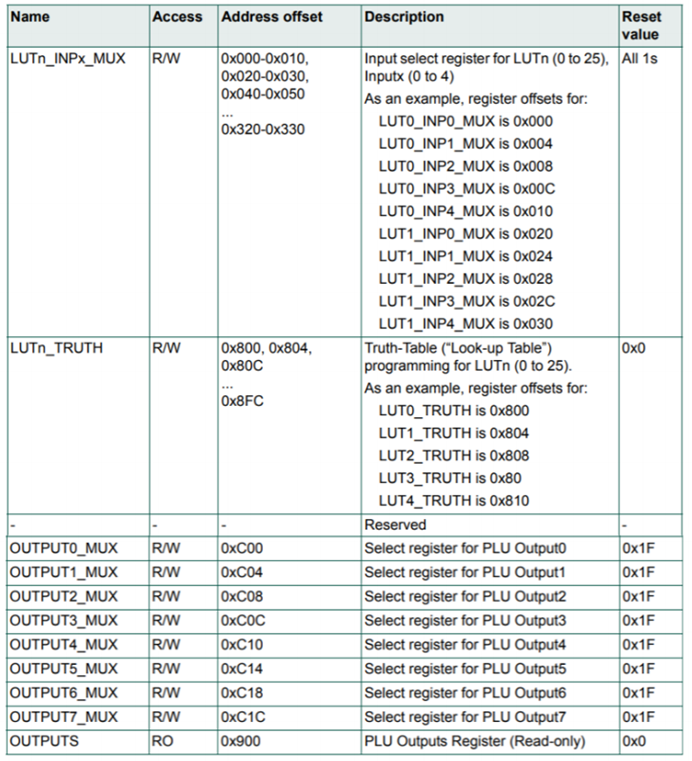

5,寄存器:

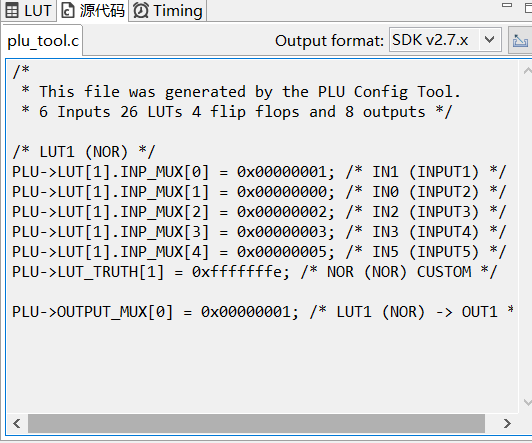

对 PLU 进行编程以实现特定的逻辑网络包括:写入各种真值表寄存器以指定每个 LUT 元素

要执行的逻辑功能;对输入多路复用器寄存器进行编程以选择呈现给每个 LUT 的五个输入;并编程输出多路复用器寄存器以选择 PLU 模块的八个主要输出。

所有这些寄存器的编程仅在初始化期间执行。

表 1. PLU 寄存器

6,PLU configuration tool 工具.

下载地址:

https://www.nxp.com.cn/search?keyword=PLU%20Configuration%20Tool&start=0

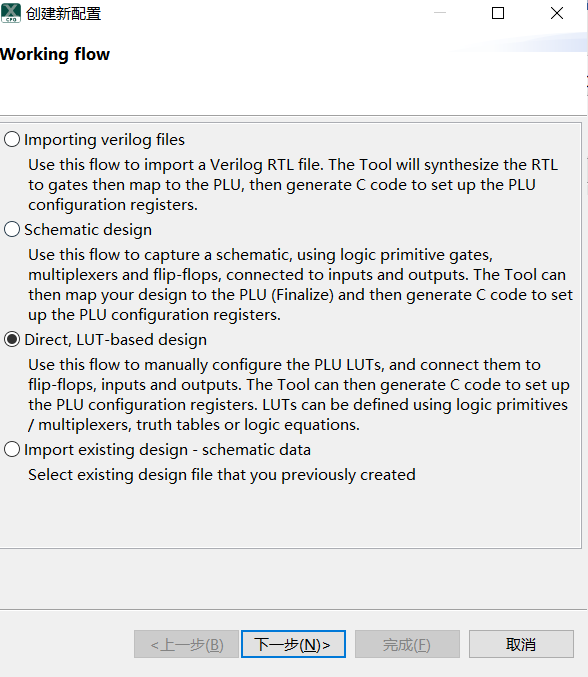

--PLU configuration tool支持图形化配置.

--支持从Verilog文件导入.

--支持从原理图设计.

--支持使用真值表.

示列选择使用LUT真值表.

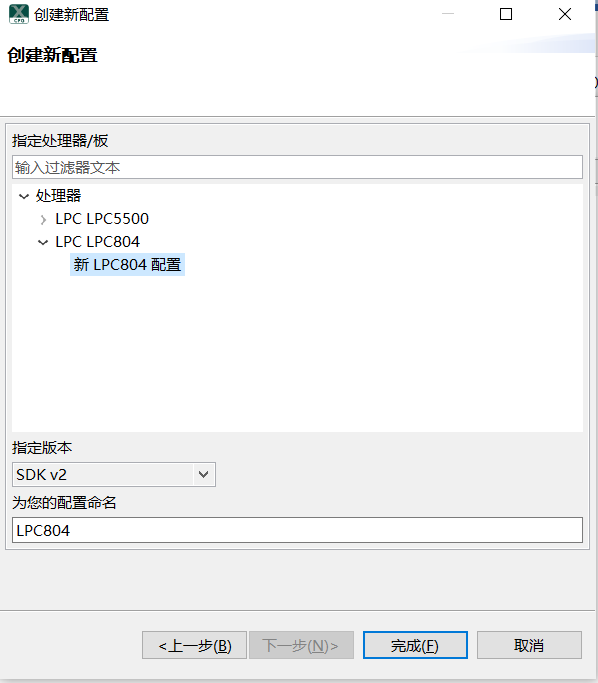

--PLU Config Tool支持的MCU系列:

I, LPC804

II, LPC5500(55S6x、55S2x/2x、55S1x/1x)系列

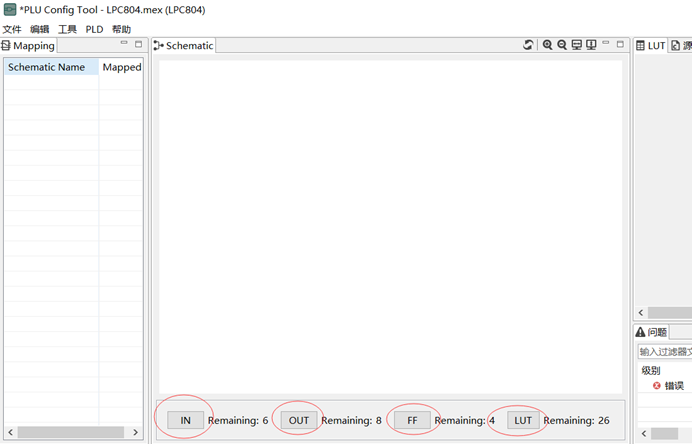

点完成后我们可以看到资源有:

--IN 输入 6个

--OUT输出 8个

--FF触发器 4个

--LUT真值表 26个

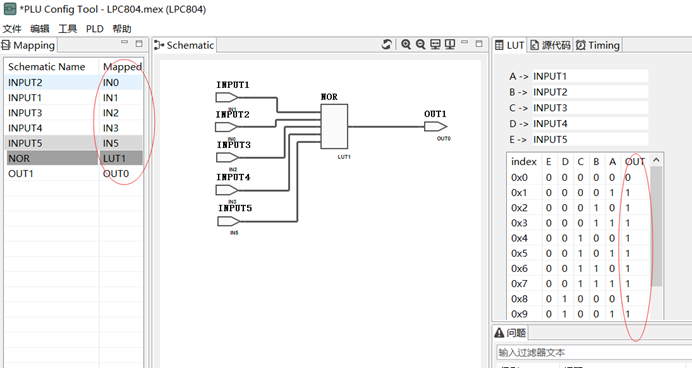

拖动配置完成一个工程案例.

--配置好Mapped 通道.

--配置LUT真值表.

工程完成后可以生成代码.

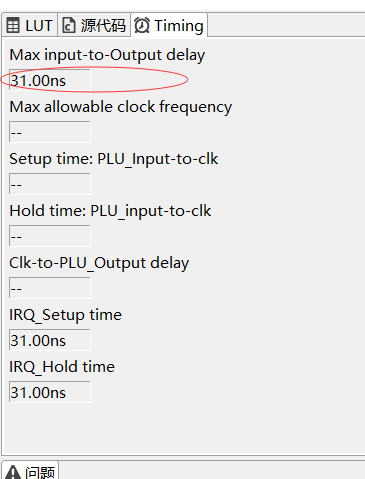

--可以看到Delay延时很小,相对MCU软件来设计做延时会降低很多,

--不需要MCU软件参与进来,纯硬件实现,减少MCU Loading.

--替换74系列逻辑,节省成本.

评论