一、前言

在《初识 i.MX RT 系列》中,我们了解了 i.MX RT 系列芯片的特点和芯片架构,本文将以 RT1060 为例介绍 i.MX RT 系列的存储器映射及它的区域功能划分,参考 NXP 《IMXRT1060RM》(参考手册)一起看,理解效果会更加。二、存储器映射

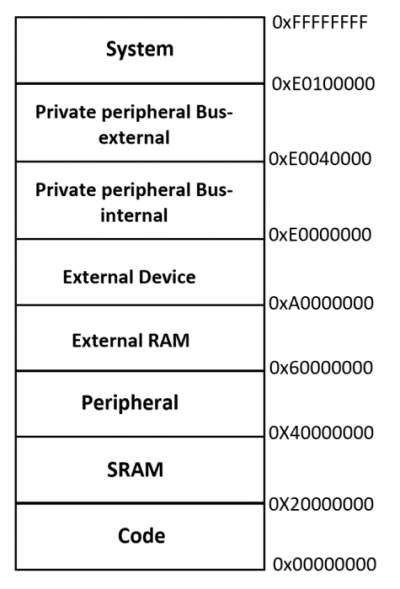

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射,具体见图 2.1 。如果给存储器再分配一个地址就叫存储器重映射。

图 2.1 Cotex-M7 存储器应用

2.1 存储器区域功能划分

在 4G 地址空间中, ARM 已经被分成了 8 块,并规定了用途,具体如下表格 2-1 所示,大部分块的大小都有 512MB 以上。

|

序号 |

用途 |

地址范围 |

|

Block 0 |

Code |

0x0000 0000 ~ 0x1FFF FFFF (512MB) |

|

Block 1 |

SRAM |

0x2000 0000 ~ 0x3FFF FFFF (512MB) |

|

Block 2 |

Peripheral 片上外设 |

0x4000 0000 ~ 0x5FFF FFFF (512MB) |

|

Block 3 |

External RAM(外部RAM) |

0x6000 0000 ~ 0x9FFF FFFF (1024MB) |

|

Block 4 |

External device(外部设备) |

0xA000 0000 ~ 0xDFFF FFFF (1024MB) |

|

Block 5 |

内核私有外设内部总线 |

0xE000 0000 ~ 0xE003 FFFF (256KB) |

|

Block 6 |

内核私有外设外部总线 |

0xE004 0000 ~ 0xE00F FFFF (768KB) |

|

Block 7 |

系统外设 |

0xE010 0000 ~ 0xFFFF FFFF (511MB) |

表 2-1 内核划分的存储器功能分类

在这 8 个 Block 中, Block0 、 Block1 及Block2 三个块是非常重要的。 Block0 一般采用 Flash 存储器存储程序代码, Block1 主要用于运行时的内存,一般用 SRAM 存储器,Block2 主要用于设计成片上外设,内核通过相应的地址访问片上外设。这三个 Block 具体区域的功能划分介绍如下:

(1)存储器Block0 内部区域功能划分

ARM 内核设计中, Block0 主要用于存储代码,在 i.MX RT1060 中,又把 Block0 细致地根据自己的芯片需求设计出具体的功能分配方案,如表 2-2 所示。

|

Start Address |

End Address |

Size |

Description |

|

1000_0000 |

1FFF_FFFF |

256MB |

Reserved |

|

0800_0000 |

0FFF_FFFF |

128MB |

Reserved |

|

0040_0000 |

07FF_FFFF |

124MB |

Reserved |

|

0028_0000 |

003F_FFFF |

1536KB |

Reserved |

|

0022_0000 |

0027_FFFF |

384KB |

ROMCP Reserved |

|

0020_0000 |

0021_FFFF |

128KB |

ROMCP |

|

0010_0000 |

001F_FFFF |

1MB |

ITCM Reserved |

|

0008_0000 |

000F_FFFF |

512KB |

ITCM Reserved |

|

0000_0000 |

0007_FFFF |

512KB |

ITCM |

表 2-2 RT1060 芯片对存储器 Block0 内部区域功能划分

首先是指令紧耦合内存(ITCM)。其中,“指令”指该内存专用于缓存指令,“紧耦合”指该内存与内核连接紧密,有非常高的访问速度。对于希望有着极高执行速度的代码,我们可以要求内核上电后把相应的代码从外部 FLASH 加载到 ITCM ,那么在运行时,代码的执行速度就不会因外部 FLASH 的访问速度而存在瓶颈。

其次是 ROMCP ,这是一小段 ROM 空间,用于存储芯片启动时的加载代码,即 bootloader ,它负责把指令从外部存储器加载至 ITCM 。

(2)储存器Block1 内部区域功能划分

Block1 用于设计片内的 SRAM ,也就是芯片运行时的内存,在 i.MX RT1060 芯片内部把这部分划分了两种 RAM 类型。Block1 内部区域的功能划分具体见表 2‑3。

|

Start Address |

End Address |

Size |

Description |

|

3000_0000 |

3FFF_FFFF |

256MB |

Reserved |

|

2040_0000 |

2FFF_FFFF |

252MB |

Reserved |

|

2030_0000 |

203F_FFFF |

512KB |

OCRAM Reserved |

|

2028_0000 |

202F_FFFF |

512KB |

OCRAM - FlexRAM |

|

2020_0000 |

2027_FFFF |

512KB |

OCRAM2 |

|

2010_0000 |

201F_FFFF |

1MB |

Reserved |

|

2008_0000 |

200F_FFFF |

512KB |

DTCM Reserved |

|

2000_0000 |

2007_FFFF |

512KB |

DTCM |

表 2-3 RT1060 芯片对存储器 Block1 内部区域功能划分

DTCM — 数据紧耦合内存,它和 ITCM 相似,有着极高的访问速度,不过它是专门用来存储程序数据的,即代码中变量的存储位置。

OCRAM — On-chip RAM,片上内存,可以把它理解为传统 MCU 的内部 SRAM ,可用于存储指令和数据(通用)。

(3)储存器Block2 内部区域功能划分

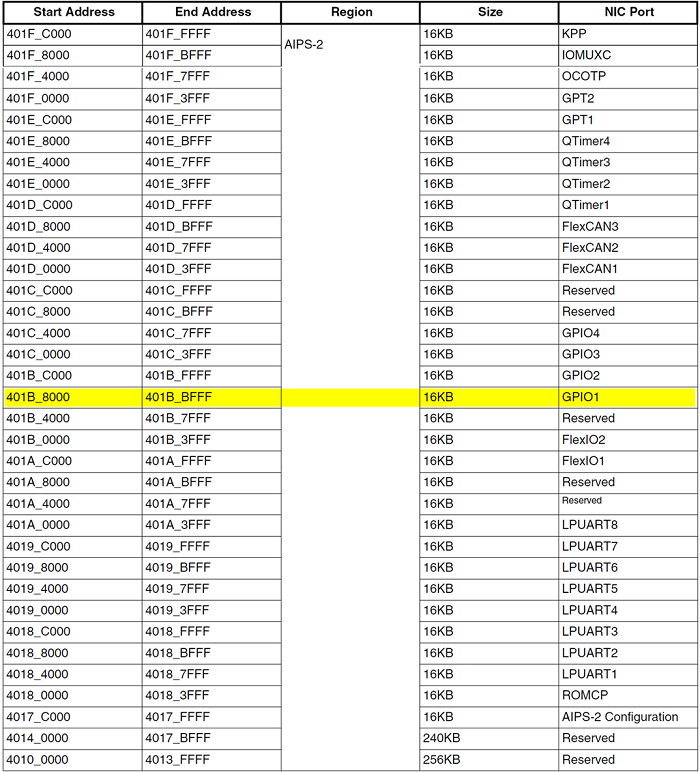

Block2 用于设计片内的外设,在 RT1060 芯片中,它的外设使用 5 条总线与内核进行连接,它们的地址分配情况见表格 2‑4(此处仅列出 AIPS 总线相关部分)。

|

Start Address |

End Address |

Size |

Description |

|

4200_0000 |

420F_FFFF |

1MB |

AIPS-5 |

|

4030_0000 |

403F_FFFF |

1MB |

AIPS-4 |

|

4020_0000 |

402F_FFFF |

1MB |

AIPS-3 |

|

4010_0000 |

401F_FFFF |

1MB |

AIPS-2 |

|

4000_0000 |

400F_FFFF |

1MB |

AIPS-1 |

表 2-4 RT1060 芯片对存储器 Block2 内部区域功能划分

AIPS 是 ARM IP Bus 的缩写,它一边与内核 AHB 总线连接,另一边与片上的各种外设连接, AIPS 1~5 连接了各种各样的外设,此处每条总线划分的地址范围各为 1MB ,内核根据地址可以访问相应总线下的外设,达到控制目的,下面是 AIPS-2 总线上外设的地址分配,见表 2‑5 。

表 2‑5 AIPS-2 总线地址分配

该表格的最右侧栏是挂在 AIPS-2 总线上的外设名称。本文主要介绍了 i.MX RT 系列芯片存储器映射及以 RT1060 为例介绍了存储器区域功能的划分,在下一篇博文《i.MX RT 系列之寄存器映射》中,将围绕 RT1060 探讨什么是寄存器,什么又是寄存器映射。

喜欢的点关注,关注博主不迷路~~

【参考文献】

- 《IMXRT1060RM》:MX RT1060 Processor Reference Manual (nxp.com)

- 《MX RT库开发实战指南——基于i.MXRT1052》:[野火]i.MX RT库开发实战指南——基于i.MXRT1052 文档 (embedfire.com)

评论