继上一篇关于 i.MX RT 的基本常用外设 LPI2C 的解析,这篇博文就带大家看看 i.MX RT 的 LPSPI。

SPI(Serial Peripheral Interface)总线是 Motorola 公司推出的一种高速、全双工的同步串行接口。SPI 的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或者多个从设备,并且在芯片的管脚上只占用四根线:SCK(时钟)、SDO(数据输出MOSI)、SDI(数据输入MISO)、CS(片选)。其中,SCK、SDO、CS 由主设备控制,SDI 由从设备控制。

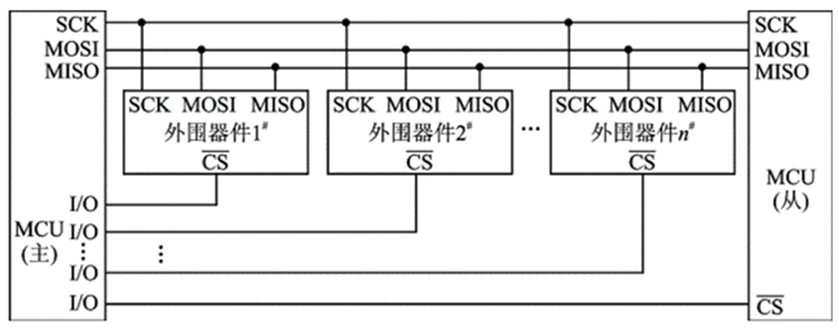

- SPI 硬件连接

通常情况下,只需要对四种信号进行编程即可控制 SPI 设备间的数据通信,设备间的硬件连接如下图所示:

SCK(Serial Clock):主要作用是 Master 向 Slave 传输时钟信号,控制数据交换的时机和速率;

SS/CS(Slave Select/Chip Select):用于 Master 片选 Slave,使被选中的 Slave 能够被 Master 访问;

SDO/MOSI(Serial Data Output/Master Out Slave In):在 Master 上也被称为 Tx-channel,作为数据的出口,主要用于 SPI 主设备发送数据;

SDI/MISO(Serial Data Input/Master In Slave Out):在 Master 上也被称为 Rx-channel,作为数据的入口,主要用于 SPI 主设备接收数据。

- SPI 总线的特征

SPI 总线的主要特征包括:

(1)高速:i.MX RT 的 LPSPI 最大速度可以达到 30MHz。

(2)同步:主设备会根据将要交换的数据来产生相应的时钟脉冲(Clock Pulse), 时钟脉冲组成了时钟信号(Clock Signal) , 时钟信号通过时钟极性 (CPOL) 和 时钟相位 (CPHA) 控制着 SPI 设备间何时数据交换以及何时对接收到的数据进行采样, 保证数据在两个设备之间是同步传输的.

(3)全双工:SPI可以全双工传输数据,即在主设备通过 MOSI 信号线向从设备发送数据的同时,也可以通过 MISO 信号线读取从设备发来的数据。

(4)非差分:SPI 的两根数据线并不是差分的形式。

(5) 主从机通讯模式:一主多从,主设备通过片选信号线来确定与哪个从设备通讯。

(6) 没有指定的流控制,没有应答机制确认是否接收到数据。

- SPI 总线传输时序

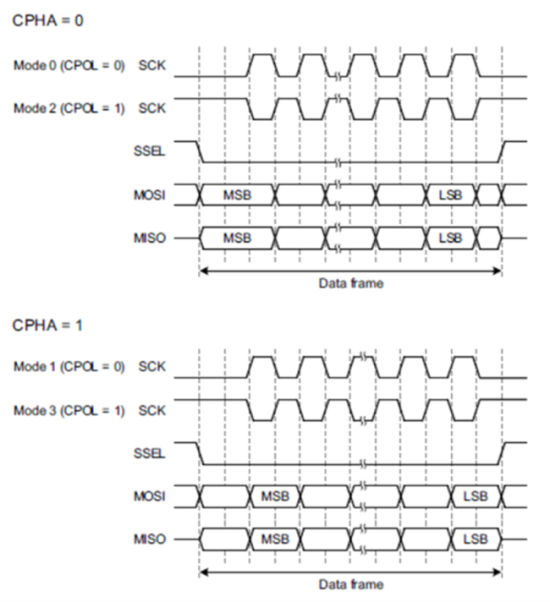

SPI 接口有四种不同的数据传输时序,取决于时钟极性(CPOL)和时钟相位(CPHA)的组合。

时钟极性(CPOL)决定 SPI 在空闲时,时钟信号是高电平还是低电平。CPOL = 0 时,SCK在空闲时为低电平,CPOL = 1 时,SCK在空闲时为高电平。

时钟相位(CPHA)决定 SPI 读取和发送数据的时钟沿。CPHA = 0 时,在每个周期的第一个时钟沿采样,CPHA = 1 时,在每个周期的第二个时钟沿采样。

SPI 的 4 种传输时序如下图所示:

(1) Mode 0:当 CPHA = 0,CPOL = 0 时,SPI 工作在模式 0,SCK 在总线空闲时保持低电平。MOSI 和 MISO 的数据在第一个 SCK 时钟沿跳变之前上线,当 SCK 上升沿时,MOSI 和 MISO 保持稳定状态;当 SCK 下降沿时,MOSI 和 MISO 改变状态。

(2) Mode 1:当 CPHA = 1,CPOL = 0 时,SPI 工作在模式 1,SCK 在总线空闲时保持低电平。MOSI 和 MISO 的数据在第二个 SCK 时钟沿跳变之前上线,当 SCK 上升沿时,MOSI 和 MISO 改变状态;当 SCK 下降沿时,MOSI 和 MISO 保持稳定状态。

(3) Mode 2:当 CPHA = 0,CPOL = 1 时,SPI 工作在模式 2,SCK 在总线空闲时保持高电平。MOSI 和 MISO 的数据在第一个 SCK 时钟沿跳变之前上线,当 SCK 上升沿时,MOSI 和 MISO 改变状态;当 SCK 下降沿时,MOSI 和 MISO 保持稳定状态。

(4) Mode 3:当 CPHA = 1,CPOL = 1 时,SPI 工作在模式 3,SCK 在总线空闲时保持高电平。MOSI 和 MISO 的数据在第二个 SCK 时钟沿跳变之前上线,当 SCK 上升沿时,MOSI 和 MISO 保持稳定改变状态;当 SCK 下降沿时,MOSI 和 MISO 改变状态。

- SPI 总线使用注意事项

(1) 由于 SPI 的最高工作速率由主设备的系统时钟频率决定,所以从设备的系统时钟频率必须要足够高。否则,如果 SCK 的速率太高,将导致从设备接收到的数据不正确。

(2) 主从模式的总线传输时序必须一致,即 CPOL 和 CPHA 的设置要一致。

(3) 在设置不当,或者受到外界干扰,数据传输难免会发生错误,或者有时软件对错误的种类判断不清,必须要有一种方法强制 SPI 接口从错误状态中恢复过来。在 SPI 不工作的时候,清除 SPI 内部所有的状态(专用寄存器除外)。如果软件在接收数据的时候能够发现数据有错误,无论是什么错误,都可以强制停止 SPI 的工作,重新进行数据传输。这样就可以避免错误一直持续下去。

(4) 在应用中,如果对数据的正确性要求较高,除了要在软件上满足 SPI 接口的时序要求外,还需要在软件上做适当的处理。

以上是我对 i.MX RT 的基本常用外设 SPI 的一些理解,希望对有这方面了解需求的你有些帮助。如果要获得更详尽的信息,可以参考 NXP 官网的 RT1060 参考手册数据手册。如果您还有更多的疑问,欢迎在下面评论区评论。

在后续的博文中,我会继续写一些关于 RT1060 的设计笔记,请多多来大大通关注我哦。

参考资料

- i.MX RT1060 Processor Reference Manual - https://www.nxp.com.cn/products/processors-and-microcontrollers/arm-microcontrollers/i-mx-rt-crossover-mcus/i-mx-rt1060-crossover-mcu-with-arm-cortex-m7-core:i.MX-RT1060?tab=Documentation_Tab

- i.MX RT1060 Processor Datasheet - https://www.nxp.com.cn/docs/en/nxp/data-sheets/IMXRT1060IEC.pdf

评论