0、前言

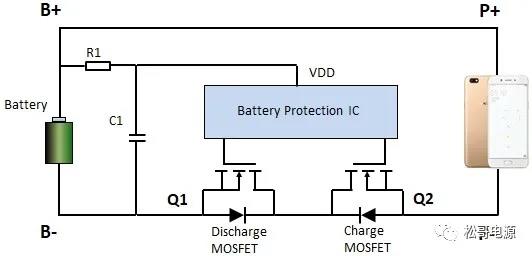

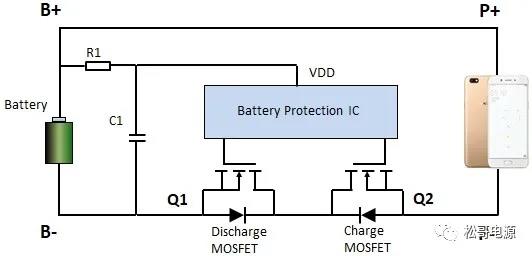

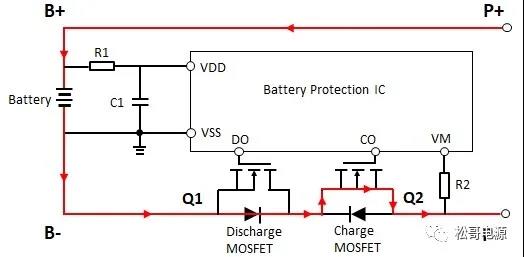

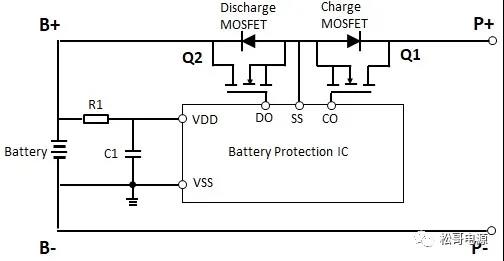

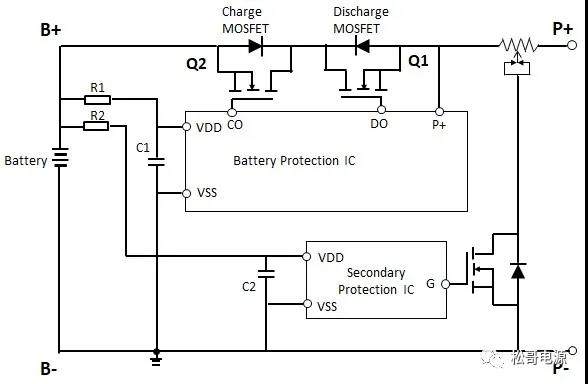

锂离子电池包的内部,电芯和输出负载之间要串联功率MOSFET,使用专用的IC控制MOSFET的开关,从而对电芯的充、放电进行管理,如图1所示。在消费电子系统中,如手机电池包,笔记本电脑电池包等,带有控制IC、功率MOSFETFE管以及其他电子元件的电路系统称为电池充放电保护板Protection Circuit Module (PCM),而对于动力电池的电池管理系统,则称为Battery Management System (BMS)。

图1:电池充放电保护板电路结构

在电池充放电保护板PCM中,充、放电分别使用一颗功率MOSFET,背靠背的串联起来。功率MOSFET管背靠背的串联的方式有二种:一种是二颗功率MOSFET的漏极连接在一起;另一种是二颗功率MOSFET的源极连接在一起。功率MOSFET管放置的位置也有二种方式:一种是二颗功率MOSFET放在电池的负端,也就是所谓的“地端”、低端(Low Side);另一种是二颗功率MOSFET放在电池的正端,高端(High Side)。功率MOSFET背靠背连接的不同方式、以及放在不同的位置,都有各自的优缺点,对应着系统的不同要求。

PCM需要低的导通电阻,同时要控制成本,通常采用N沟道的功率MOSFET。P沟道的功率MOSFET放在高端驱动简单灵活,有少量的应用也会采用P沟道MOSFET。但是,P沟道MOSFET的导通电阻很难做低,成本高,选型的型号和供应厂家也受限,因此,N沟道的功率MOSFET依然是主流的方案。

如果功率MOSFET有非常严格的体积和尺寸的要求,需要将二个功率MOSFET集成到一个芯片上,由于通用的功率MOSFET是垂直结构,衬底是漏极D,因此,使用漏极的背靠背结构就可以采用这样工艺。采用水平(横向)结构的功率MOSFET,可以使用漏极、或源极的背靠背结构,但是,水平结构的功率MOSFET导通电阻很难做低,做低导通电阻成本也高。

1、背靠背功率MOSFET配置方式及工作原理

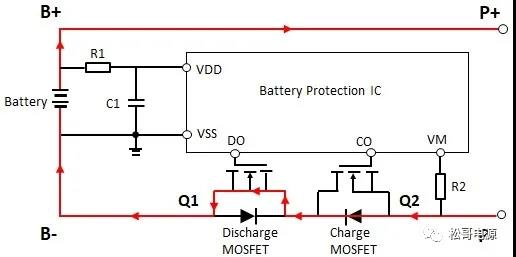

1.1 地端、漏极背靠背的工作原理

充、放电管理的二颗N沟道的功率MOSFET放在地端,漏极背靠背连接在一起,是PCM常用的方案之一,如图2所示。其中,Q1为电池放电的功率MOSFET,Q2为电池充电的功率MOSFET,B+为电池(电芯)的正端,B-为电池(电芯)的负端,P+为电池包的正端,P-为电池包的负端,VSS为电池保护管理IC的地,电池的负端、VSS和Q1的源极连接在一起。PCM电路板工作前,Q1、Q2都是关断的。

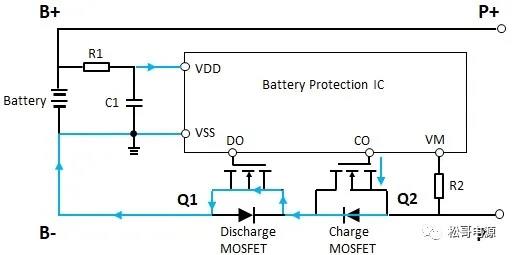

充电的时候,控制IC给出充电功率MOSFET管Q2的栅极驱动信号CO,Q2栅极驱动信号路径为:外部充电电路的正端->P+->B+->R1->VDD->CO驱动输出->Q2栅极->Q2源极->P-->外部充电电路的负端,形成完整的驱动回路,Q2开通,如图3所示。

锂离子电池包的内部,电芯和输出负载之间要串联功率MOSFET,使用专用的IC控制MOSFET的开关,从而对电芯的充、放电进行管理,如图1所示。在消费电子系统中,如手机电池包,笔记本电脑电池包等,带有控制IC、功率MOSFETFE管以及其他电子元件的电路系统称为电池充放电保护板Protection Circuit Module (PCM),而对于动力电池的电池管理系统,则称为Battery Management System (BMS)。

图1:电池充放电保护板电路结构

在电池充放电保护板PCM中,充、放电分别使用一颗功率MOSFET,背靠背的串联起来。功率MOSFET管背靠背的串联的方式有二种:一种是二颗功率MOSFET的漏极连接在一起;另一种是二颗功率MOSFET的源极连接在一起。功率MOSFET管放置的位置也有二种方式:一种是二颗功率MOSFET放在电池的负端,也就是所谓的“地端”、低端(Low Side);另一种是二颗功率MOSFET放在电池的正端,高端(High Side)。功率MOSFET背靠背连接的不同方式、以及放在不同的位置,都有各自的优缺点,对应着系统的不同要求。

PCM需要低的导通电阻,同时要控制成本,通常采用N沟道的功率MOSFET。P沟道的功率MOSFET放在高端驱动简单灵活,有少量的应用也会采用P沟道MOSFET。但是,P沟道MOSFET的导通电阻很难做低,成本高,选型的型号和供应厂家也受限,因此,N沟道的功率MOSFET依然是主流的方案。

如果功率MOSFET有非常严格的体积和尺寸的要求,需要将二个功率MOSFET集成到一个芯片上,由于通用的功率MOSFET是垂直结构,衬底是漏极D,因此,使用漏极的背靠背结构就可以采用这样工艺。采用水平(横向)结构的功率MOSFET,可以使用漏极、或源极的背靠背结构,但是,水平结构的功率MOSFET导通电阻很难做低,做低导通电阻成本也高。

1、背靠背功率MOSFET配置方式及工作原理

1.1 地端、漏极背靠背的工作原理

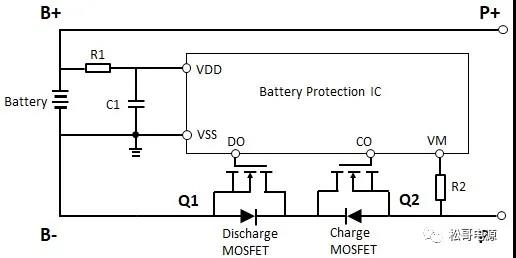

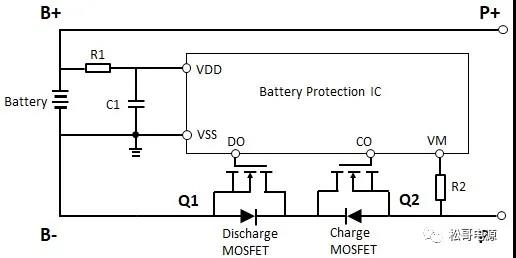

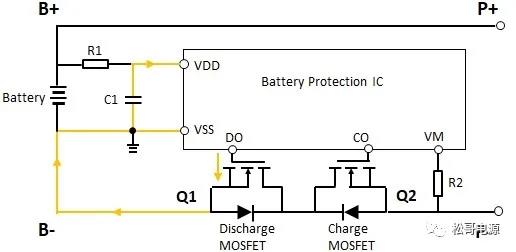

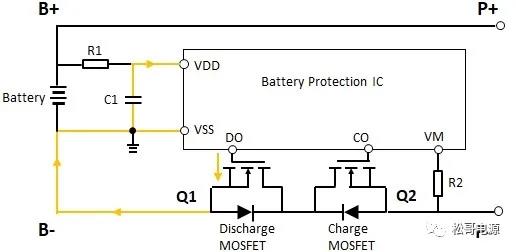

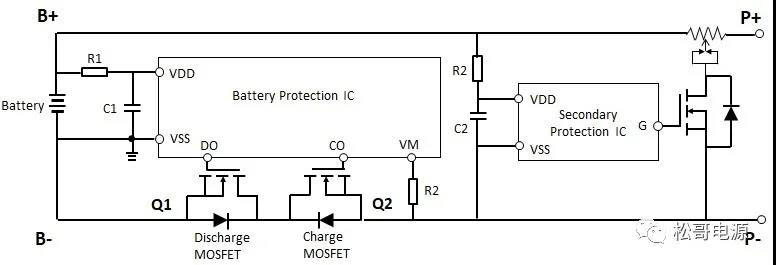

充、放电管理的二颗N沟道的功率MOSFET放在地端,漏极背靠背连接在一起,是PCM常用的方案之一,如图2所示。其中,Q1为电池放电的功率MOSFET,Q2为电池充电的功率MOSFET,B+为电池(电芯)的正端,B-为电池(电芯)的负端,P+为电池包的正端,P-为电池包的负端,VSS为电池保护管理IC的地,电池的负端、VSS和Q1的源极连接在一起。PCM电路板工作前,Q1、Q2都是关断的。

图2:功率MOSFET放地端、漏极背靠背电路图

(1)充电

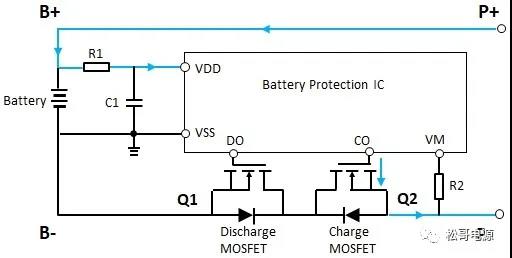

充电的时候,控制IC给出充电功率MOSFET管Q2的栅极驱动信号CO,Q2栅极驱动信号路径为:外部充电电路的正端->P+->B+->R1->VDD->CO驱动输出->Q2栅极->Q2源极->P-->外部充电电路的负端,形成完整的驱动回路,Q2开通,如图3所示。

图3:充电,CO输出Q2的驱动信号

Q2开通后,充电电流的路径为:P+->B+->B-->Q1体内寄生二极管->Q2沟道->P-,电池就可以充电,如图4所示。

图4:Q2导通的充电回路

为了减小Q1的损耗,Q2开通后,控制IC给出放电功率MOSFET管Q1的栅极驱动信号DO开通Q1,Q1的导通电阻RDSON低,导通损耗远低于体内寄生二级管的损耗,从而提高充电的效率。Q1驱动信号路径为:VDD->DO驱动输出->Q1栅极->Q1源极->B-->VSS,形成完整的驱动回路,Q1开通,如图5所示。

图5:充电,Q2导通后,DO输出Q1的驱动信号

Q2、Q1同时处于导通状态,充电电流的路径为:P+->B+->B-->Q1沟道->Q2沟道->P-,如图6所示。

图6:Q2、Q1导通的充电回路

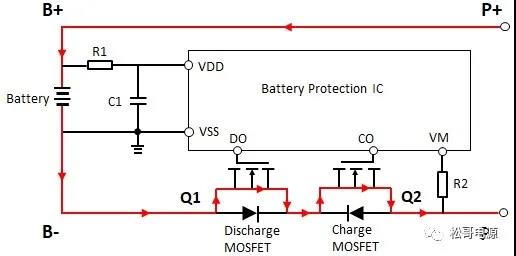

(2)放电

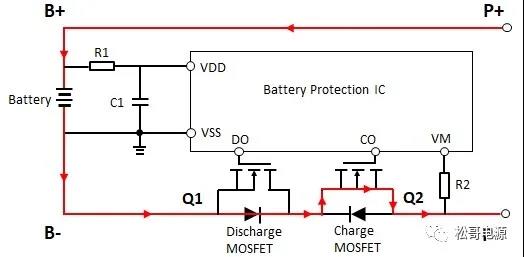

放电的时候,控制IC给出放电功率MOSFET管Q1的栅极驱动信号DO,Q1栅极驱动信号路径为:VDD->DO驱动输出->Q1栅极->Q1源极->B-->VSS,形成完整的驱动回路,就可以打开Q1,如图7所示。

图7:放电,DO输出Q1的驱动信号

Q1开通后,放电的电流路径为:P-->Q2体内寄生二极管->Q1沟道->B-->B+->P+,电池就可以放电,如图8所示。

图8:Q1开通的放电回路

为了减小Q2的损耗,Q1开通后,控制IC给出充电功率MOSFET管Q2的栅极驱动信号CO开通Q2,Q2的导通电阻RDSON低,导通损耗远低于体内寄生二级管的损耗,从而提高电池使用的时间。Q2驱动信号路径为:VDD->CO驱动输出->Q2栅极->Q2源极->Q2体内寄生二极管->Q1沟道->B-->VSS,形成完整的驱动回路,Q2开通,如图9所示。

图9:放电,Q1导通后,CO输出Q2的驱动信号

Q1、Q2同时处于导通状态,放电电流的路径为:P-->Q2沟道->Q1沟道->B-->B+ ->P+,如图10所示。

图10:Q1、Q2导通的放电回路

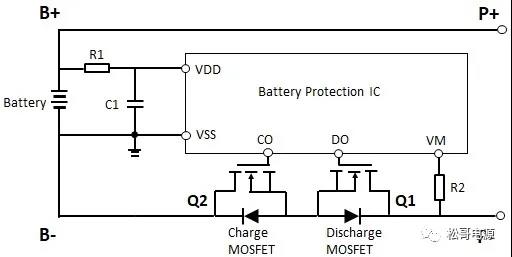

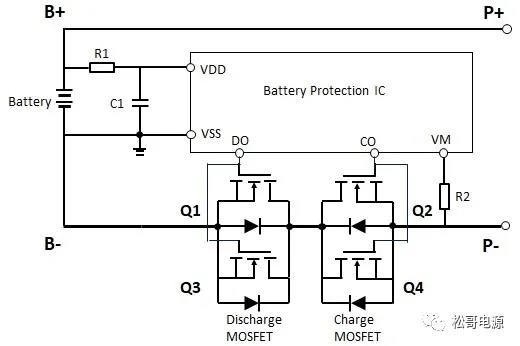

1.2 地端、源极背靠背

N沟道的二颗功率MOSFET源极背靠背连接在一起,放在地端,如图11所示,这种结构在PCM里面应用较少,在一些负载开关以及通信系统的热插拔电路中,才有使用。

图11:功率MOSFET源极背靠背连接

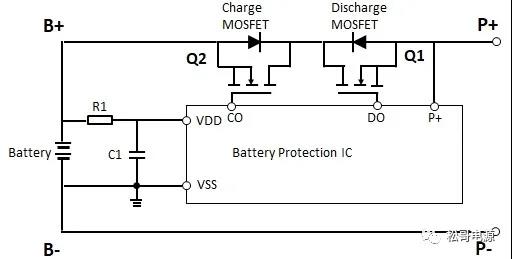

1. 3 高端、漏极背靠背的工作原理

充、放电管理的二颗N沟道的功率MOSFET放在电源端,也就是高端,漏极背靠背连接在一起,也是是PCM常用的方案之一,如图12所示。其中,Q1为电池放电的功率MOSFET,Q2为电池充电的功率MOSFET。

N沟道的二颗功率MOSFET放在高端,MOSFET开通时,栅极G的电压要高于源极S的电压,源极S的电压为输入电源电压,因此,需要二个的充电泵,叠加在输入电源电压(MOSFET的源极S)上,对它们进行浮驱。

图12:功率MOSFET放在高端,漏极背靠背

1.4 高端、源极背靠背的工作原理

充、放电管理的二颗N沟道的功率MOSFET放在电源端,也就是高端,源极背靠背连接在一起,如图13所示。N沟道的二颗功率MOSFET共源极,因此,只需要一个的充电泵,就可以对它们进行浮驱,这种结构应用于一些负载开关,如笔记本电脑内部输入电源电压的负载开关。

图13:功率MOSFET放在高端,源极背靠背

2、大电流多管并联

目前,为了提高电子系统的使用时间和待机时间,电池的容量越来越大,如3000mAh到5000mAh,甚至更大,为了缩短充电时间,提高充电的速度,通常使用快充,也就是使用更大的充电电流,如4A、5A、6A,甚至高到8A,对电池充电,这样PCM内部功率MOSFET的功耗非常大,温度非常高。为了降低功率MOSFET的温升,满足热设计的要求,保证功率MOSFET可靠运行,就会使用二个或多个功率MOSFET并联工作,如图14所示。

图14:大电流多管并联

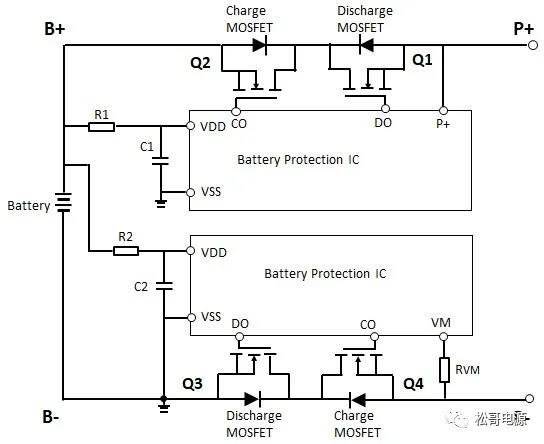

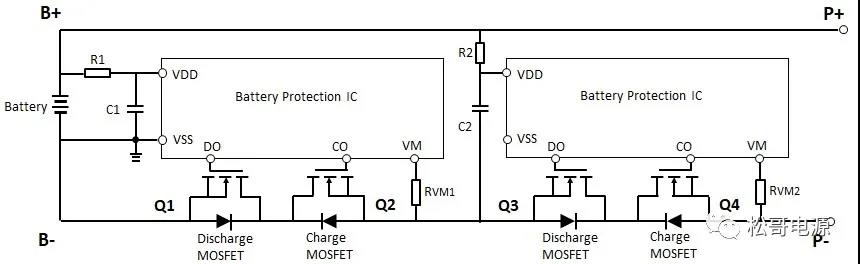

3、冗余设计

根据安规LPS要求,如果PCM内部的功率MOSFET发生损坏而短路,那么接上充电器,输入电压直接加在电池上,可能发生危险。为了提高系统的安全,可以再串联一组背靠背的功率MOSFET,或使用其他的方案,形成冗余设计,当一级保护失效后,还有另一级保护,如图15、图16、图17、图18所示。

图15:二组功率MOSFET,一组放在高端,一组放在低端

图16:二组功率MOSFET放在低端

图17:功率MOSFET放在高端,电子保险丝

图18:功率MOSFET放在低端,电子保险丝

评论