- 概述

本文档旨在帮助硬件工程师设计和测试i.MX 8M Mini系列处理器。文档提供了有关电路板布局和设计注意事项核对清单的示例,旨在确保首次成功,同时还提供了避免电路板启动问题的一些解决方案。

工程师应了解电路板布局和电路板硬件术语。

本指南随相关设备特定的硬件文档一起发布,如数据手册、参考手册、应用笔记等。所有这些文档均可从www.nxp.com/imx8mminievk获取。

1.1. 支持的器件

本文档支持i.MX 8M Mini(14 x 14 mm封装)。

1.2. 重要参考资料

本指南是对i.MX 8M Mini系列芯片参考手册和数据手册的补充。关于焊接期间的回流焊温度曲线和热限值信息,请参见《一般焊接温度工艺指南》(文档AN3300)。这些文档可从www.nxp.com/i.MX8MMINI获取。

1.3. 补充参考资料

1.3.1. 一般信息

下述文档介绍了Arm®处理器架构和计算架构。

- 有关Arm Cortex®-A35处理器的信息,请参见: www.arm.com/products/processors/cortex-a/cortex-a35-processor.php

- 有关Arm Cortex-A53处理器的信息,请参见: www.arm.com/products/processors/cortex-a/cortex-a53-processor.php

- 有关Arm Cortex-A72处理器的信息,请参见: www.arm.com/products/processors/cortex-a/cortex-a72-processor.php

- 有关Arm Cortex-M4F处理器的信息,请参见: www.arm.com/products/processors/cortex-m/cortex-m4-processor.php

- 计算机架构:定量方法(第4版)—作者:John L. Hennessy和David A. Patterson

- 计算机组成和设计:硬件/软件接口(第2版),作者:David A. Patterson和John L. Hennessy

下述文档介绍了高速电路板设计:

- 一举成功—高速PCB和系统设计实用手册—第1和2卷—作者:Lee W. Ritchey(出版社:Speeding Edge)—ISBN 0-9741936-0-72

- 信号和电源完整性分析(第2版)—作者:Eric Bogatin(出版社:Prentice Hall)—ISBN 0-13-703502-0

- 高速数字设计—黑魔书—作者:Howard W. Johnson和Martin Graham(出版社:Prentice Hall)—ISBN 0-13-395724-1

- 高速信号传播—高级黑魔书—作者:Howard W. Johnson和Martin Graham(出版社:Prentice Hall)—ISBN 0-13-084408-X

- 高速数字系统设计—互连理论和设计实践手册—作者:Hall、Hall和McCall(出版社:Wiley Interscience,2000年)—ISBN 0-36090-2

- 信号完整性问题和印刷电路板设计—作者:Doug Brooks(出版社:Prentice Hall)ISBN 0-13-141884-X

- PCB设计:在真实世界里的EMI控制—作者:Bruce R. Archambeault(克吕 韦尔学术出版集团)—ISBN 1-4020-7130-2

- 干扰规范的数字设计—EMI抑制实用手册—作者:David L. Terrell和R. Kenneth Keenan(出版社:Newnes Publishing)—ISBN 0-7506-7282-X

- 电磁兼容工程—作者:Henry Ott(第1版,出版社:John Wiley and Sons)—ISBN 0-471-85068-3

- 电磁兼容导论—作者:Clayton R. Paul(出版社:John Wiley and Sons)—ISBN 978-0-470-18930-6

- 仪器的接地和屏蔽技术—作者:Ralph Morrison(第5版,出版社:John Wiley and Sons)—ISBN 0-471-24518-6

- 产品设计中的EMC技术—作者:Tim Williams(出版社:Newnes Publishing)—ISBN 0-7506-2466-3

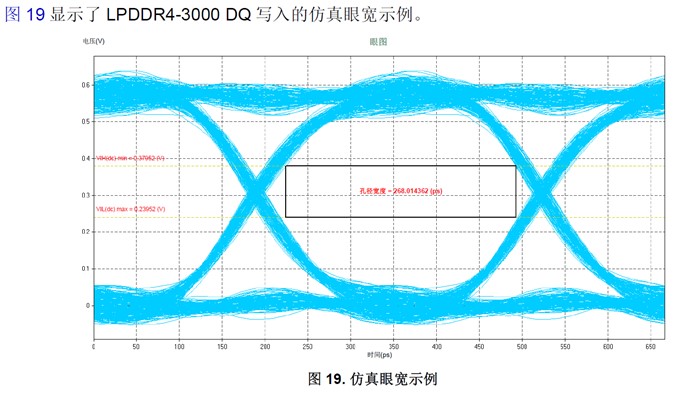

2.4.5. i.MX 8M Mini DDR SI仿真指南

仿真架构包括DDR控制器(即i.MX 8M Mini处理器)、PCB和DRAM器件。i.MX 8M Mini处理器的IBIS型号可从恩智浦购买。DRAM器件IBIS型号必须从存储器供应商处购买。

本节介绍如何使用i.MX 8M Mini检查DDR设计布局的SI性能。

- 首先,执行S参数提取:

— 需要2.5D全波提取工具,如Cadence的PowerSI。

— 将提取带宽设置为20 GHz。

— 端口参考阻抗:信号端口为50 Ω,电源端口为0.1 Ω。

— 耦合模式:将上升时间置为20 ps,耦合系数置为1%。

- 其次,执行时域仿真:

— 激励模式:500位随机代码和不同的模式,用于相同字节内的各个信号。

— 理想电源。

— 裸片上的探针。

— 在慢速角仿真(最坏情况)。

— 通过与定时参考(DQS/CLK)保持一致触发眼图波形。

仿真完成后,找出仿真的最差眼宽并与下列要求进行比较,看看仿真是否能够通过:

- 对于LPDDR4-3000

— DQ写入:VREF ±70mV时的眼宽应超过248 ps。

— DQ读取:VREF ±70mV时的眼宽应超过201 ps。

— Cmd/Addr/Ctrl:VREF ±77.5mV时的眼宽应超过563 ps。

- 对于DDR4-2400

— DQ写入:VREF ±65mV时的眼宽应超过276 ps。

— DQ读取:VREF ±70mV时的眼宽应超过225 ps。

— Cmd/Addr/Ctrl:在阈值时的眼宽应超过579 ps。

- 对于DDR3L-1600

— DQ写入:在阈值时的眼宽应超过395 ps。

— DQ读取:641.5 ±70mV时的眼宽应超过370 ps。

— Cmd/Addr/Ctrl:在阈值时的眼宽应超过727 ps。

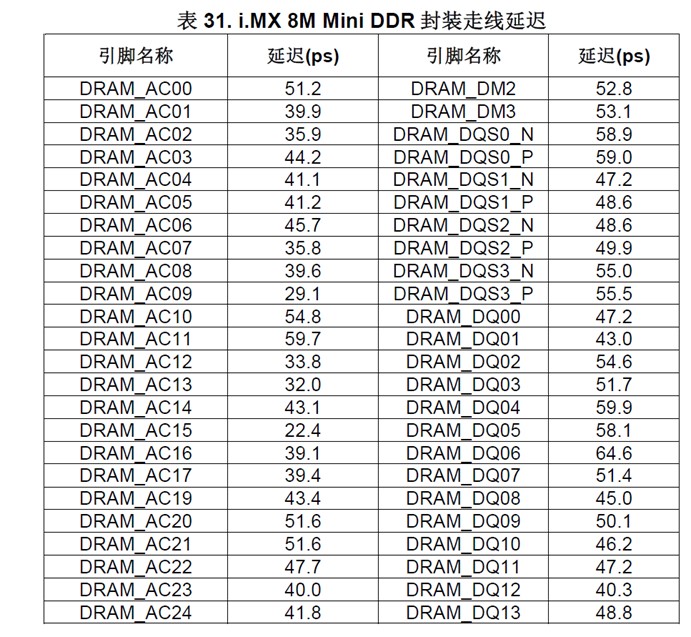

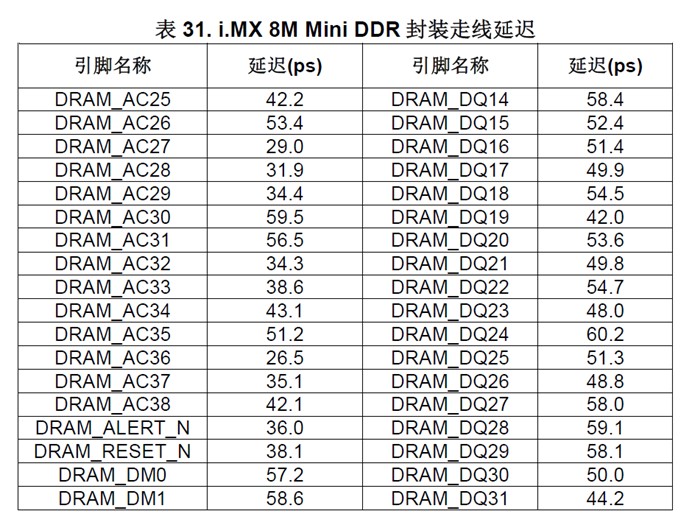

2.4.6. i.MX 8M Mini DDR封装延迟

对LPDDR4/DDR4路由执行所需的延迟匹配时,匹配计算中应考虑包含i.MX 8M Mini封装中的焊线。表31列出了从裸片I/O至封装引脚的传播/飞行时间。

2.4.7. 高速路由建议

下面列出了高速信号的路由走线。传播延迟和阻抗控制应匹配,以确保与器件正确通信。

- 高速信号(DDR、PCIe、RGMII、MIPI等)不得跨越参考平面中的间距。

- 避免在参考平面中形成插槽、空隙和间隔。检查通孔的定位,以确保不会意外形成间隔/空隙(即将通孔间隔开,以消除这种可能性)。

- 在不同参考接地层之间转换时,确保接地缝合通孔与高速信号上的信号层转换通孔的间隔不超过50 mil。

- 固态GND平面必须直接位于与元件和走线相关的晶体下方。

- 同一层的时钟或选通与相邻走线的间距至少为参考平面2.5倍的高度,以减少串扰。

- 所有同步接口应进行适当的总线延迟匹配。

- 差分对的真互补信号延迟必须匹配为1ps以内。

參考資料:

NXP官網:

- https://www.nxp.com/docs/en/user-guide/IMX8MMEVKBHUG.pdf

- https://www.nxp.com/docs/en/quick-reference-guide/8MMINILPD4EVKBQSG.pdf

- https://www.nxp.com/webapp/Download?colCode=L5.4.24_2.1.0_LINUX_DOCS

- https://www.nxp.com/webapp/Download?colCode=8MMINILPD4-CPU2-DESIGNFILES

- https://www.nxp.com/webapp/Download?colCode=IMX8MMRM

- https://www.nxp.com/document/guide/get-started-with-the-i-mx-8m-mini-evk:GS-iMX-8M-Mini-EVK

评论