低压差稳压电源LDO芯片设计(2)浅谈数字LDO及其LCO

原创 Yan 路延 延路的笔记 2019-05-26

收录于话题#电源管理芯片设计8个内容

这一篇短文里面的大部分工作和思路由黄沫博士提出,我只是加以总结。并再次感谢帮我整理资料的殷晗同学。

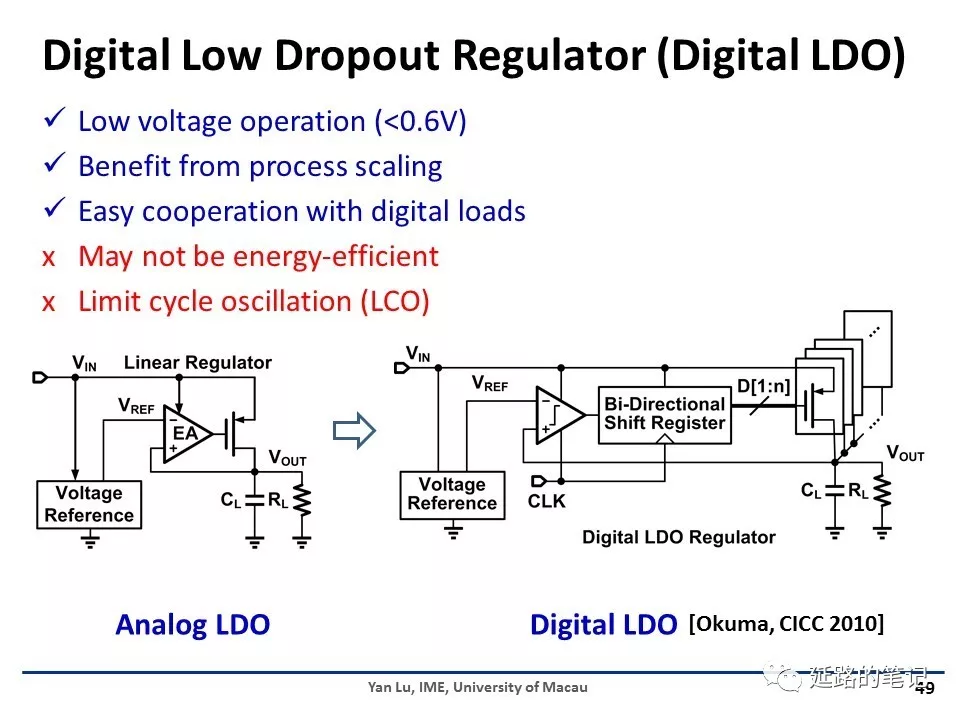

数字LDO的基本思想非常简单。模拟LDO中的大功率管在这里被分割成许多功率开关,这些开关由双向移位寄存器控制。双向移位寄存器从比较器的输出端得到输入信号。时钟控制的比较器在每一个时钟周期开始时比较VOUT与VREF的值,并指示移位寄存器每个时钟周期打开或关闭一个功率开关。

相较于模拟LDO,数字LDO可以在低输入电压下工作(比如小于0.6V),在这一低电压下,模拟LDO较难达到很高的增益。数字LDO的另一个优点是它的性能参数随使用工艺尺寸变小而等比例变好,和工艺节点之间的迁移便利性。另外,数字LDO可以与数字负载相互配合来对负载的变化进行提前响应。

但是,传统的数字LDO的能量利用率并不高,这是因为每一个时钟周期内数字LDO仅仅改变一个开关的状态。而为了达到更高的输出精度,我们需要使用成百上千个开关,这又会导致响应速度十分缓慢。另外,由于有限的输出精度,即使在负载电流不变的情况下,数字控制码也会在附近的码值间振荡。这就是所谓的有限周期振荡(Limit-Cycle Oscillation,LCO),该现象在数字控制系统中普遍存在。

这是最早一篇提出这个数字LDO架构的论文,由日本团队在CICC2010上发表。在最近5年中被广泛引用。

可能有人马上会问,为什么不使用二进制编码而使用温度计编码来达到快速响应的目的呢?使用二进制码确实可以使响应变得快很多。但是,使用二进制码也有许多缺点。第一,需要使用更多用作多级ADC的比较器,这会消耗更多的转换能量。第二,在最高位发生变化时,比如说,从0111变化到1000,所有的开关状态都会发生改变,这也会消耗大量的能量,而就数字码本身而言,却仅仅是从7到8上升了一个数字而已。同时,如果二进制位没能在同一时刻发生改变,最高位的变化会导致很严重的输出毛刺。因此,对于数字LDO来说,使用温度计码更为合适。

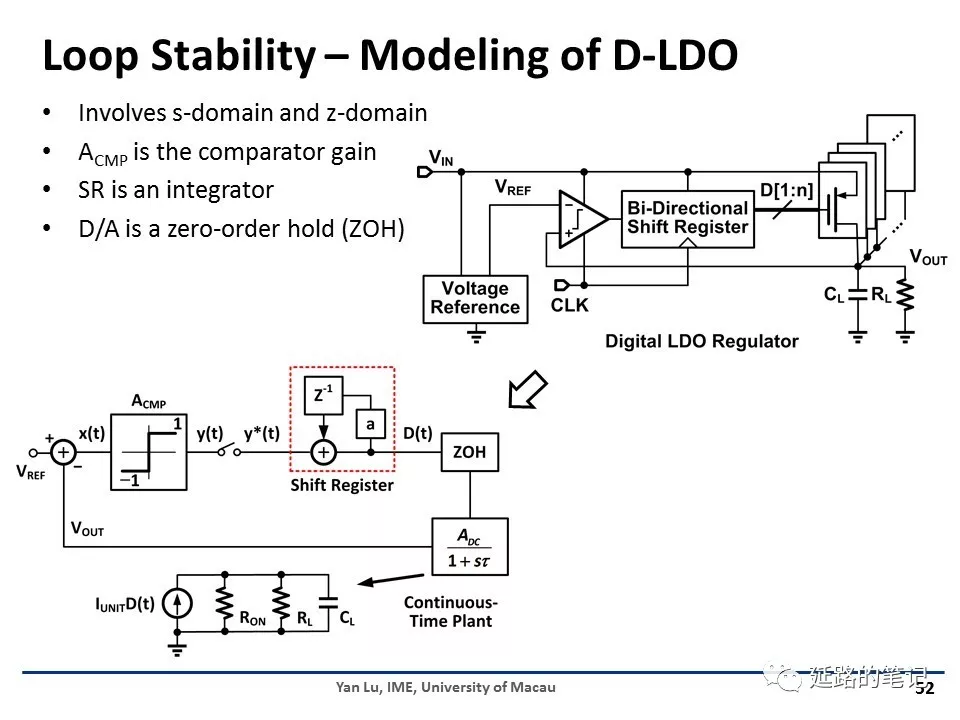

数字LDO的环路稳定性分析方法与模拟LDO类似,但是要更复杂一些,因为它还包括了s域和z域的转换。比较器是一个1-bit ADC,可以建模为一个增益受输入控制的放大器和一个采样-保持开关。移位寄存器是一个积分器,累积了过去的所有信息,因此,在小信号模型中,移位寄存器贡献了一个频率位于DC的极点。移位寄存器可以被设置成每周期移动一位或者多位,因此在模型中存在一个增益因子a。数字信号通过功率管开关阵列(相当于一个DAC)被转换回模拟域,这可以用零阶保持(Zero-order Hold,ZOH)来建模。另外,与模拟LDO类似,输出节点提供一个极点。

数字LDO小信号模型的一个特性是其ADC的增益会发生变化,且这一变化高度取决于输入信号。因为ADC的输出一定是0和1,所以当输入信号很接近比较阈值的时候,等效增益就非常大。反之,当输出信号远离比较阈值的时候,等效增益就减小了。因此,DLDO的单位增益频率也会随着输入信号的变化而变化。当等效增益非常大(即VOUT与VREF非常接近)时,环路会发生振荡,这是因为单位增益频率超过了输出极点的频率。但是振荡过程中,VOUT又会时而远离VREF,时而接近VREF,也就是这个振荡是相对可控的。当VOUT远离VREF的时候,这个系统趋于稳定,当VOUT接近VREF的时候,系统趋于振荡。所以这个现象叫“Limit-Cycle” Oscillation。这是LCO现象的另一种解释方式。

如上所述,LCO来源于精度有限的ADC(比较器)的量化误差。传统上大家定义了LCO的“mode”来把LCO频率和时钟频率联系起来。如果数字码在两个相邻的码间振荡,我们说这是模式1的LCO。如果码在三个码之间振荡,则为模式2。LCO还有模式3,4,5甚至更高。显然,在其他条件相同的情况下,更高模式下的输出电压振荡幅度更大。

LCO的模式和幅度取决于几个因素。较高的时钟频率FS会导致mode更大,因为比较器将在VOUT振荡的一个周期内会多次采样VOUT。另一方面,如果LCO的mode不变,较慢的FS会使得开关管单位电流对节点的充电/放电时间变长,这将导致LCO幅度较大。当LCO mode相同时,LCO的幅度也取决于负载条件。轻负载电流会使得等效负载电阻RL变大,并因此导致更大的LCO幅度。因为一个bit的振荡幅度等于Iunit x RL,Iunit为单位数字电流。

降低LCO幅度有以下解决方案。第一,通过使用多位ADC,使得量化误差变小,也使得数字LDO环路增益受VOUT的影响变小,环路稳定性也会变得好一点。但是这种方法中多位ADC需要消耗更大的功率,电路模块也会更复杂。第二,Deadzone(DZ)比较器是使用两个比较器和两个边界比较值。当VOUT在DZ范围内时,数字控制器不发生开关活动,从而避免在DZ的LCO。但接下来的问题是如何定义合适的DZ范围。如果DZ范围太大,会降低输出精度,如果DZ太小,则依然会发生LCO。第三种降低LCO振幅的方法在论文[Huang,TCAS-II,2016]中有所介绍,即与主环路并联地添加一条前馈(FF)路径,以保证LCO模式等于1。

这里显示了带有一个附加的与主环路并联的简单前馈(FF)路径的数字LDO的原理框图,添加该路径的目的是为了保持LCO模式等于1。该FF路径可以立即对比较器的输出产生响应,在频域内则等效为一个零点。通过将辅助电源开关的强度β设定为主电源开关的2倍,可以获得具有最小LCO幅度且模式等于1的LCO。

这里显示了带前馈和不带前馈的LCO mode大小仿真。使用带前馈路径的方法后,在很大的负载电流范围内,LCO mode都保持在1。

最后,最常见的一个问题是:数字LDO除了要考虑LCO外,还要像模拟LDO那样考虑稳定性的问题吗?数字LDO的LCO和模拟LDO的振荡是同一个问题吗?

我个人认为要考虑,但是它们是同一个问题,对于同一个数字LDO,如果你给它更高的时钟频率,它会振荡得更大。如果你把数字电流步长变大,它会振荡得更大。如果你让它负载电流变小,它会振荡得更大。如果振荡幅度太大,超出了你比较器的deadzone,那它就一直在deadzone上下大幅振荡了。你还是得通过调整时钟频率,数字电流步长这两个参数让你的数字LDO的LCO幅度不超过你的deadzone。

以下是我们组在数字LDO方面发表的一些论文,由于本公众号没有评论功能,欢迎email讨论。(这个系列还有后续,敬请期待)

[1] M. Huang, Y. Lu, S. W. Sin, S. P. U, and R. P. Martins, “A Fully Integrated Digital LDO With Coarse-Fine-Tuning and Burst-Mode Operation,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 63, no. 7, pp. 683–687, Jul. 2016.

[2] M. Huang, Y. Lu, S. W. Sin, S. P. U, R. P. Martins, and W. H. Ki, “Limit Cycle Oscillation Reduction for Digital Low Dropout Regulators,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 63, no. 9, pp. 903–907, Sep. 2016.

[3] M. Huang, Y. Lu, S. P. U, and R. P. Martins, “20.4 An output-capacitor-free analog-assisted digital low-dropout regulator with tri-loop control,” in IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 342–343.

[4] M. Huang, Y. Lu, S. U, and R. P. Martins, “An Analog-Assisted Tri-Loop Digital Low-Dropout Regulator,” IEEE Journal of Solid-State Circuits, vol. 53, no. 1, pp. 20–34, Jan. 2018.

[5] X. Ma, Y. Lu, R. P. Martins, and Q. Li, “A 0.4V 430nA quiescent current NMOS digital LDO with NAND-based analog-assisted loop in 28nm CMOS,” in IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 306–308.

[6] Y. Huang, Y. Lu, F. Maloberti, and R. P. Martins, “A Dual-Loop Digital LDO Regulator with Asynchronous-Flash Binary Coarse Tuning,” in IEEE International Symposium on Circuits and Systems (ISCAS), 2018, pp. 1–

[7] L. Zhao, Y. Lu, and R. P. Martins, “A Digital LDO With Co-SA Logics and TSPC Dynamic Latches for Fast Transient Response,” IEEE Solid-State Circuits Letters, vol. 1, no. 6, pp. 154–157, Jun. 2018.

评论