一. 前言

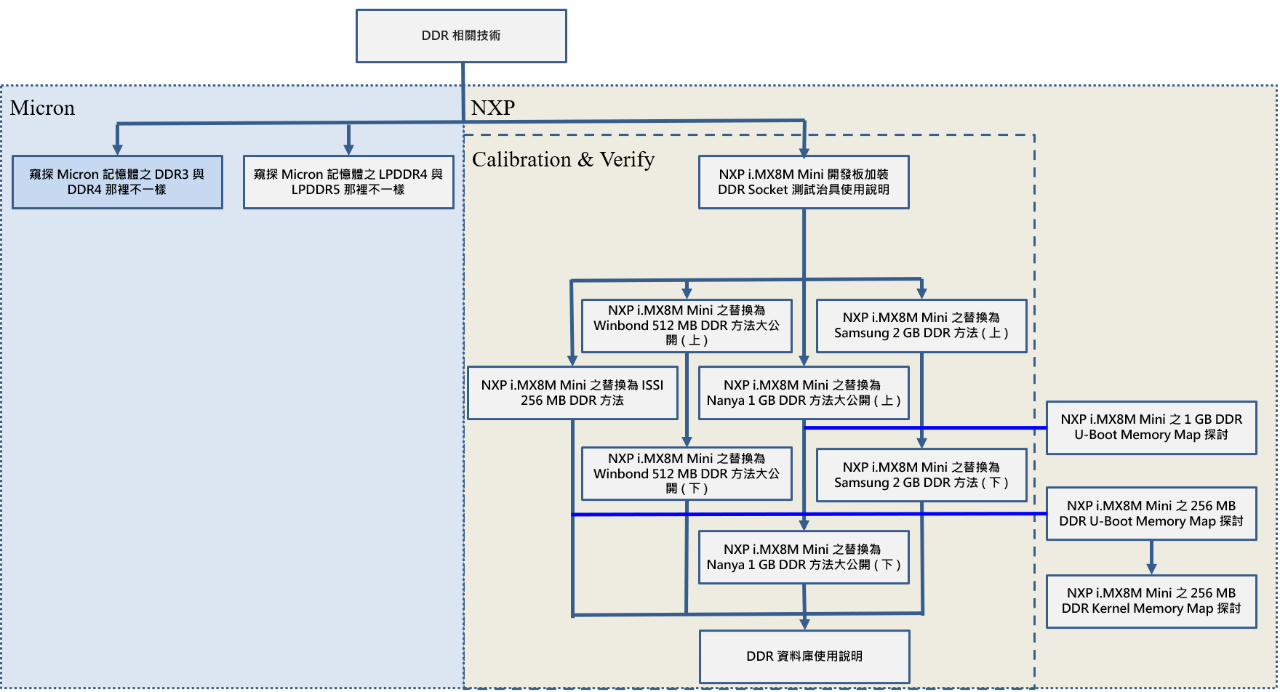

世平集团针对 DDR 相关技术整理了一系列博文,其中也包含了 Micron DDR 的相关技术。下图为详细的博文索引架构笔者希望能够透过这些博文协助大家更了解 DDR 的相关技术,未来笔者也会持续更新此系列的相关博文还恳请支持!而本篇博文会针对 DDR 相关技术索引架构中的【ATU Book-Micron 系列-DDR】窥探 Micron 记忆体之 DDR3 与 DDR4 那里不一样 这篇文章做介绍。

从各大报章杂志甚至是科技新知网站 ( 例如 DIGITIMES ) 的文章中可以了解到 DDR4 是当前主流的记忆体。而 DDR4 比起 DDR3 有着更高的 Performance 和更强大的功能非常适合应用在 Micro-Server、Tablet 等领域上。

此外 DDR4 的好处有运行“电压更低”以及“速度更快”等优势。本篇文章将会整理出 Micron 的 DDR3 与 DDR4 不一样的地方给各位读者们参考,希望借由此篇文章的分析让各位读者对 DDR4 更加了解。

以下笔者将会用 DDR4 的角度来与 DDR3 做比较。接着请各位读者们继续看下去吧!

二. DDR4 的电压比 DDR3 的电压更低

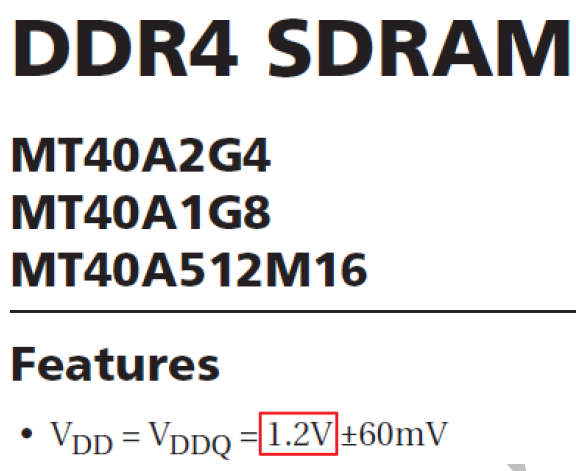

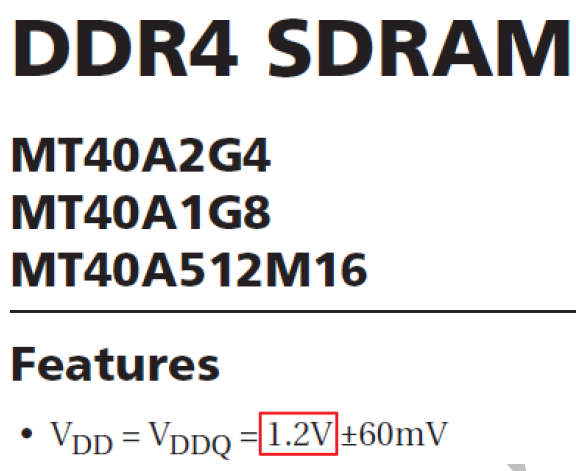

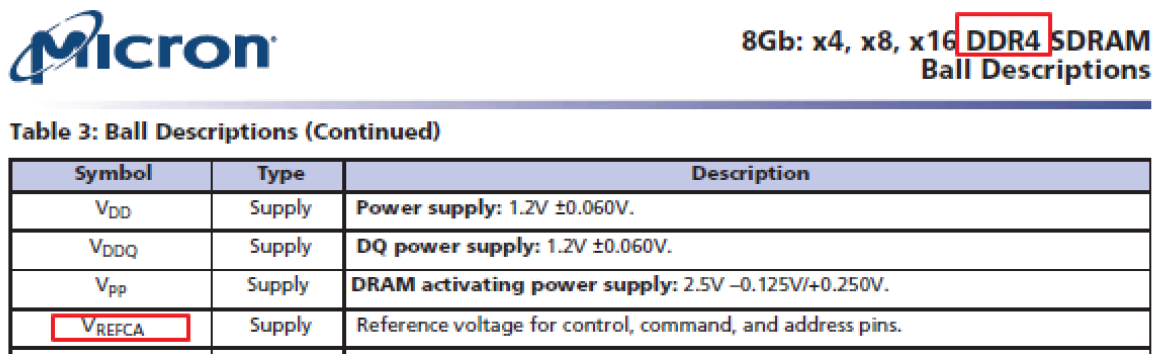

DDR4 VDD 的电压降低为 1.2V ( 可参阅以下图片 );DDR3 VDD 的电压为 1.5V,相较之下 DDR4 明显的更加省电了。

此图来自 Micron DDR4 Datasheet。

三. DDR4 VREF Input Pin 的改变

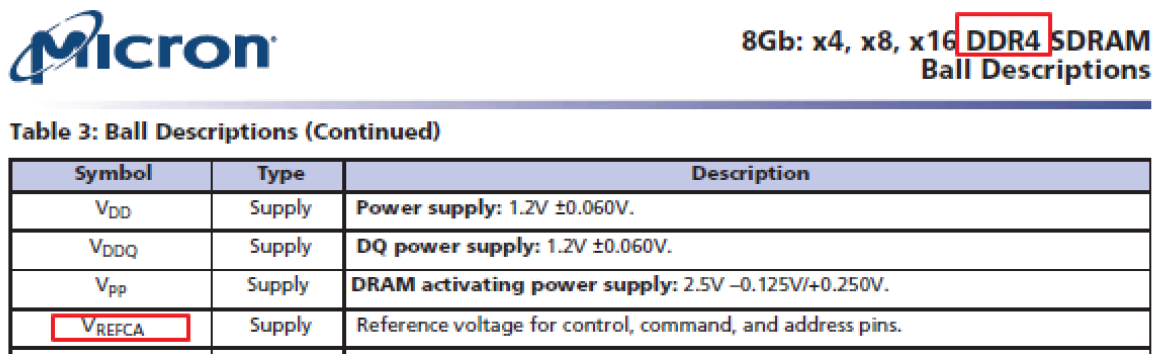

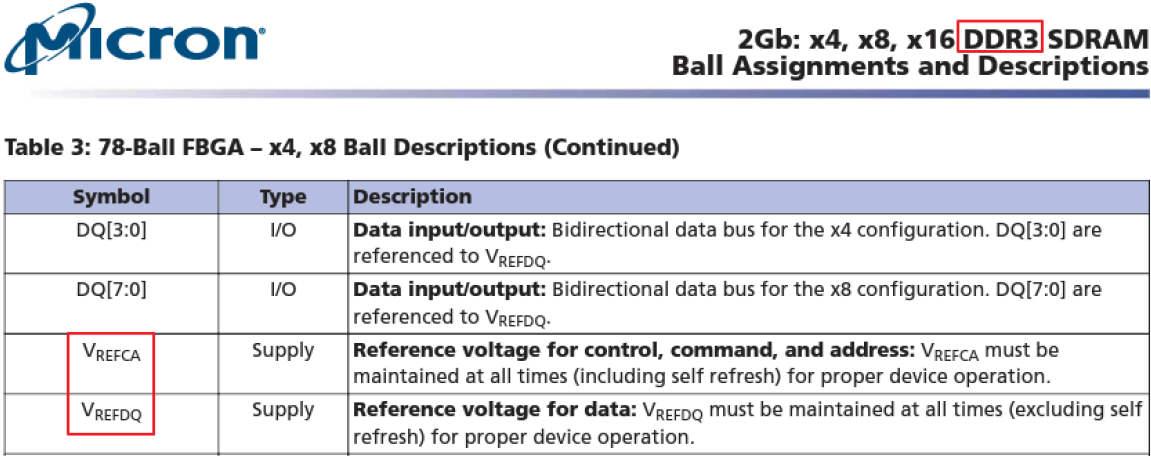

DDR4 的 VREF Pin 剩下 1 根 ( VREFCA );而 DDR3 的 VREF Pin 有 2 根 ( 分别为VREFDQ 与 VREFCA ) 我们可从 Datasheet 中看到差异 ( 也可参阅以下比较图 )。

补充 1:VREF 就是参考电压。笔者的理解为 VREFCA 就是 Command / Address Pin 的参考电压;而 VREFDQ 就是 Data Pin 的参考电压。

补充 2:DDR4 的 VREFDQ 是由内部生成。笔者的理解是可以透过修改 MR6[7]、MR6[6]、MR6[5:0] 等 Register 来做到开关或 Range 的调整 ( 详细叙述可参阅 Datasheet )。

补充 3:MR 为 Mode Register 的简写。

此图来自 Micron DDR4 Datasheet。

此图来自 Micron DDR3 Datasheet。

四. DDR4 没有低电压版本

DDR4 工作电压为 1.2V 并无其他低电压的版本。在 DDR3 系列 DDR 中有一个低电压的版本叫做 DDR3L;它的工作电压可运作在 1.35V ( 一般标准的 DDR3 工作电压是 1.5V ),值得一提的是 DDR4 的电压 ( 1.2V ) 就比 DDR3L 的电压 ( 1.35V ) 还低了。

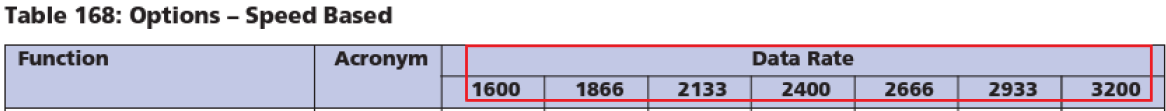

五. DDR4 的 Data Rate 更快

DDR4 Data Rate 传输速率范围在 1600 MT/s 到 3200 MT/s 之间;而 DDR3 Data Rate 传输速率范围在 800 MT/s 到 2133 MT/s 之间,比起 DDR3 的传输速度 DDR4 明显快了很多 ( 多了 2400、2666、3200 等频段 )。

补充 1:DDR4 比起 DDR3 多了 2400、2666、3200 等频段。

补充 2:Data Rate 为 Clock 的 2 倍。举例来说 Clock 如果是 1600 MHz 那 Data Rate 就是 3200 MT/s。

六. DDR4 Density 支援的容量更大

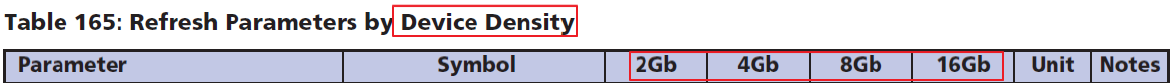

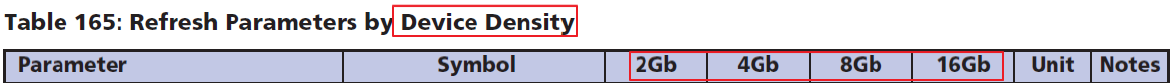

DDR4 Density 支援 2Gb ~ 16Gb,而 DDR3 Density 只支援 512Mb ~ 8Gb 明显可以看到 DDR4 能支援的容量更大了。

可由下图了解到 DDR4 支援的 Density 有哪些。( 此图来自 Micron DDR4 Datasheet )

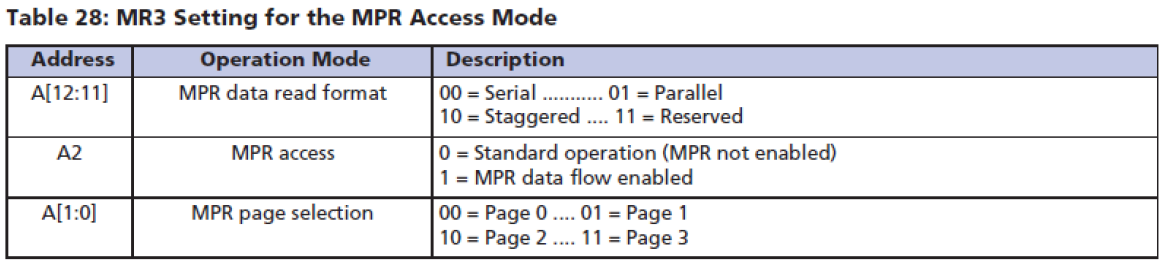

七. DDR4 支援更多 Bank

DDR4 与 DDR3 相比 DDR4 多了Bank Group 的这个概念,而每组 Bank Group 是由 4 个 Bank 所组成。从 Datasheet 中可以得知 x4/x8 Configuration 的 DRAM 有 4 组 Bank Group;而 x16 Configuration 的 DRAM 有 2 组 Bank Group。

值得一提的是 DDR4 Bank Group 的这个概念,可让 Bank 对不同 Bank Group 的 Access 比在同一组 Bank Group 内的 Access 还快。( 详细说明可参阅 Datasheet )

补充:将 Bank 拆分到 Bank Group 里的好处,就是让 DDR4 可以改善与提升 Bank Access 的时间。

从以上叙述可以得知 DDR4 最多可以支援到 4 组 Bank Group ( x4/x8 Configuration ),而一组 Bank Group 是由 4 个 Bank 组成。因此 DDR4 最多可以支援到 16 个 Bank,而 DDR3 最多只可以支援到 8 个 Bank。

下图叙述了 DDR4 支援的 Bank 数量。( 此图来自 Micron DDR4 Datasheet )

八. DDR4 DLL 频率变高

DDR 的运作主要是依靠 Clock ( CK_t/CK_c ) 做为基础来做到 Read / Write 等讯号的同步,而电压或温度的变化都可能会影响到 Clock 精准度进而导致 Read / Write 等的 Timming 出现问题。根据笔者的了解 DLL ( Delay Locked Loop ) 机制可以让 Clock 的讯号同步问题得到改善在 DDR 技术里是个相当重要的关键。由于 DDR4 的速度比 DDR3 更快的缘故因此 DLL 的速度也需要跟着增加。

值得一提的是 DLL 在 DDR 上电初始化阶段会被 Enable ( 可参阅下图 ),而主要是透过 MR1[0] 的Register 来做设置。而 DDR4 比起 DDR3 在 DLL Enable 时候有着更高的 Data Rate ( 667 MHz 到 1.6 GHz )。此外 DDR4 比 DDR3 更为弹性“多了 DLL-Off 模式可以使用”,而使用 DLL-Off 模式会影响到 Read Data 的部分讯号 ( 例如 tDQSCK )。

补充 1:根据笔者的理解当系统平台想进入低功耗模式,可能会采取将 DDR 切换到 DLL-Off 模式的方式。

补充 2:关于 DLL Enable 与 DLL-Off 模式的更多叙述可参阅 Datasheet。

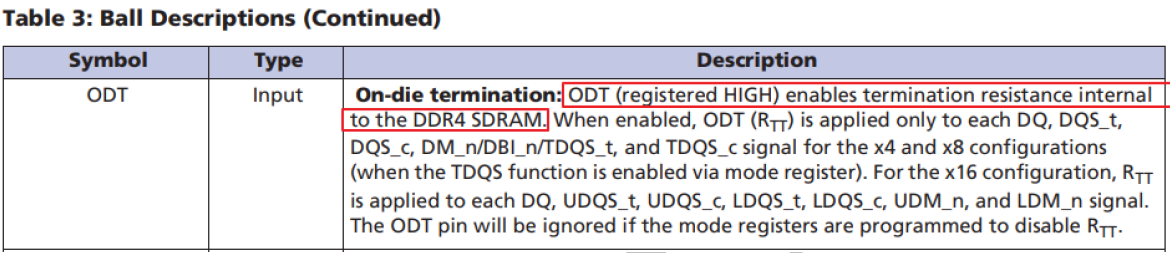

九. DDR4 ODT 的不同

首先让我们粗略的了解一下 ODT 是什么,ODT 是 On-Die Termination 的缩写。根据笔者的理解它指的是一根实体 Pin 脚也是一种讯号状态的表示。一般常见讯号有 High Level 或 Low Level 这 2 种而 DDR 信号的传输非常快速所以对电路阻抗匹配的要求较高,因此多了 ODT 功能来做到对电阻值的细部调整进而达成让讯号完整性更好之目的。

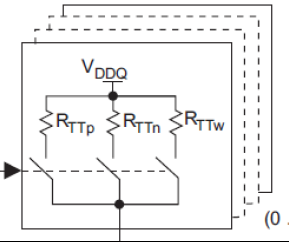

从 Datasheet 中可以得知设置 ODT Pin 脚为 High 以后透过改变 RTT 的电阻值可以改变 DQ、DQS_t/DQS_c 等讯号的强度。RTT 就是 DDR 里面的终端电阻值可以透过 MR Register 做调整。

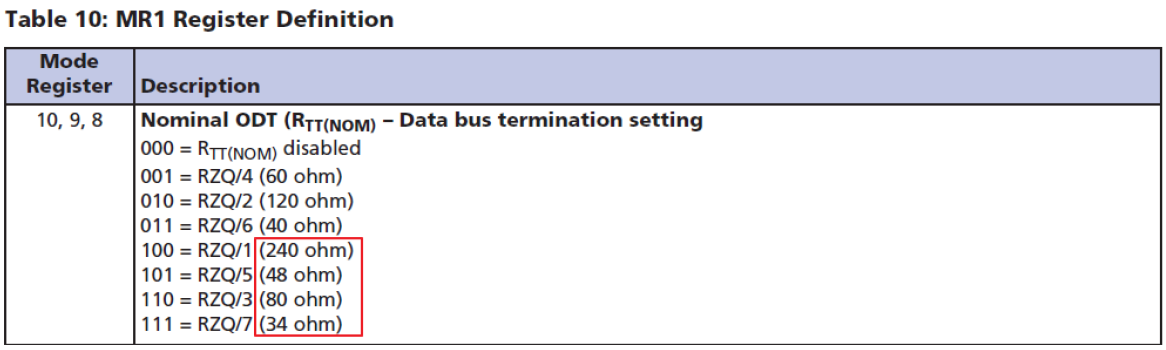

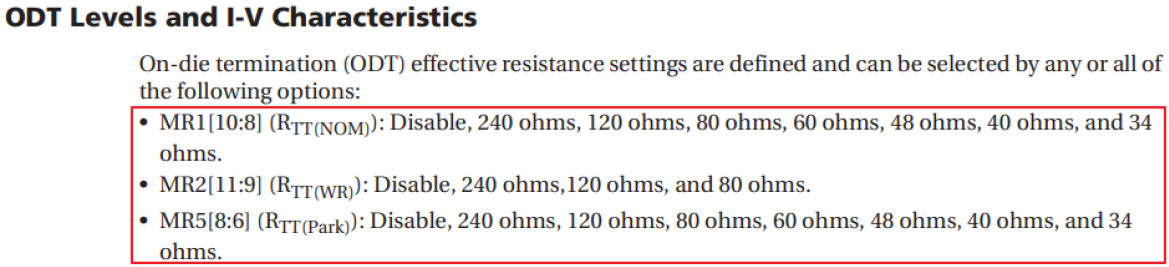

由于 DDR4 的信号传输比起 DDR3 的讯号更加高速所以对电路阻抗匹配的要求更高的关系,因此在 DDR4 增加了几个电阻值 ( 分别为 240、80、48、34 Ohm;可参阅 DDR4 Datasheet MR1[10:8] Register ) 可以做到对终端电阻更加细微的调整。

值得一提的是 DDR4 还增加了新的 ODT ( On-Die Termination ) 模式 “Park”;稍早有提到开启 ODT 功能后就可以设定 DDR 内部的终端电阻 RTT,因为 DDR4 的信号传输更加高速并且对电路阻抗匹配更加要求,所以可以透过修改 RTT 相关 Register 做到更加细微的终端电阻调整达到提升讯号的完整性的目的。

DDR4 的 ODT 模式共有以下 4 种状态:

(1) Data Termination Disable。

(2) RTT(NOM):就是 Nominal ODT ( RTT(NOM) ) 可修改 MR1[10:8] Register 来做电阻调整。

(3) RTT(WR):就是 Dynamic ODT ( RTT(WR) ) 可修改 MR2[11:9] Register 来做电阻调整。

(4) RTT(Park):就是 Parked ODT ( RTT(Park) ) 可修改 MR5[8:6] Register 来做电阻调整。

补充:根据笔者的理解“不同的 Case 对上述提到的 RTT(NOM)、RTT(WR)、RTT(Park) 的设置都会不同”。

先在这里小结一下,由以上叙述可以得知 DDR4 比起 DDR3 的 RTT 多了一些电阻值可做到更加细微的调整,另外 DDR4 比起 DDR3 也多了一个 RTT(Park) 模式可以使用。DDR4 比起 DDR3 多了更多弹性的选择可以让信号的完整性更佳。

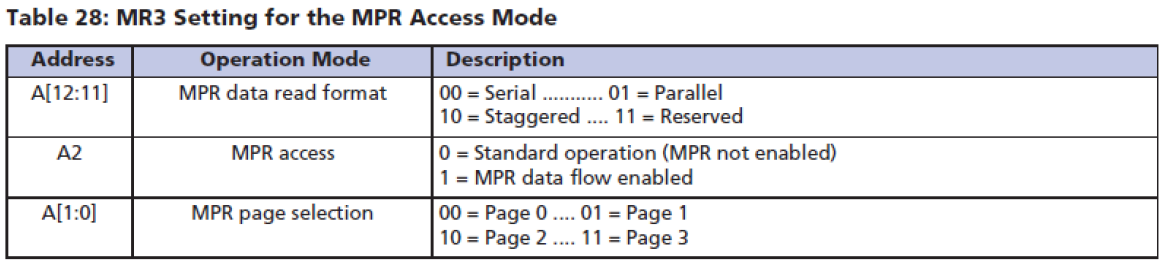

十. DDR4 MPR 增加新定义

DDR4 在 MPR ( Multipurpose Register ) 部分增加了新定义,添加了像是 MR3[12:11] ( MPR Data Read Format ) 之类的功能。在 DDR4 可透过操作 MR3[1:0]、MR3[2]、MR3[12:11] Register 来使用 MPR 功能。笔者的理解是:若将 MR3[2] 设置为 1 就是启用 MPR 功能;而 MPR 启用后将可以 Write / Read Specialized 的 Data 到 DRAM。

下图为 DDR4 的 MPR 可以设置的模式。( 此图来自 Micron DDR4 Datasheet )

十一. 结语

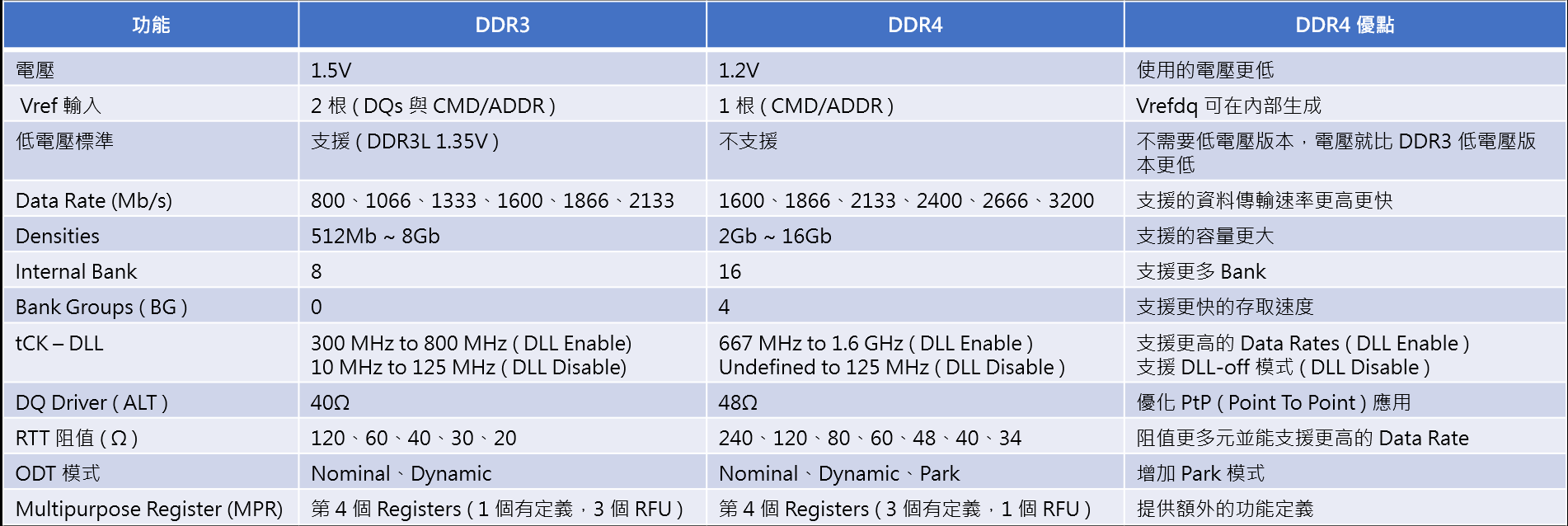

世平集团针对 DDR 相关技术整理了一系列博文,而本篇文章针对 Micron 的 DDR4 与 DDR3 不一样的地方做了些粗略的介绍。DDR4 有 IO 电压更低、运行速度更快、容量更大等优势 ( DDR4 与 DDR3 详细的不同处可参考以下的比较表 ),希望本篇文章的内容可以让各位读者对 Micron 的 DDR4 相关技术有更深入的体会,若未来读者们有 DDR 的相关问题欢迎随时与世平集团做讨论,之后笔者也将会继续产出与 DDR 有关的相关博文,请各位读者拭目以待。

十二. 参考文件

[1] https://www.digitimes.com.tw/tech/dt/n/shwnws.asp?CnlID=1&id=628575&query=DRAM

[2] https://www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr4/8gb_ddr4_sdram.pdf

[3] https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr3/4gb_ddr3l.pdf?rev=8d4b345161424b60bbe4886434cbccf4

[4] https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr3/2gb_ddr3_sdram.pdf?rev=4bc67ac3a6f34250a2b73cb9db8c5502

[5] https://blog.csdn.net/comeonbestxiaohe/article/details/84971448

[6] https://www.computerdiy.com.tw/ddr4-ram/

[7] https://bbs.eetop.cn/thread-612579-1-1.html

[8] https://blog.csdn.net/hierro_zs/article/details/54603417

[9] https://community.nxp.com/t5/i-MX-Processors/i-MX-8M-Mini-configure-DLL-off-mode-using-LPDDR4-memory/m-p/1275517

[10] https://blog.csdn.net/tbzj_2000/article/details/90762594

[11] https://www.micron.com/products/dram/ddr3-to-ddr4

[12] https://www.kingston.com/tw/memory/ddr4-overview

[13] https://blog.csdn.net/hierro_zs/article/details/70238823

[14] https://kknews.cc/zh-tw/news/j5jpbmy.html

[15] https://www.micron.com/-/media/client/global/documents/products/technical-note/dram/tn0456_clock_jitter.pdf

[16] https://kknews.cc/zh-tw/news/oxrl2yq.html

[17] https://www.twblogs.net/a/5b80c55b2b71772165a93fc7

[18] https://www.rambus.com/dllpll-on-a-dram/

评论