i.MX8QXP/DXP+LPDDR4 的内存配置与测试包括以下几步:

- 根据LPDDR4 数据手册和相关硬件设计电路,生成LPDDR4 的初始化脚本。

- 运行内存压力测试工具来测试内存稳定性。

注意:

与i.MX6 系列不同,i.MX8X 的内存控制器根据 JEDEC 要求,实现了开机自动训练(或是校准)的功能,所以不需要象i.MX6 那样使用内存测试工具去手动校准内存,所以配置内存参数成为必要,而使用内存测试工具测试内存稳定性则不如i.MX6 那么必要。

由于i.MX8X 有自动训练(或是校准)功能,所以本文不再解释校准的原理细节。

生成LPDDR4 初始化脚本

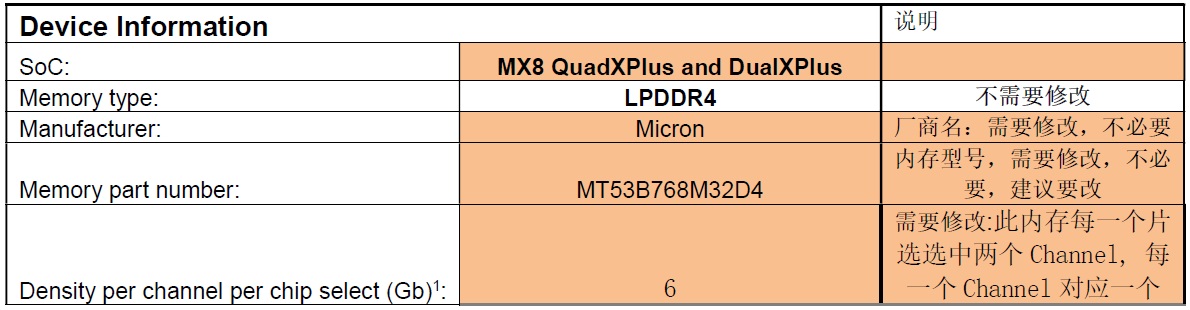

以i.MX8QXP MEK 板连接3GB LPDDR4: MT53B768M32D4 为例,使用LPDDR4 的脚本生成工具《MX8QXP_C0_B0_LPDDR4_RPA_1.2GHz_v13.xlsx》,配置内存相关参数,一般包括四大类:尺寸大小相关,时序相关,阻抗&ODT 设置相关和BYTE Swap 相关参数:

- 我们需要输入其数据手册中的相关大小尺寸参数:

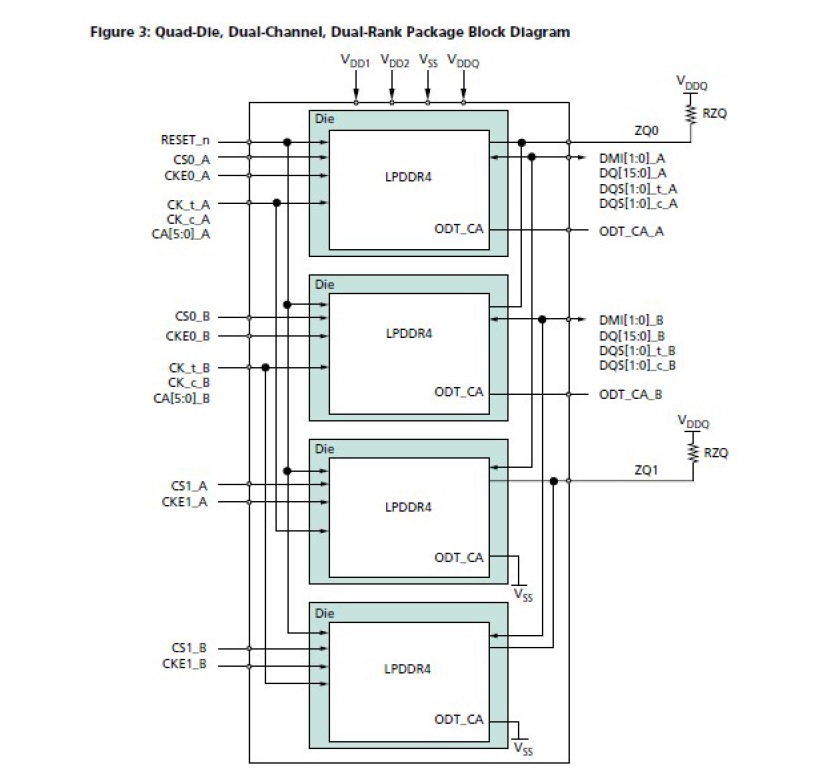

先看一下这颗LPDDR4 的构成:

所以这颗LPDDR4 内存有4 个Die,

第一个Die 对应Channel 0 片选0,

第二个Die 对应Channel1 片选0,

第三个Die 对应Channel 0 片选1,

第四个Die 对应Channel 1 片选1。

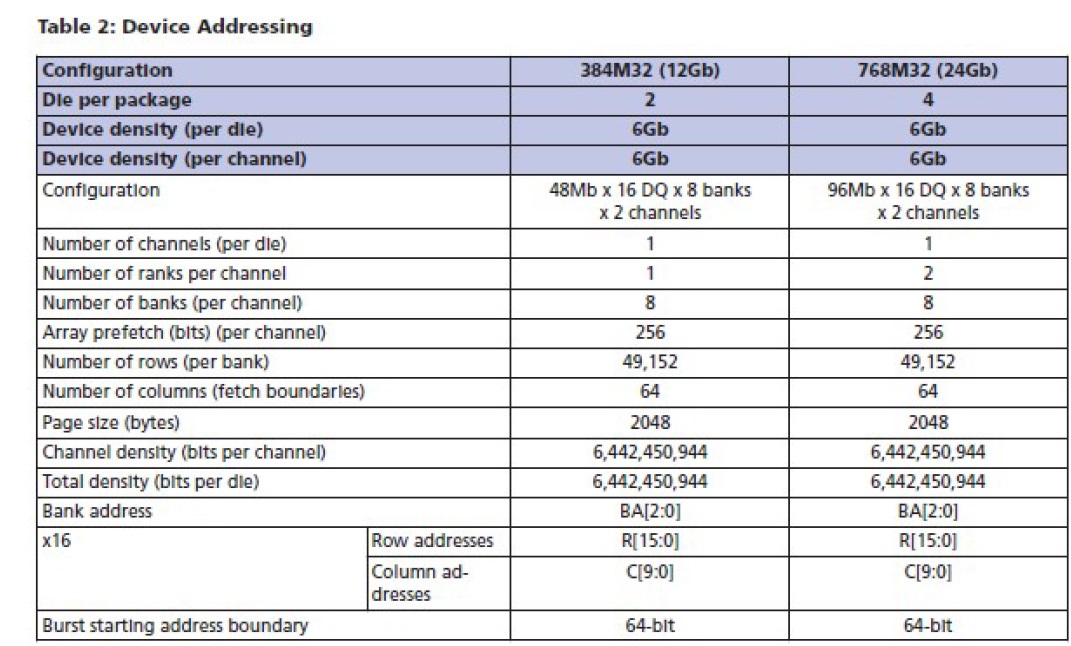

它的地址表如下:

所以:

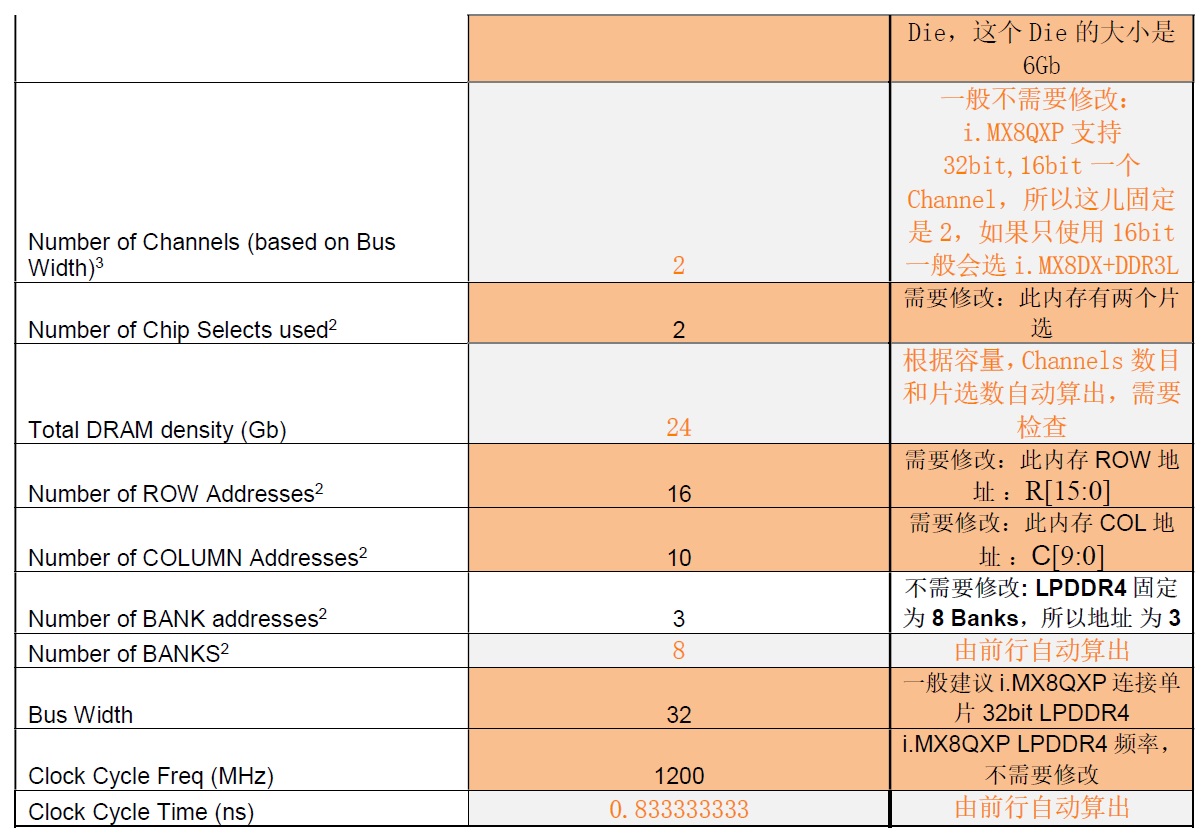

Density per channel per chips select(Gb)= Device density(Per Channel)=6Gb

Number of Channels=2 (2 Channels i.MX8X is 32bit, normally will link 1 piece 2 Channel

LPDDR4)

Number of Chip Selects used=Number of rank per channel=2:used CS0_1/CKE0_1_A/B

Number of ROW Addresses=R[15:0]=16

Number of COLUMN Addresses=C[9:0]=10

Number of BANK Addresses=BA[2:0]=3

Bus Width=M32=32bit: i.MX8X is 32bit, normally will link 1 piece 2 Channel LPDDR4

打开《MX8QXP_C0_B0_LPDDR4_RPA_1.2GHz_v13.xlsx》配置工具,在Register Configuration一页中填入内存大小相关参数,说明 如下:

- 其它时序相关参数一般会根据JEDEC 要求来设计,所以可以使用默认值,不需要特别修改。

- 阻抗相关参数如果是按照我们硬件开发指南的阻抗要求设计的,一般也不需要修改,在DEBUG 一章中有说明 如何修改阻抗和ODT。

- Swap 设置:

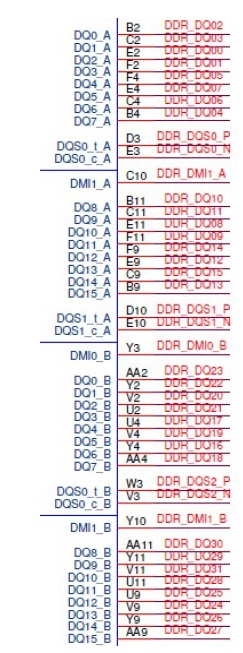

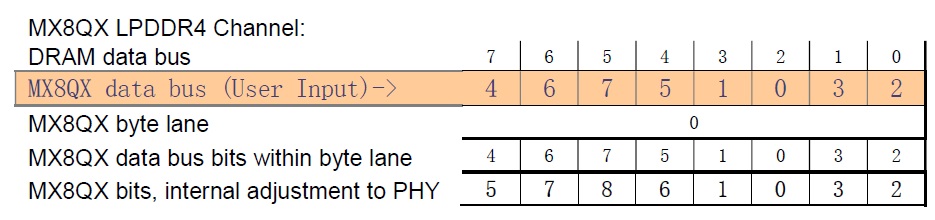

i.MX8QXP 的内存控制器允许BYTE 内交换,为了Layout 方便,一般会进行BYTE 内交换,所以要根据实际原理图设计来配置BoardDataBusConfig 一页,根据原理图设计如下:

比如说:i.MX8QXP 的DDR_DR00 连接到了LPDDR4 的DQ2_A 上,所以如下每二行,红字的部分,DRAM data bus 2 例对应的是MX8QX data bus(User Input)的值是0。以此类推:

如果客户的扇出连线设计与i.MX8QXP MEK 板是相同的,则此页不修改,否则则需要修改。在填写完Register Configuration 一页和可能需要填写完BoardDataBusConfig 一页后,可以在DCD CFG file CBT(4.14.98_2.3.0 BSP 对应的SCFW 版本1.3.0 中已经使能了CBT:command bustraining,所以使用带CBT 功能的这一页)一页中得到Bootloader 需要的内存配置格式,拷贝下来存成文件:imx8qx_dcd_1.2GHz_cbt.cfg。(cbt 功能已经在i.MX8QXP 平台上验证通过,所以建议可以使用,以后更新的BSP 也会使用)。

可以在DCD CFG file (4.19.35_1.1.0 BSP 对应的SCFW 版本1.2.7.1 中还没有使能了CBT:

command bus training,所以使用不带CBT 功能的这一页)一页中得到Bootloader 需要的内存配置格式,拷贝下来存成文件:imx8qx_dcd_1.2GHz.cfg。

在DDR Stress Test Script CBT 一页中得到内存测试工具需要的内存配置格式,拷贝下来存成文件:mx8qx_c0_b0_lpddr4_1200mhz_RPAv13_cbt_myplatform.ds。

在DDR Stress Test Script 一页中得到内存测试工具需要的内存配置格式,拷贝下来存成文件:mx8qx_c0_b0_lpddr4_1200mhz_RPAv13_myplatform.ds。

參考資料:

NXP官網:

- https://www.nxp.com/design/development-boards/i-mx-evaluation-and-development-boards/i-mx-8quadxplus-multisensory-enablement-kit-mek:MCIMX8QXP-CPU

- https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-processors/i-mx-8-processors/i-mx-8x-family-arm-cortex-a35-3d-graphics-4k-video-dsp-error-correcting-code-on-ddr:i.MX8X?tab=Documentation_Tab

- https://www.nxp.com/design/i-mx-developer-resources/i-mx-software-and-development-tools:IMX-SW

- https://github.com/NXPmicro/mfgtools

- https://www.nxp.com/webapp/Download?colCode=L5.4.70_2.3.0_MX8QXPC0&appType=license

评论