1、 电磁兼容性(EMC)注意事项

EMC与电磁能量的生成、传输和接收有关,此电磁能量可能会扰乱电子系统的工作。来源(发射方)产生辐射,然后一个传输或耦合路径会将辐射能量传输至接收方,即对辐射能量进行处理的地方,在此可引发良好或不良的行为。电子设备需要符合特定的限制,以满足发出能源和易受外部事件的要求。世界各地的多个监管机构设定了地区性规格,以确保电子设备互不干扰。

CMOS模拟和数字电路具有很高的输入阻抗。这导致它们对外部电场非常敏感。因此,您需要特别注意,以确保在辐射和导电噪声存在的情况下,这些电路仍可以正常工作。

1、1 辐射干扰及辐射

辐射电能会影响系统的测量,并可能影响CapSense处理器内核的运作。在PCB板上,干扰会通过传感器走线和其他数字和模拟输入进入CapSense芯片。虽然CapSense提供了一个直观和强大的接口,能够通过消除机械部件提高产品的可靠性,它所产生的辐射发射(RE)又能加重电磁兼容性(EMC)问题。

请使用下面的技术来降低辐射干扰和发射。

1、1、1 通用EMI/EMC指南

1、1、1、1 接地层

一般的情况下,在PCB 板上正确放置接地层会降低RF 辐射和干扰。但是,接近CapSense 传感器或用于将这些传感器连接至PSoC 引脚的走线的实心接地层会增大传感器的寄生电容。因此,推荐在传感器周围以及传感器下方的PCB板底层上使用网格接地层,如接地层部分所介绍的内容。在PBC 板上的器件和其他电路部分下面的实心接地要远离CapSense 传感器和走线。不建议在CapSense 传感器或走线10 mm 的范围内使用实心接地层。多层电路板是首选。如果您使用四层或更多层的电路板,建议您将一层用作接地层,这对降低辐射很有帮助,因为它能大大减少接地层的抖动。

1、1、1、2 串联电阻

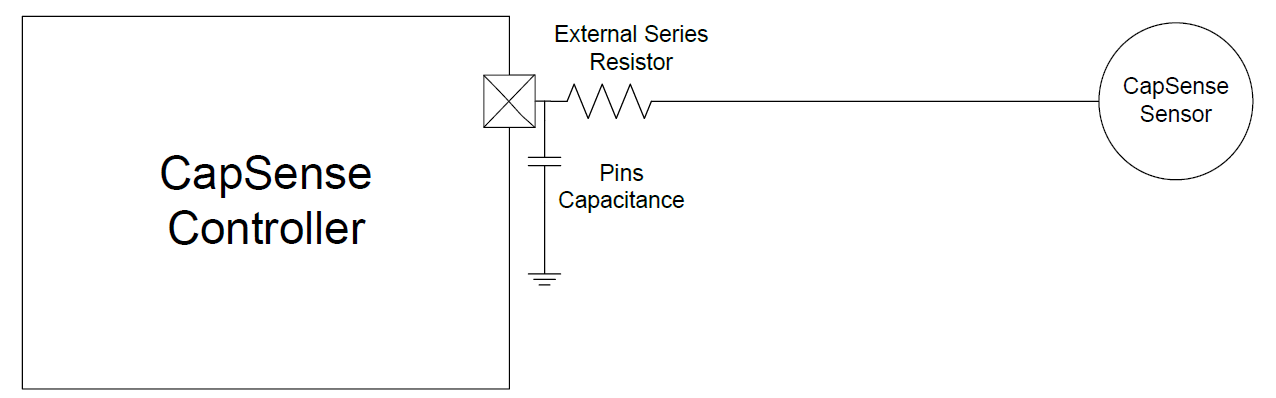

各个CapSense 控制器引脚均有各自的寄生电容(CP)。添加一个外部电阻可构成低通RC滤波器,从而减少耦合到引脚的RF 噪声振幅。该电阻和连接到引脚的走线的寄生电容(如图1-1 中所示的传感器走线和传感器垫块)组合时,可构成能够明显降低RF 辐射的低通滤波器。因此,串联电阻对于消除高次谐波和降低RF 干扰和辐射十分有用。

图1-1. RC 滤波器

应将串联电阻置于靠近PSoC 引脚的地方,以便能够在PSoC 器件的输入端过滤掉走线所引起的辐射噪声。因此,推荐在PSoC 引脚的10 mm 内放置串联电阻。

1、1、1、2、1 CapSense 输入线路

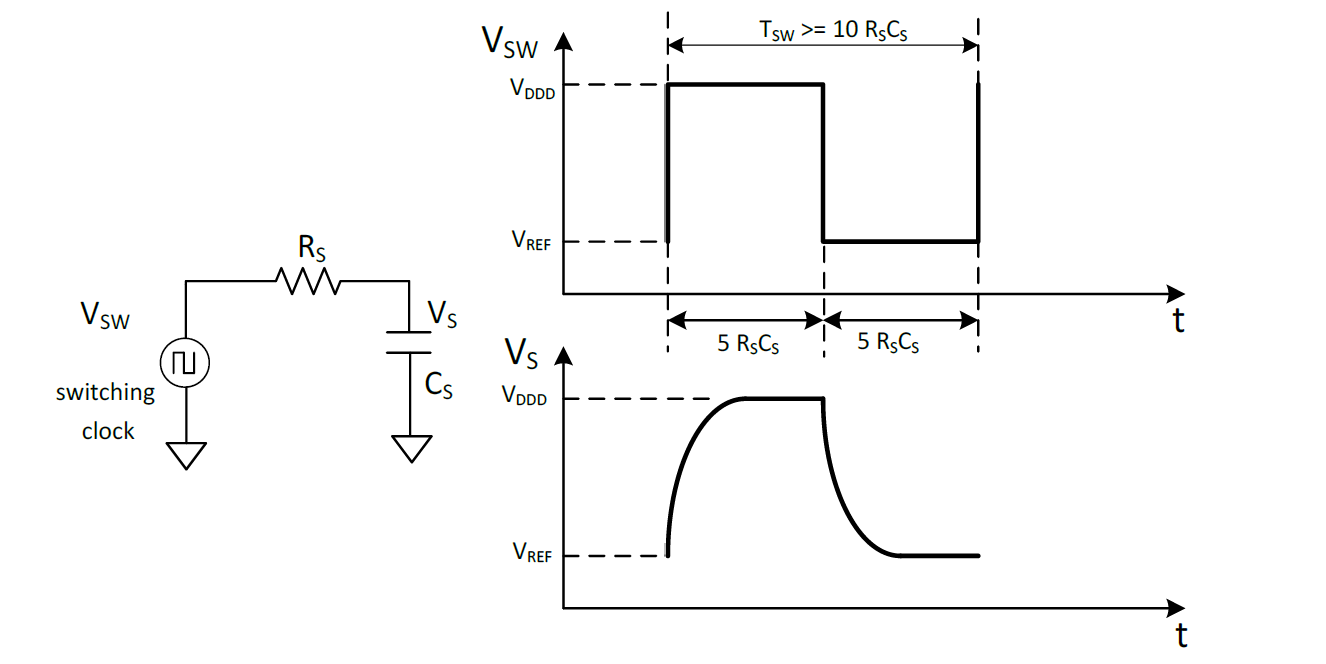

为了保证CapSense 正常工作,传感器在每个开关周期中必须要满充满放。传感器电容的充电和放电路径本身具有的串联电阻会减缓充电/放电过程。图1-2 显示了它的等效电路和产生的波形。增加电阻会改变将CP 转化为等效电阻的开关电容电路的时间常数。如果串联电阻值较高,开关电路的较低时间常数可抑制辐射和其干扰,但会限制可传输的电荷量。这样不能实现对传感器进行完全地充电和放电操作。这会降低信号等级,进而降低信噪比。电阻值越小越好,但在阻止射频辐射和干扰方面却不太有效。

通用覆铜PCB 上CapSense 输入线路的串联电阻推荐值为560 Ω。ITO 面板的电阻较大。电阻值选择范围仅为100 Ω至1 kΩ。串联电阻通常使用的范围为560 Ω 至4.7 kΩ,以实现EMC 目的。串联电阻实际的最大值会因器件而异。其大小取决于多个因素,如:用作传感器的GPIO 的电阻、用于扫描传感器的开关频率以及所需的信噪比。

图1-2. 等效电路和波形

RS 是GPIO 电阻和外部串联电阻的总和。CS 是传感器的最大电容值。对于给定的开关频率,必须选择能够对传感器电容进行完全充电和放电的串联电阻值。换句话说,对于给定的串联电阻,必须选择能够对传感器电容进行完全充电和放电的开关频率值。如果不能修改其他CapSense 参数,那么降低开关频率会降低信噪比。因此,在串联电阻值和开关频率之间进行权衡,以实现所需性能。

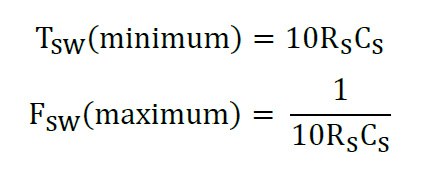

根据经验,可选择5RSCS 的周期用于充电和放电循环。用于计算最小值周期和最大频率的公式分别为: 1、1、1、2、2 数字通信线路

1、1、1、2、2 数字通信线路

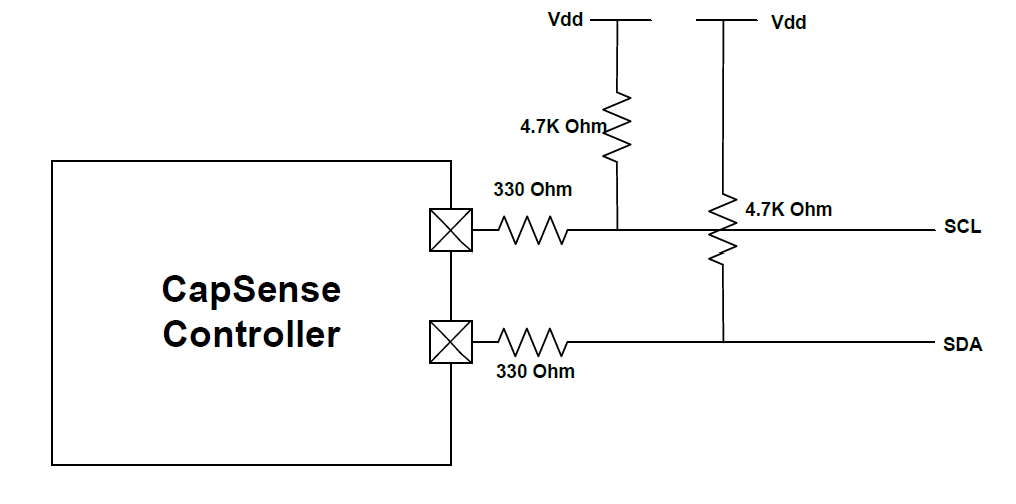

通信线路,如I2C和SPI,同样能受益于串联电阻,并且推荐采用330 Ω。通信线路的走线一般较长,它们同CapSense走线一样以天线的形式发射干扰。推荐在通信线路上采用一个大小为4.7 kΩ 的上拉电阻。因此,如果在这些线路上串联超过330 Ω 的电阻,则电压电平(VIL 和VIH)会超出规范范围,在最坏的情况下还会使系统和接收器输入阻抗间的供应电压跌出规范范围。由于当PSoC 输出为低电平时,VIL 电平仍会保持为I2C 规范所要求的0.3 VDD,因此330 Ω 的电阻不会影响I2C 的操作。

图1-3. 通信线路上的串联电阻

1、1、1、3 走线长度

长走线比短走线引起的噪声更多。长走线同样会增加CP 值。所以要尽可能地缩短走线长度。

1、1、1、4 电流环路面积

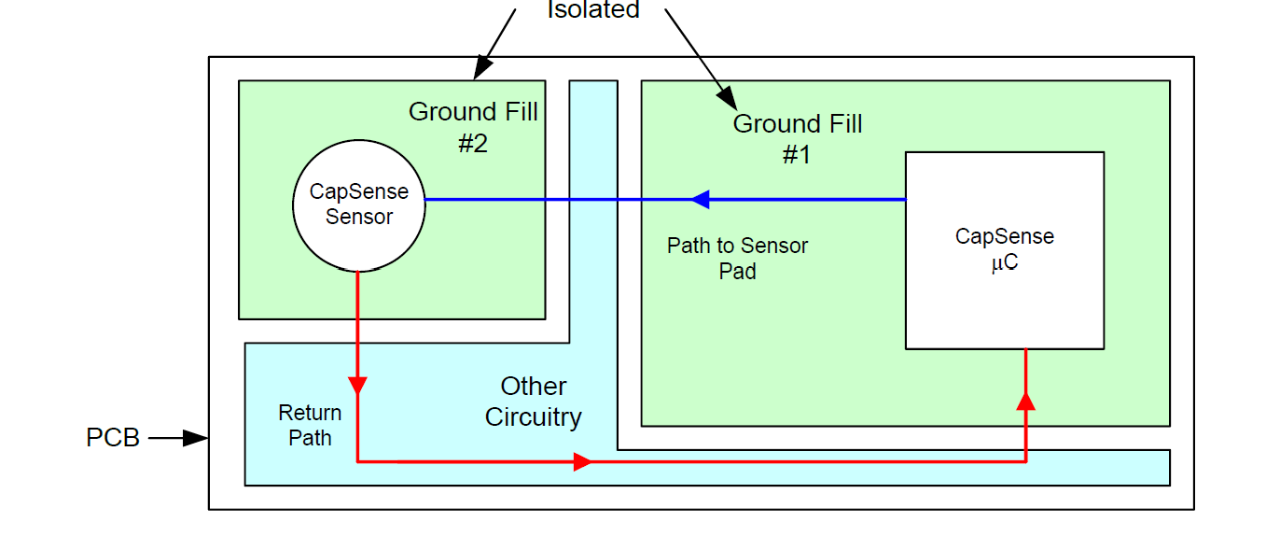

另一个重要的布局注意事项是尽量缩短电流返回路径。接地层可降低全部接地阻抗,从而减少高频率接地反弹。需要确保每个传感器线路都具有良好的GND 返回路径。因为电流是在环路中流通的。除非高频信号具有正确的返回路径,否则返回电流会通过较长的回路路径,从而形成较宽的环路;这样会发生由互电感导致的信号问题。因此,会增大辐射和干扰。

如果器件封装中包含了高频电流环路,那么能量也可以通过磁场耦合到器件外。通过磁通量可以使器件形成一个电流环路,以便链接到器件外面的电路环路。该互电感会在外部环路中产生一个意外电压。同样,外部的磁通量也会在内部电路环路中产生一个意外的电压。通过使用尽可能小的电源和信号环路区域,可以最小化磁场耦合。在地面上拼接过孔(越多越好)。这样会降低接地总阻抗。用于时钟和振荡器电路等高频率走线应同时连接到两个接地线路。这样可确保不会发生耦合情况(该情况会导致串扰)。如果可能,请使用独立的接地层和电源层。图1-4 显示了一个不合理的接地方案示例。通过减少环路面积大大改善了布局。

图1-4. 不合理的接地方案和接地环路

在图1-5 中,一个接地层围绕着两个传感器,此接地层与CapSense 控制器接地连接,而接地层围绕着第三个传感器。第三个传感器通过其他电路的长线被连接到其他接地层,从而造成电流环路。在这种布局下,第三个传感器会更容易受辐射噪声影响,且会增加辐射。在原理图上这两个接地部分位置相同,所以更好地布局的话它们可能是一个连接的区域。

图1-5. 不合理的电流环路布局

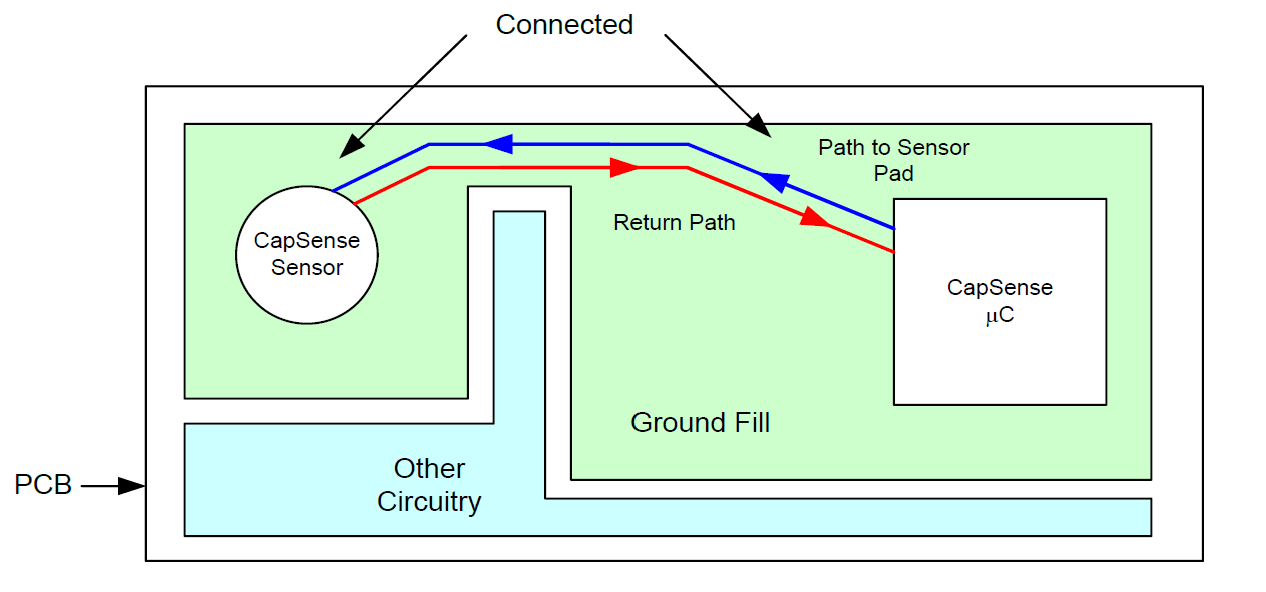

图1-6 说明了前面示例中的合理布局。通过连接两个接地区域,减少了环路面积。

图1-6. 合理的电流环路布局

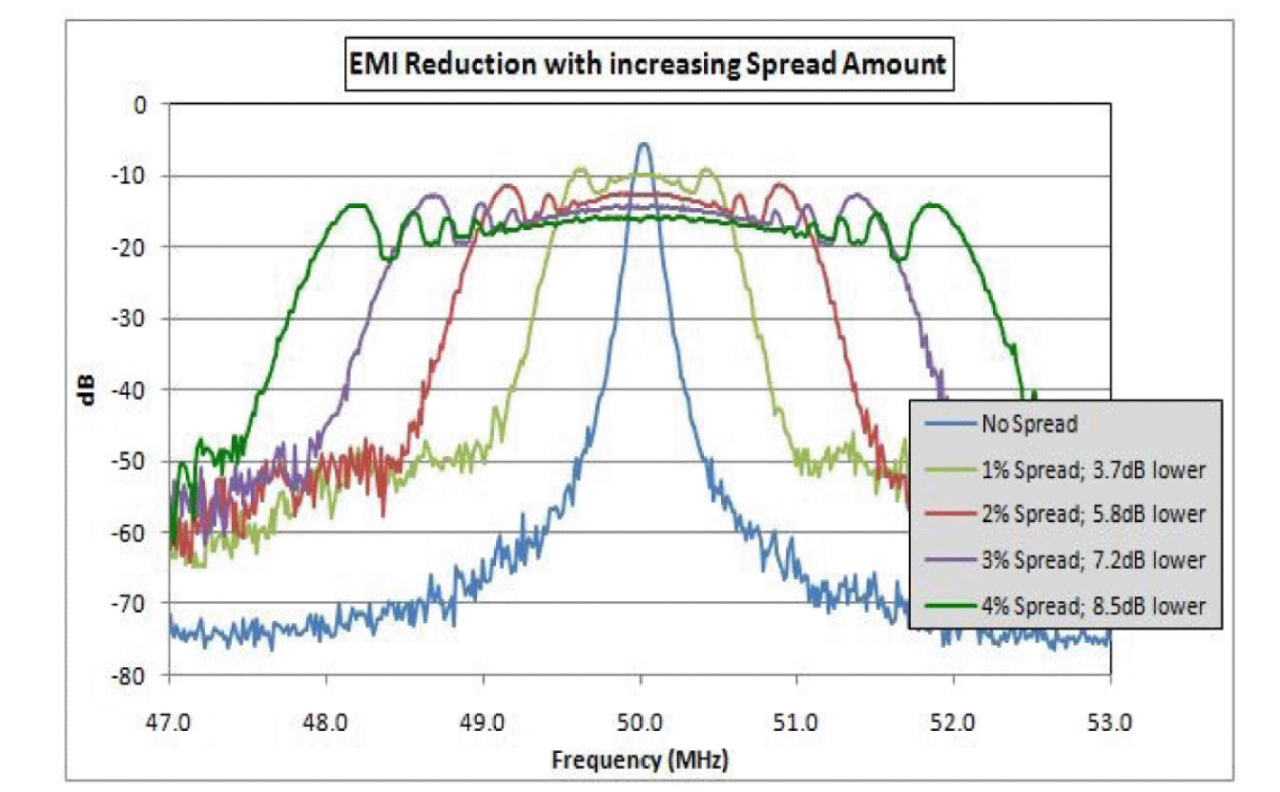

1、1、1、5跳频

跳频是一种通过较窄的频带扩展输入信号或工作频率的方法。该方法有助于降低峰值,并实现在频率范围内(如图1-7 所示)扩展辐射和干扰。下面介绍了PSoC 的各种跳频方法:

图1-7. 跳频

扫描传感器时实现IMO抖动:可以对不同的传感器进行IMO抖动或调整操作。例如,当基本IMO频率为24 MHz时,那么使用24 MHz到22 MHz的频率范围对IMO频率进行扫描。只能使用一个频率对传感器进行扫描。使用不同的频率对不同的传感器进行扫描。这样,通过扩展辐射可降低峰值。

进行扫描时可实现IMO抖动:还可以在每次进行扫描实现IMO抖动。当一个传感器被扫描时,那么使用24 MHz到22 MHz的频率范围对IMO频率进行扫描。因此,该方法可防止使用一个频率对传感器进行扫描。这样,通过扩展辐射可降低峰值。该方法还可以提高抗RF干扰的能力。

扩频时钟(SSC):通过使用外部时钟也能够使PSoC工作。与实现IMO抖动方法相同,使用扩频时钟也有助于在较宽的频率范围内扩展辐射。在PSoC1内,只能使用端口P1[4]提供外部时钟。在这种情况下,必须将引脚P1[4]驱动模式设置为数字高阻态。这有助于提高抗RF干扰的能力和扩展辐射。

伪随机序列(PRS):使用PRS(并不是固定的时钟源)可以降低CapSense引脚上的噪声(通过减少由固定频率源引起的EMI),并提高对其他频率源和它们谐波的抗EMI能力。这有助于提高抗RF干扰的能力和扩展辐射。