本文介绍如何正确使用HME-H1C02系列芯片内嵌的SPI Flash用户区和可编程逻辑来扩展8051的程序空间。

FPGA H1C02的主要功能特性如下:

FPGA

时钟网络

IO特性

MCU

外设

内嵌存储器

配置

安全

1.3 系统连接概述

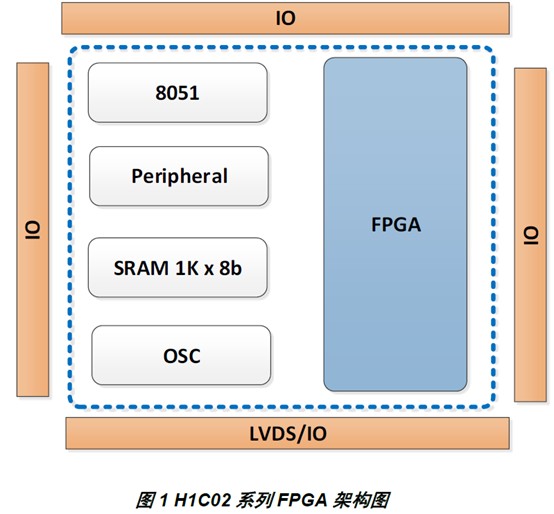

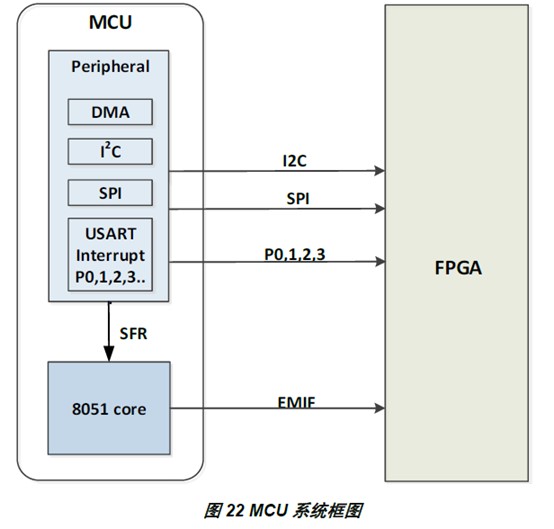

H1C02 系列FPGA 由增强型8051 处理器、嵌入式外设、SRAM、CCB 和时钟块组成,通过路由资源互连到FPGA。本小节主要对HME-H1C03 系列FPGA 特有的系统级功能进行介绍。

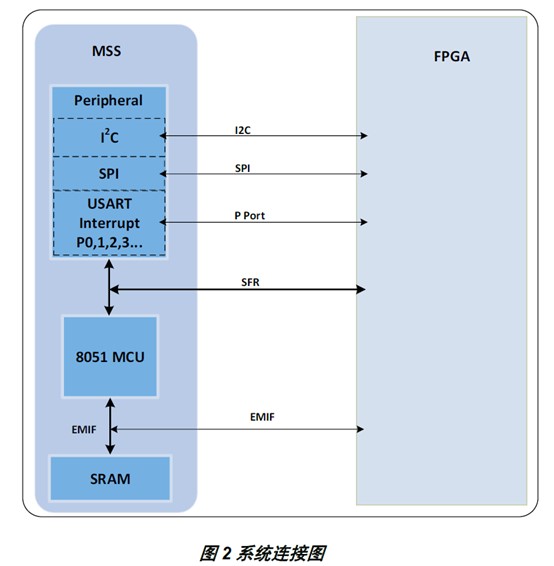

系统连接图如下所示:

嵌入式1Kx8b SRAM可以通过EMIF接口用作8051的代码和数据存储器,嵌入式存储模块(EMB)也可以通过EMIF接口用作8051的代码和数据存储器。

用户可以使用Fuxi IP向导实例化MCU IP,使外设连接到FPGA。系统可以使用的外设包括UART、SPI、I2C、端口、计时器及中断等等。

标准的8051 MCU具有128字节的特殊功能寄存器(Special Function Registers,SFRs),有些SFR未被硬核外设占用。用户可以使用SFR接口和这些未被占用的SFR来扩展定制外设或IP,然后MCU可以通过SFR操作FPGA实现的软核外设。

FPGA

HME-H1C02 系列FPGA 包含高达1536 个LUT,16 个EMB 4.5K 模块和2 个PLL。本章将逐一介绍这些模块。

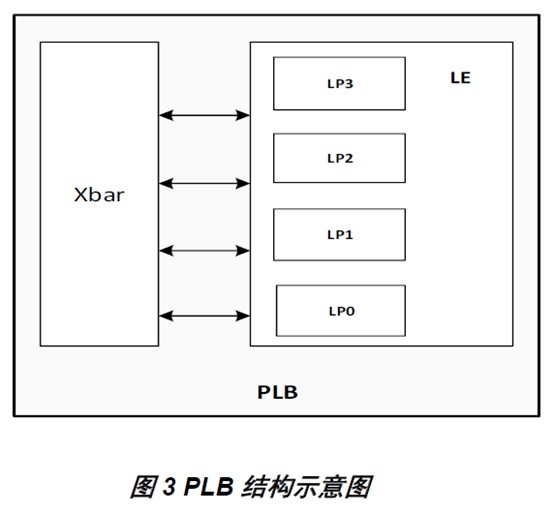

2.1 可编程逻辑模块(PLB)

可编程逻辑模块(Programmable Logic Block,PLB)是FPGA 的基本逻辑块,由LE 和Xbar 组成。其结构见下图所示。一个LE 包含4 个互联的LP(Logic Parcel,逻辑包)。LE 的逻辑资源用于实现时序和组合逻辑电路。

Xbar 可路由和传递各基本模块之间的信号。

2.1.1 逻辑模块(LP)

LP 是基本的可编程逻辑组件。LP 包括下列组件,通过这些组件可提供逻辑和算术功能:

3 个4 输入LUT 逻辑功能发生器

两个寄存器

进位、级联、移位和算术逻辑

(1) 查询表(LUT)

查找表(LUT/Look-Up Table)是一种基于RAM 的功能发生器,用于执行逻辑功能。LP 中的三个LUT 都包含四个逻辑输入(f0-f3)和一个单输出(d)。一个LUT 可执行任意四变量的逻辑操作。如需执行多个输入功能,可级联某个或邻近LUT 的LP。

(2) 寄存器

该寄存器是一种可编程的D 型触发器,也可以配置为T 型锁存器。寄存器的D 输入选择上有一个多路复用器。多路复用器可以选择LUT 组合输出,加法器输出或旁路信号。

(3) 进位,级联和算术逻辑

进位链与各种专用算术逻辑电路支持快速和有效的数学运算,例如加法器,计数器,比较器,乘法器, 宽逻辑运算等相关功能。软件综合工具能够自动利用这些进位链和逻辑电路实现算术运算,同时进位链和逻辑电路的逻辑门和多路复用器也可实现通用逻辑,如简单布尔运算。

2.1.2 LE

LE 包含4 个LP、跳级进位电路和寄存器控制电路。LE 可以实现具有快速进位逻辑的灵活进位功能, 以提高多字节加法器的速度。

2.1.3 互联

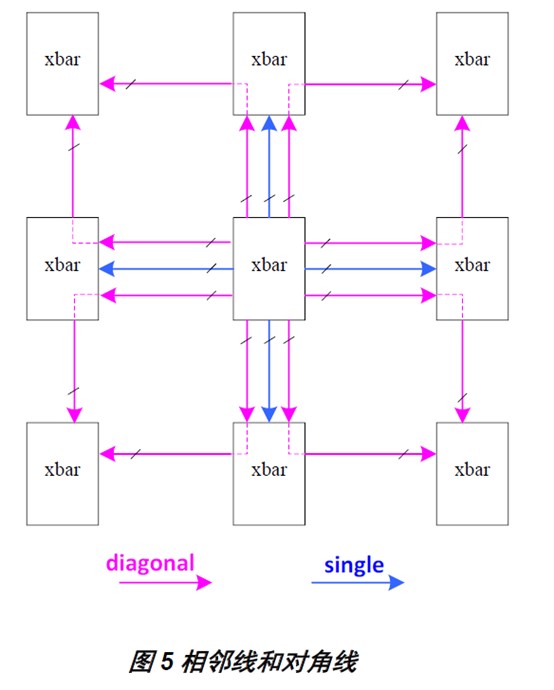

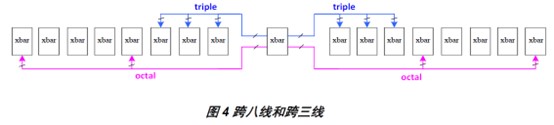

H1C02 系列器件的Xbar 为互联资源,通过Xbar 把各个模块连接成一个整体,模块之间通过Xbar 传递信号。Xbar 有四种互联方式为:跨八连线,跨三连线,相邻线和对角线。

跨八线水平及垂直方向上与相距8 个和4 个的基本模块的Xbar 相连(见下图)。

跨三线水平及垂直方向上与相距3、2和1个的基本模块的Xbar相连(见下图)。

相邻线和对角线通过水平及垂直方式直接连接相邻的Tile(见下图)。

2.2 嵌入式存储器模块(EMB)

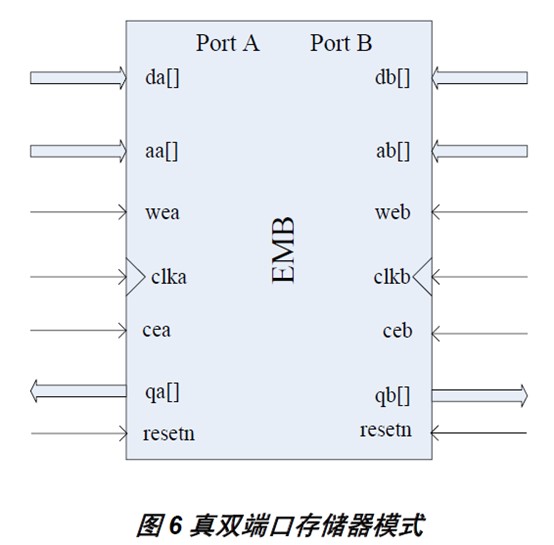

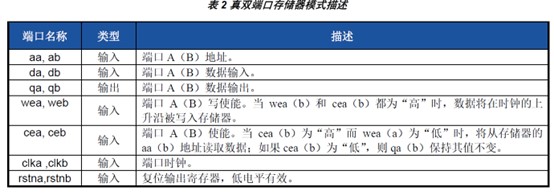

H1C02 系列器件支持嵌入式存储器模块(EMB),该EMB4.5K 模块排成一列。EMB4.5K 模块为真双端口存储器,允许独立访问两个端口。每个端口都有其专用的数据线,控制线和时钟线,用于同步读取和写操作。

EMB4.5K 具有以下功能:

4.5Kb

混合时钟模式

可以单独配置A,B 数据位宽

支持写优先、读优先和NO_CHANGE 模式

旁路或寄存器输出

奇偶校验位

EMB 模块支持每个存储字节都有一个奇偶校验位。通过奇偶校验位以及内部逻辑配资源,可以实现错误校正或者奇偶校验检查,以保证数据完整性的。奇偶校验位也可用作存储用户自定义的控制位。

支持初始化文件,在RAM和ROM模式下预加载存储器中的数据

初始化文件的格式为.hex 或.dat(dat 的格式:每行一个十六进制数,第一个数对应地址0 的值,以下行和地址依次对应)。初始化文件在配置过程中对EMB 存储器进行初始化。

支持以下三种存储器模式: - emb_tdp:真双端口

emb_sdp:简单双端口

- emb_sp:单端口

2.2.1 EMB操作模式

(1) EMB真双端口

EMB 支持双端口操作的任意组合:两个读操作,两个写操作,或不同时钟频率下一个端口读一个端口写操作。下图为真双端口存储器配置。

8051例化

从用户的设计角度来看,8051 IP 可被视作一个宏模块,类似于其它IP,如EMB4.5K 等,在代码中直接例化。

标准8051代码分页的原理和实现

H1C02内嵌的SRAM容量为1KB,存储空间较小,本文档描述的解决方案可以完全满足任何用户应用程序对程序空间的需求。相比其他芯片依靠不同型号来满足程序空间大小的需求,H1C02系列芯片可免除用户开发和量产选型的麻烦,降低用户成本,具有极大的优越性。

一个标准的8051器件能寻址64KB的代码空间。对于超过64KB的代码,单片机系统通常采用代码分页(CODE BANKING)的方式来扩展程序空间。

代码分页的机理就是将地址空间分成小于或等于64KB的不同代码段,通过片选的方式实现程序在不同代码空间的跳转。Keil C51工具支持代码分页这个技术,它可以管理一个公共的区域和32个代码页,每个代码页最大可达64KB,从而有共计2MB的代码切换空间

H1C02代码分页实现

3.1 原理介绍

H1C02程序和数据空间共享同一个的存储空间,用户使用时切记不要把数据和程序空间重叠。

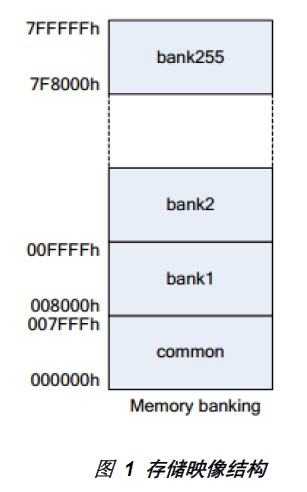

H1C02代码分页存储映像如图1所示。这种存储映像结构不需要每个bank都复制一份common公用代码,存储空间的利用率达到100%。

H1C02内嵌4Mbit的SPI接口的Flash,而它的配置文件一般占用0-0x10000字节空间,其他空间可用作用户的数据区。H1C02内嵌的SRAM只有1KB,存储空间是远远不够的。

基于H1C02上述特点,可以用SPI Flash实现代码分页,只需要在FPGA逻辑里实现对SPI Flash的读和8051的地址到SPI Flash程序区地址的转换。

3.2 SPI Flash实现代码分页

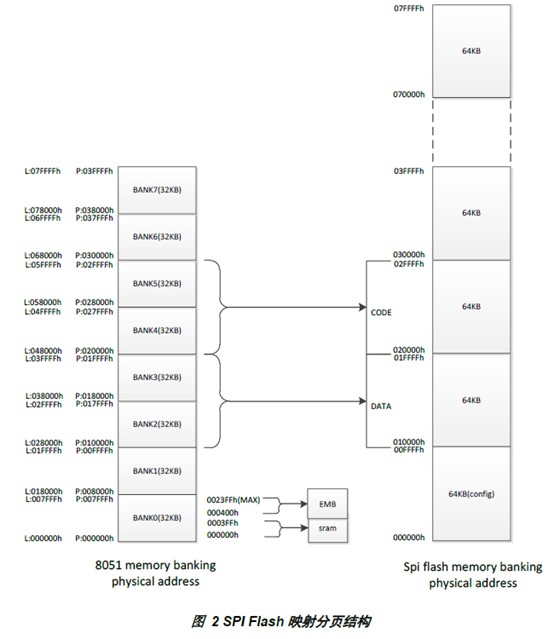

8051物理地址到SRAM、EMB和SPI Flash的物理地址分页结构如图2所示,其中,P代表物理地址,L代表逻辑地址。

3.2.1 Keil 设置

- Keil Target Options 选项设置

❑ 设置Code Banking:勾选Use Extended Linker (LX51) instead of BL51,该设置要求在工程中加入L51_BANK.A51;off-chip code memory,off-chip xdata memory 大小可根据上图中SRAM、EMB 的地址空间进行分配。

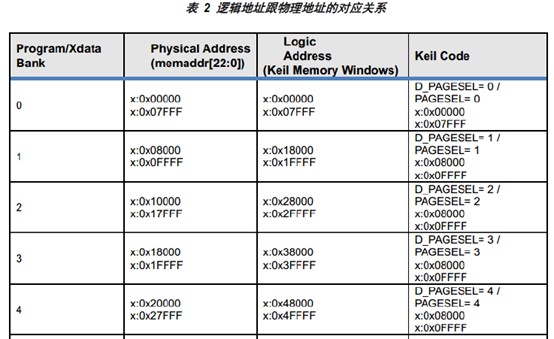

❑ 勾选Code Banking:设置Banks 数目,Bank Area 起始地址设为0x8000(逻辑地址,逻辑地址跟物理地址的对应关系如表 2 所示),对应H1C02 扩展SPI Flash 空间的起始地址。

设置output hex输出:勾选Merge32K Hexfile,选择HEX-386。

❑ User选项设置:After build run #1 C:\2020-03-19-win64-rel-606\bin\hexsplitter.exe -h read_spi_code.hex -b {-o sram.hex -s 0x00000000 -e 0x00000000} -b {-o flash.hex -s 0x00020000 -e 0x00020000 -z}把read_spi_code.hex通过工具拆分为2个hex,其中,sram.hex作为8051sram的初始化文件,flash.hex烧写到SPI Flash起始地址为0x20000的空间。

❑ Debug选项设置:Use HME 8051 Emulator:Settings:Set code memory as ROM,用ROM方式在线调试,支持4个硬件断点。

L51_BANK.A51设置和修改❑ ?B_NBANKS EQU 8;定义最大bank数

❑ ?B_MODE EQU 4;选用用户自定义模式

下面的代码用于控制bank切换时,写相应的bank值到PAGESEL。

PAGESEL DATA 94H ; page select

;

SWITCH0 MACRO ; Switch to Memory Bank #0

MOV PAGESEL, #1

ENDM

;

SWITCH1 MACRO ; Switch to Memory Bank #1

MOV PAGESEL, #1

ENDM

;

SWITCH2 MACRO ; Switch to Memory Bank #2

MOV PAGESEL, #2

ENDM

;

SWITCH3 MACRO ; Switch to Memory Bank #3

MOV PAGESEL, #3

ENDM

;

SWITCH4 MACRO ; Switch to Memory Bank #3

MOV PAGESEL, #4

ENDM

;

SWITCH5 MACRO ; Switch to Memory Bank #3

MOV PAGESEL, #5

ENDM

;

SWITCH6 MACRO ; Switch to Memory Bank #3

MOV PAGESEL, #6

ENDM

;

SWITCH7 MACRO ; Switch to Memory Bank #3

MOV PAGESEL, #7

ENDM

文件bank设置

在Target1中,使用Add Group建立多个Group。右键点击后,在选项Options for Group中设置该Group的Bank号。

Bank号从0开始,共享的文件和函数放在Common区,建议将没有速度要求的函数,或者不含跳转指令的函数放入bank4、5中(对应总线起始地址memaddr为0x20000,SPI Flash起始地址为0x20000)。在调用bank4、5函数前,S6的最低位要设成0。

超出SRAM、EMB存储空间data设置

将data(类似i2c数据)通过fuxi agdbg下载到SPI Flash起始地址为0x10000的空间。

|

Keil中在固定memory定义数组如下所示:U8 array1[1] _at_ 0x8000; |

|

U8 array2[2] _at_ 0x8001; |

|

U8 array3[6] _at_ 0x8003; |

|

U8 buffer[12] _at_ 0x8009; |

3.2.2 Hex文件拆分和下载

- 将Keil编译生成的sram.hex作为8051sram的初始化文件,然后使用Fuxi编译生成acf文件。

- Keil编译生成的flash.hex,将会烧写到spi flash起始地址为0x20000的空间。

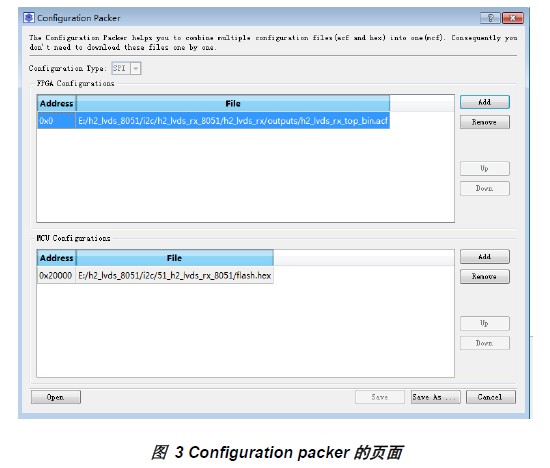

- 使用Fuxi->tools->configuration packer工具软件,将acf文件和flash.hex文件生成mcf文件,操作如图4所示。

用download工具,先擦除,然后下载上面生成的mcf文件。

- 打开Fuxi->tools->command-line window,输入命令agdbg -fls_w -addr <address,HEX> -c <byte number, DEC> -data <data, HEX>,例如往flash地址0x10000写入9个数据,agdbg –fls_w –addr 10000 –c 9 –data 112233445566778899。

- 按下开发板上reconfig按钮,使用Keil在线调试,观察功能是否正确。

这样就能完美的在片内结合MCU及FPGA 了....

评论