一、I2C 驱动介绍

1.1、I2C 协议

I2C是我们在MCU开发时时常会用到的通讯接口,用来与一些字符型设备进行通信,比如:陀螺仪、温度传感器等等,同样的在Linux下I2C驱动也是十分重要的。

以下为 I2C 协议内容:

(1)、I2C (Inter-Integrated Circuit,内置集成电路),同步(SCL控制) 串行(按位传输)接口。

两线协议-----时钟线和双向数据线,SCL (Serial CLock,串行时钟)和SDA (Serial Data,串行数据)。

主从协议-----通信双方为主机适配器( 主控制器)和客户设备(从设备)。

特点:交换数据总量少;数据传输率低;标准传输频率为100KHZ、400KHZ;

下图为 I2C 硬件示意图:

1.2、I2C 时序

(1)、时序图可以看到它的一个完整时序,包括开始时序、发送地址8位地址、发送应答、接收数据地址8位、接收应答、停止时序。

(2)、必须是起始信号为开始条件,结束信号为传输的停止条件。在这两个条件的中间做发送或者接收字节。

其中看到第一发送时序,是SCL高电平期间,SDA数据线是由高电平到低电平的一个变化,最后需要释放SCL的数据总线。

下图是 I2C 总线信号时序图:

I2C传输的要点就是: 传输一个字节 后面必然紧跟一个"响应"信号----应答信号.这个响应信号可能来自主机,或者是从机,具体是谁,就要看传输方向。

传输方向分两种情况(每种情况又有两种可能: A无应答和 B有应答):

1.主机->从机,主机对从机发一个字节之后,主机要读取从机的响应信号(主机读SDA线)

- A) 主机读SDA为高电平,说明从机无应答(意味着从机接收完毕,主机发送停止信号)

- B) 主机读SDA为低电平,说明从机有应答。(可继续发送下一个字节)

2.从机->主机, 主机读取从机一个字节之后,主机要向从机发送一个响应信号(主机写SDA线)

A) 主机写SDA为高电平,从机收到主机的无应答信号之后,从机停止传输,等待主机的停止信号。

B) 主机写SDA为低电平,从机收到主机的应答信号之后,从机继续输出下一字节

了解了相关的 MCU 的 I2C 功能后,下面开始介绍开始对相关的开发过程做介绍。

1.3、I2C 时序Linux 内核

相关概念解释:

I2C设备驱动:即挂接在I2C总线上的二级外设的驱动,也称客户(client)驱动,实现对二级外设的各种操作,二级外设的几乎所有操作全部依赖于对其自身内部寄存器的读写,对这些二级外设寄存器的读写又依赖于I2C总线的发送和接收

I2C总线驱动:即对I2C总线自身控制器的驱动,一般SOC芯片都会提供多个I2C总线控制器,每个I2C总线控制器提供一组I2C总线(SDA一根+SCL一根),每一组被称为一个I2C通道,Linux内核里将I2C总线控制器叫做适配器(adapter),适配器驱动主要工作就是提供通过本组I2C总线与二级外设进行数据传输的接口,每个二级外设驱动里必须能够获得其对应的adapter对象才能实现数据传输

I2C核心:承上启下,为I2C设备驱动和I2C总线驱动开发提供接口,为I2C设备驱动层提供管理多个i2c_driver、i2c_client对象的数据结构,为I2C总线驱动层提供多个i2c_algorithm、i2c_adapter对象的数据结构

以上是基于 Linux 内核的 I2C 驱动开发相关概念,作为常见的概念参考。

1.4、MCU 的 I2C 开发

如何在 MCU 中实现 I2C 功能开发,参考如下内容,讲述比较详细也非常清楚:

(原创) 巩固理解I2C协议(MCU,经验) - Booting - 博客园 (cnblogs.com)

1)、主器件向从器件读数据。

2)、 协议的程序实现

2.1)、 基本配置和宏定义

2.2)、 I2C通信建立

2.3)、 主器件向从器件写一个字节数据(带应答信号检验)

2.4)、 主器件从从器件接收一个数据

2.5)、 主器件回复应答信号0(ACK)

2.6)、 主器件回复应答信号1(NO ACK)

2.7)、 主器件向从器件写入数据

2.8)、 主器件从从器件读入数据

3)、 实际程序验证

二、E3 中I2C 驱动开发

对于 Semidrive 的 E3 系列而言,在如下官方地址进行下载相关的 Datasheet :

E3的系列如下:由于我们使用的是 E3103F2 这颗芯片,故选择 E3100_MCU_Datasheet_Rev00.07

中 I2C 的相关资料。

《E3400_E3600_MCU_Datasheet_Rev00.09》

《E3300_MCU_Datasheet_Rev00.09》

《E3648_MCU_Datasheet_Rev00.05》

从 E3100_MCU_Datasheet_Rev00.07 中可以看到芯片的功能模块如下:

E3100系列集成了 Cotex-R5F 的CPU,还有支持外设:LIN/UART/CAN/I2C等,以及功能安全 HSM 等。这里 Peripherals中总共有 I2C x 4:4组 I2C 的接口

Datasheet 中对 I2C相关资料如下:

(1)、I2C 的功能:Feature

Main features of I2C are as below:

- Supports 32bits APB 3.0 Slave interface.

- Supports the following speed modes:

– Standard Speed (100KHz), Fast Speed (400KHz), Fast-Plus Speed (1MHz)

– Supports High Speed mode (5MHz)

– Supports Ultra-Fast Speed mode (5MHz)

- Supports the following operation modes:

– I2C Master

– I2C Slave

– FIFO Test

- Compliant to I2C bus specification, version 6.0

- Compliant to SMBus specification, version 3.1

– ARP-capable

– Bus timeout detection

- Compliant to PMBus specification, version 1.3

- Supports DMA operation

- Shared TX/RX FIFO

– FIFO size: 64 (depth) * 8 (width)

(2)、功能接口 Block Diagram

The high-level block diagram of I2C is as below:

The sub-block function is as follows:

- BUSCTL

Handles APB Bus read/write access to CSR (Control/Status Regsiters) and FIFO.

- APB CMDG Generator

Triggers APB command and generate read/write transfer on I2C transfer.

- Register File

Stores I2C control & status registers.

- Shared TX/RX FIFO

APB domain sync FIFO which is shared by TX and RX.

- DMA Interface Control

Provides the request/handshake/control interface to DMA controller.

- Clock Generator

Generates I2C peripheral clock which includes prescaler logic and also control the clock

gating of sub-modules.

- Protocol Engine State Machine

– Controls the receiving/transmitting of address/control/Data/Byte Count/PEC bytes.

– Controls ACK/NACK handshake receiving/transmitting.

– Monotors I2C bus for multi-master arbitration (Bus Lost detection).

– Holds SCL line LOW when transmit data not ready or no empty to receive new data.

– Interrupts Generation logic for address/control/Data/Byte Count/PEC bytes received.

- CDC sync

– Handles the clock domain cross between i_pclk and i_sclk.

- IOCTL

– TX/RX Shift register control logic

– TX/RX Bit/Byte Counter

– START/RESTART/STOP/Address/Data bit transmit/detect

– ACK/NACK handshake receive/transmit

– I2C bus line input sychronizer

– Spike mask logic (noise filter)

(2)、工作模式:

This section introduces the programming model in I2C.

9.3.3.1 Controller Initialization

Software flow for Controller initialization:

- Set MCR0.MODEN to 0x0 (disable module)

- Reset module by set MCR0.MODRST to 0x1

- Wait software reset auto clear (MCR0.MODRST)

- Configure following register fields:

9.3.3.2 Trigger I2C Transfer by APB command

Software flow to trigger an I2C transfer by APB command:

9.3.3.3 Abort I2C Transfer by APB command

Software flow to abort an I2C transfer by APB command:

- Write CMDCSR0 register and setting following field:

– Write Doorbell field (CMDCSR0.DOORBELL) with value 0xA5C3

- Wait for APB command abort interrupt or slave read/write transfer abort interrupt

9.3.3.4 Receive I2C Transfer on I2C bus

Software flow to response to received I2C transfer on I2C bus:

- Wait for address byte detected interrupts (such as

SLVWRREQDET/SLVRDREQDET/ADDRMATCH etc)

– Received address can be read in register CMDCSR2.TAR/CMDCSR2.TARTYP/CMDCSR3.TAR/

CMDCSR3.TARTYP.

– Received read/write type can be read in register CMDCSR2.RWB.

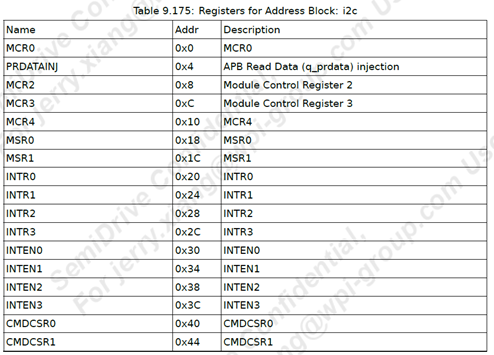

(3)、寄存器:

以下表格是对寄存器的描述

当然还有许多的寄存器,无法一一列举出来,功能及地址需要查看datasheet 进行比较。

熟悉硬件以后看看软件对其相关的设置

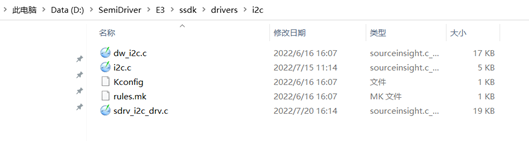

下图中为 SSDK 中 i2c 驱动部分程序:位置在 ssdk/drivers/i2c 文件夹中

i2c.c、i2c.h,dw_i2c.c是I2C核心的实现;

sdrv_i2c_drv.c 实现了I2C适配器设备文件的功能,每一个I2C适配器都被分配了一个设备

三、内容总结

本章主要介绍了 I2C 协议的相关概念,以及在 E3 芯片中的 I2C 模块,同时在E3的 SSDK 下可以看到 I2C 的驱动程序,受限于篇幅,在下一篇文章中会做详细的解释说明。

四、参考资料

【1】《E3100_MCU_Technical_Reference_Manual_Rev00.03.pdf》

【2】《极Linux驱动开发(十八):I2C驱动》

https://blog.csdn.net/a568713197/article/details/103280647

【3】《极Linux驱动开发(十八):I2C驱动》

https://blog.csdn.net/a568713197/article/details/103280647

评论