1.DDR测量神器——Interposer

众所周知,DDR系统属于高速接口。因此,为了确保SOC与DRAM之间的信号能正确传输,JEDEC针对各种信号(例如CLK、C/A、DQ、DQS)在时序、形状等方面进行了细致的规范。通常认为,满足这些规范是DDR接口能够正确运行的最低要求。如果希望系统在复杂多变的环境中能够保持良好的稳健性,则常常需要在满足底限要求的基础上额外预留一些裕量(Margin)。

在实际的电路设计中,无法避免测量信号。当优化DDR系统配置(例如Drive Strength/ODT)时,测量波形可以提供“所见即所得”的便利;当评估DDR接口的时序裕量(能反映稳定性)或PI/SI质量时,测量眼图是一种非常典型的方式;当DDR系统出错需要Debug时,测量接口上的信号常常能直接而有效地帮助问题定位。当然,对于某些任务,除了测量信号,还可以结合仿真、Shmoo等方式,本文暂不展开。

高速信号,应尽可能在靠近接收端的位置测量。这一点,在电磁场理论或信号完整性理论中均成立。一个直观的理解是:在高速电路中,信号的波长不再远大于电路尺寸,而是和电路尺寸相当(甚至更小),因此,信号在一根导线上各个位置的电压大小不能再视为相等。这意味着,在导线起点或中间某节点处测到的波形并不能代表导线终点处Rx接收到的波形。显然,低速电路中的基尔霍夫定律将不再适用于高速电路,人们常常采用传输线理论来分析高速电路,认为高速电路系统中传输的是功率(而非电压电流),任意节点的波形由入射波与反射波叠加共同决定。

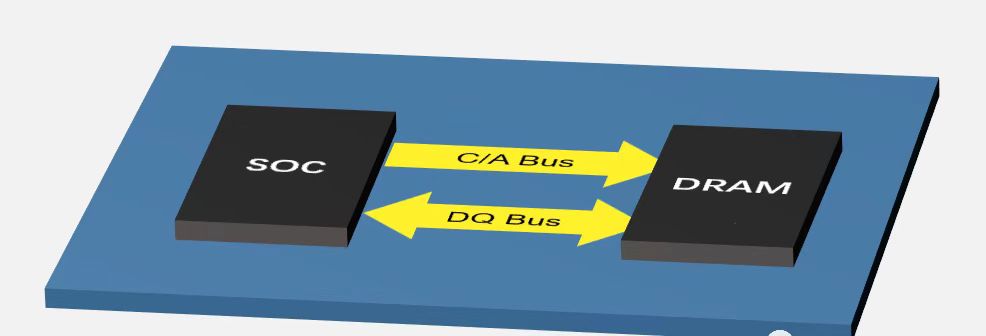

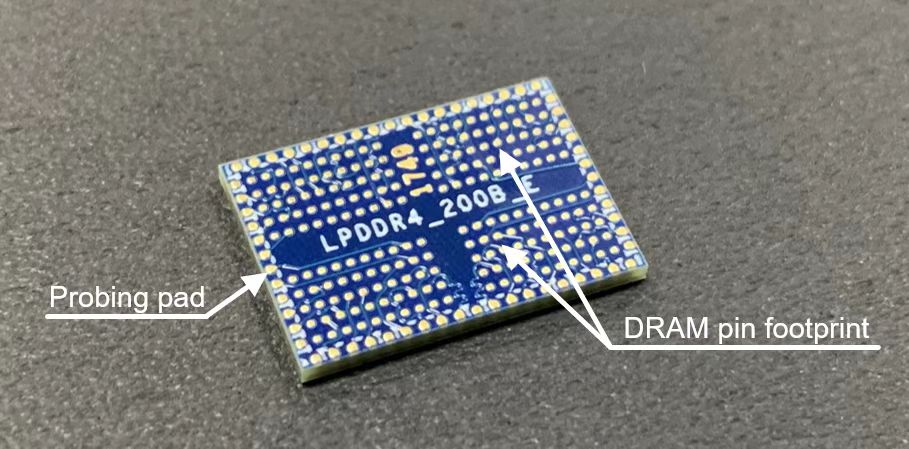

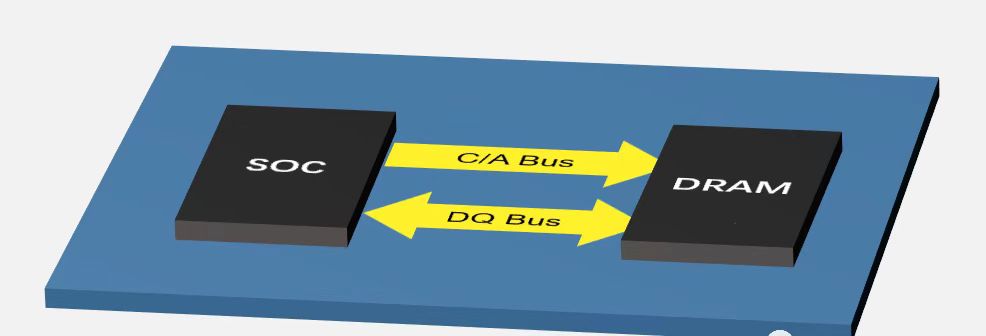

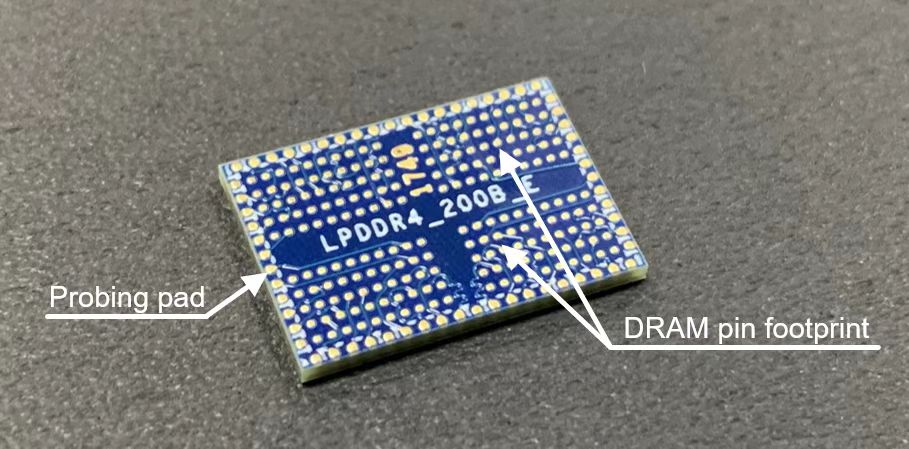

DDR接口的各种信号大致可划分为两类:Command Bus (单向,SOC发DRAM收)、Data Bus(双向,写操作时SOC发DRAM收,读操作时DRAM发SOC收)。对于写操作,所有信号的测量应尽可能靠近DRAM,显然,在引脚上测量的效果最佳。然而,现今的DRAM封装都是BGA类型,所有的引脚(Solder Ball)都位于芯片正下方(而非侧面),因此用示波器探头直接测量BGA引脚几乎是不可能的。为了解决该问题,目前主要有两种方案:(1)放弃在BGA引脚上测量,转而在PCB表层预留测试点;(2)在DRAM和PCB之间安装Interposer。方案(1)有诸多缺点:测量点距离原始引脚过远、通常只适用于表层走线的信号。我们通常更推荐方案(2),利用Interposer将测试点引出到DRAM Package外围。下图展示的是来自Micron公司的适用于LPDDR4/X的Interposer。

Interposer可以看成是一种转接板,安装在DRAM与系统板之间。在Interposer上下表面具有和DRAM一样的引脚Footprint,并且在内部用导线将上下表面的焊盘相应连通,从而可以保证Interposer的介入不影响DRAM与系统板之间的连接关系。此外,在Interposer最外围还有一圈Probing Pad,它们分别(在Interposer内部)连接到若干待测信号上,从而使得信号测量成为可能。这些规整的测量点使得示波器探头的焊接也变得更容易。

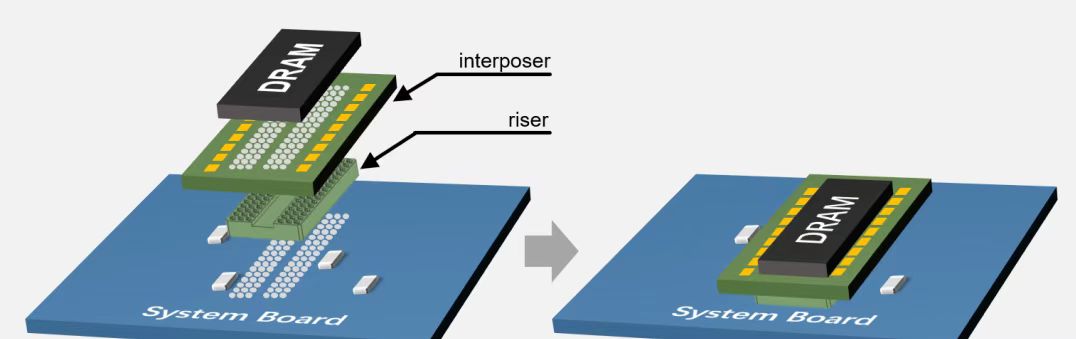

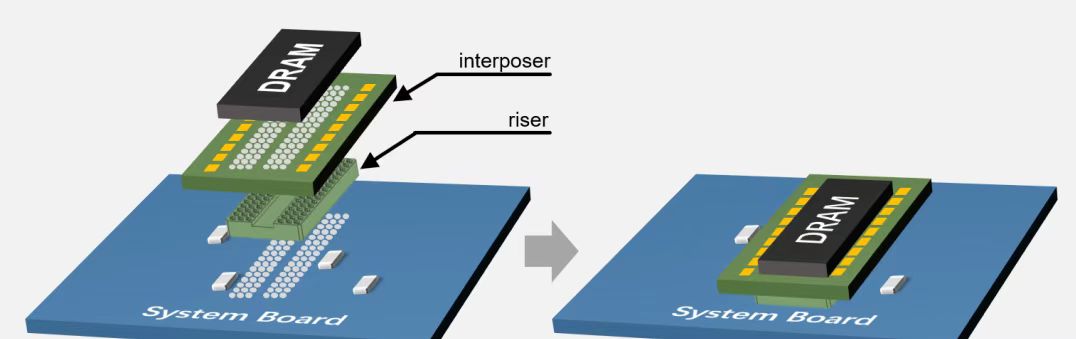

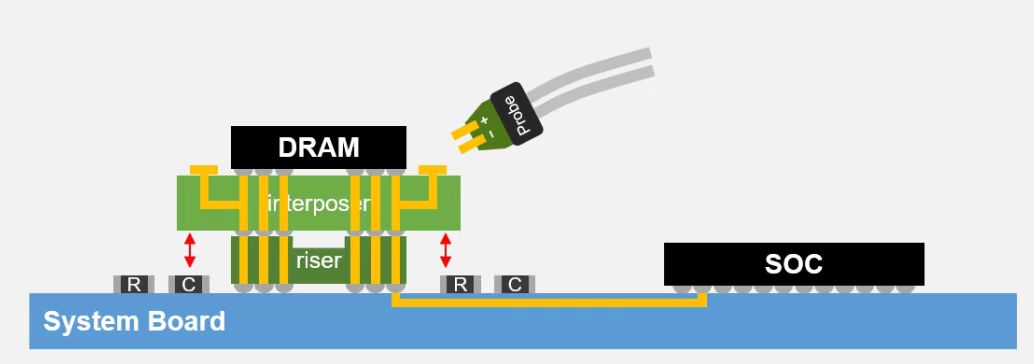

因为Probing Pad的存在,Interposer的尺寸显然要比DRAM Package大一圈。如果系统板上DRAM旁边摆放有阻容,则可能会导致Interposer无法直接贴合到系统板上。为了避免Interposer和阻容在空间上的冲突,有时还需要用到垫高板(Riser),它的结构和Interposer类似(能够实现信号上下贯通),只是没有引出测量点。

众所周知,DDR系统属于高速接口。因此,为了确保SOC与DRAM之间的信号能正确传输,JEDEC针对各种信号(例如CLK、C/A、DQ、DQS)在时序、形状等方面进行了细致的规范。通常认为,满足这些规范是DDR接口能够正确运行的最低要求。如果希望系统在复杂多变的环境中能够保持良好的稳健性,则常常需要在满足底限要求的基础上额外预留一些裕量(Margin)。

在实际的电路设计中,无法避免测量信号。当优化DDR系统配置(例如Drive Strength/ODT)时,测量波形可以提供“所见即所得”的便利;当评估DDR接口的时序裕量(能反映稳定性)或PI/SI质量时,测量眼图是一种非常典型的方式;当DDR系统出错需要Debug时,测量接口上的信号常常能直接而有效地帮助问题定位。当然,对于某些任务,除了测量信号,还可以结合仿真、Shmoo等方式,本文暂不展开。

高速信号,应尽可能在靠近接收端的位置测量。这一点,在电磁场理论或信号完整性理论中均成立。一个直观的理解是:在高速电路中,信号的波长不再远大于电路尺寸,而是和电路尺寸相当(甚至更小),因此,信号在一根导线上各个位置的电压大小不能再视为相等。这意味着,在导线起点或中间某节点处测到的波形并不能代表导线终点处Rx接收到的波形。显然,低速电路中的基尔霍夫定律将不再适用于高速电路,人们常常采用传输线理论来分析高速电路,认为高速电路系统中传输的是功率(而非电压电流),任意节点的波形由入射波与反射波叠加共同决定。

DDR接口的各种信号大致可划分为两类:Command Bus (单向,SOC发DRAM收)、Data Bus(双向,写操作时SOC发DRAM收,读操作时DRAM发SOC收)。对于写操作,所有信号的测量应尽可能靠近DRAM,显然,在引脚上测量的效果最佳。然而,现今的DRAM封装都是BGA类型,所有的引脚(Solder Ball)都位于芯片正下方(而非侧面),因此用示波器探头直接测量BGA引脚几乎是不可能的。为了解决该问题,目前主要有两种方案:(1)放弃在BGA引脚上测量,转而在PCB表层预留测试点;(2)在DRAM和PCB之间安装Interposer。方案(1)有诸多缺点:测量点距离原始引脚过远、通常只适用于表层走线的信号。我们通常更推荐方案(2),利用Interposer将测试点引出到DRAM Package外围。下图展示的是来自Micron公司的适用于LPDDR4/X的Interposer。

Interposer可以看成是一种转接板,安装在DRAM与系统板之间。在Interposer上下表面具有和DRAM一样的引脚Footprint,并且在内部用导线将上下表面的焊盘相应连通,从而可以保证Interposer的介入不影响DRAM与系统板之间的连接关系。此外,在Interposer最外围还有一圈Probing Pad,它们分别(在Interposer内部)连接到若干待测信号上,从而使得信号测量成为可能。这些规整的测量点使得示波器探头的焊接也变得更容易。

因为Probing Pad的存在,Interposer的尺寸显然要比DRAM Package大一圈。如果系统板上DRAM旁边摆放有阻容,则可能会导致Interposer无法直接贴合到系统板上。为了避免Interposer和阻容在空间上的冲突,有时还需要用到垫高板(Riser),它的结构和Interposer类似(能够实现信号上下贯通),只是没有引出测量点。

2.虚拟探测与De-embedding

在DDR3时代及以前,利用Interposer测量波形的方案能够很好地满足需求。然而,到了DDR4/LPDDR4时代,时钟频率达到了1600MHz甚至2133MHz,在信号测量过程中我们遇到了新的挑战。

前面提到,高速信号,应尽可能在靠近接收端的位置测量。并且,速度越高,这一需求越强烈。这带来一个疑问:BGA封装的Ball足够靠近电路的Receiver吗?或者说,在Ball上测量得到的波形,能够准确反映Die上看到的波形吗?对于LPDDR4(以及后续的LPDDR5),答案是否定的。随着工作频率的提升,信号翻转时间Tr需要不断缩短(不难理解,Tr相比于UI的占比应控制在某个值之下,否则有效眼宽无法保证),这意味着信号中的高频分量越来越多,阻抗匹配变得越来越难控制,从而不可避免地引起反射,导致一定程度的信号失真。信号完整性的相关理论告诉我们,一段传输线的时延TD(正比于传输线长度)相比于Tr越大,则反射引起的信号失真越明显(尤其是考虑到Ball的位置没有端接)。也就是说,随着Tr的缩短,在Ball上测到的波形越来越不能反映Die Pad上看到的波形。

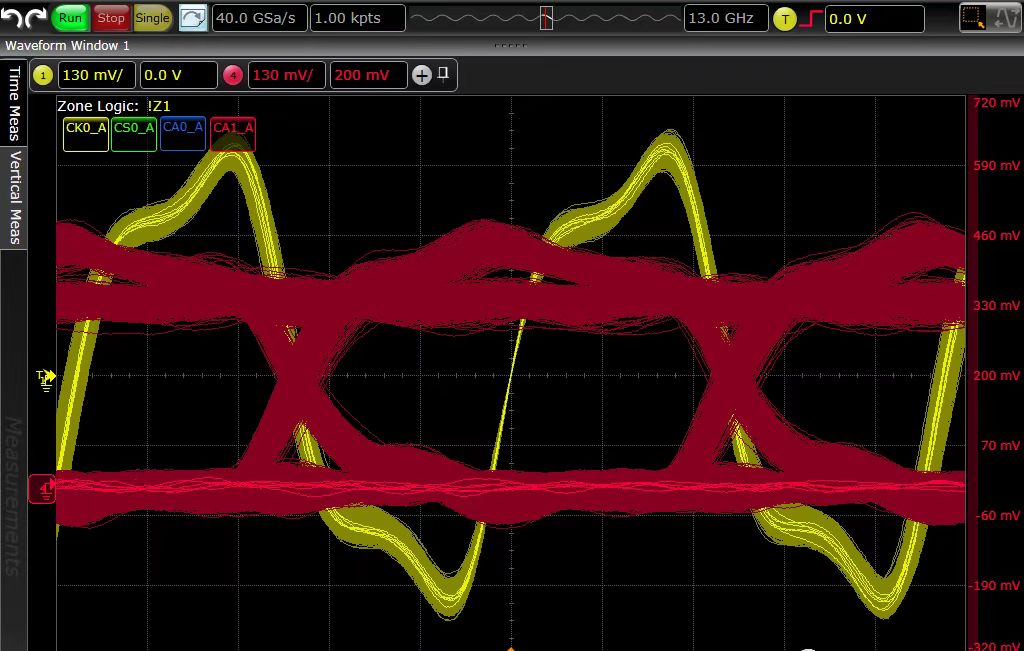

下图展示的是在Interposer的Probing Pad上测量得到的LPDDR4X的眼图(红色为CA,黄色为CK)。可以看到,波形存在明显畸变,这是因为在测量点处不但有来自SOC的入射波,还有来自DRAM的反射波(由于Cio、CA分支结构、Bonding-wire寄生电感等导致阻抗不匹配,从而引起反射)。测得的波形实际上是二者的叠加,因此并不能准确反映DRAM接收端看到的波形。

这里我们遇到了一个困境:在常规场景下我们不可能直接测量DRAM Die上的信号终端,而在DRAM BGA Ball上测得的波形又不能准确反映Die上看到的波形。为了解决这一问题,Keysight示波器提供了一个名为“InfiniiSim Waveform Transformation Toolset”的组件[1],它要求用户提供Probing Pad与Die Pad之间相关链路(例如:Interposer、DRAM Package)的S参数,该组件利用S参数可以计算出Probing Pad与Die Pad之间链路的传输函数,结合Probing Pad上测量到的波形以及该传输函数,即可推断/模拟出Die Pad上看到的波形。简而言之,该方案的原理是:在A点测量得到初始波形,利用A、B两点之间的传输函数,来模拟B点看到的波形。该方法常叫做虚拟探测(Virtual Probing)。

另外,我们知道,为了测量信号而额外引入的Interposer和示波器探头,它们本身对信号也会或多或少产生一些影响。如果我们想知道原始系统中的波形质量,则需要想办法把Interposer和示波器探头的影响“补偿”掉。该需求也可以基于上述Keysight组件,通过传输函数的方法来实现。该做法通常叫做去嵌(De-embedding)。

利用虚拟探测技术,尽管我们并未直接在Die上测量信号,但仍然能得到DRAM Die上看到的眼图波形(如下图所示)。

3.总结

DDR信号的测量通常需要用到Interposer。

随着信号上升时间Tr的缩短,在DRAM Package外部(例如Ball)测得的波形已经不能真实地反映DRAM Die实际看到的波形。利用虚拟探测技术可以更精确地评估信号质量。

评论