一、MIPI DSI 简介

MIPI DSI 是一种多功能的高速接口,主要用于智能手表、智能手机、汽车及其他平台的 LCD 屏。i.MX RT500 的 MIPI DSI 控制器实现了 MIPI DSI 规范中定义的所有功能,并提供了 MCU 与基于 DSI 接口的 LCD 屏之间的通信接口。

MIPI DSI 利用差分信号在 DSI 主机和显示模块之间进行时钟和数据的传输,其包含 1 条时钟 lane 和 1 ~ 4 条数据 lane。具体使用几条数据 lane 由应用中显示需要传输的数据量决定。RT500 中仅支持最大 2 条数据 lane。DSI 接口与传统的 RGB 并行接口相比,其数据线大大减少了,节省了很多硬件资源。

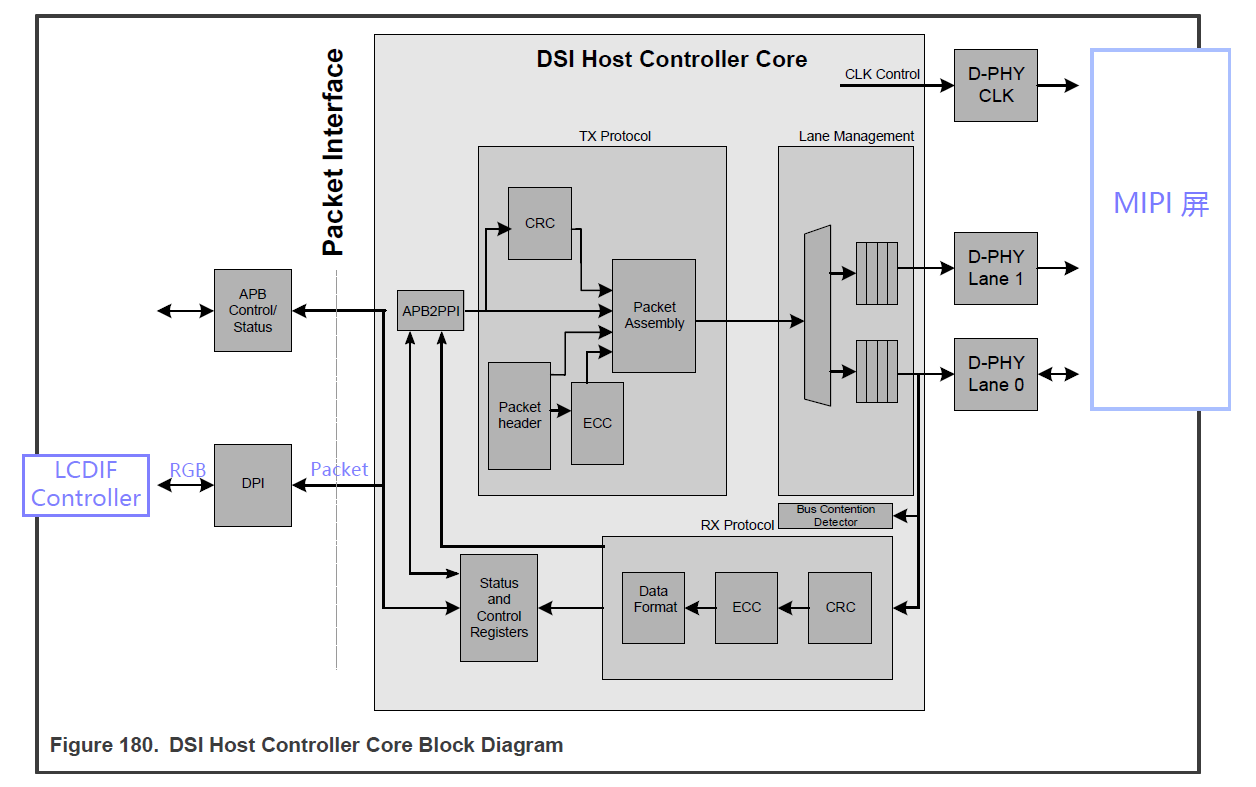

图 1. DSI 主机控制器框图

官方定义啥的这里就不介绍了,网上很多可以搜到,这些官方术语对刚接触 MIPI DSI 的朋友来说比较难以理解,所以下面用“人话”不太严谨地描述一下大概结构,便于有个大概印象,为后面的理解做铺垫。

一般的,我们用 MCU 接普通 RGB 接口的 LCD 时,多用 LCDIF 外设去接屏的 RGB 脚和各时钟信号、同步信号的脚。换成 MIPI 屏时,由于多了一层 MIPI DSI 协议,这里 MCU 的 LCDIF Controller 所产生的时序信号和像素数据(VSYNC,HSYNC,像素数据 等)就不能直接连接到 MIPI 屏,此时,就需要将 RGB 的信号先用 DPI 打包成 DSI 能识别的 packet,再将此 packet 送入 DSI Host 经一系列处理(应用层、低层协议层、lane 管理层 等)使其转化为符合 MIPI DSI 协议的物理信号(落实到最底层的物理层的 DPHY Clock、数据 Lane 信号),再将这些信号通过 MIPI DSI 接口传输给 MIPI 屏。

当然,这是大致的描述,细节上,MIPI DSI 有标准的协议,各层都有自己的规范。

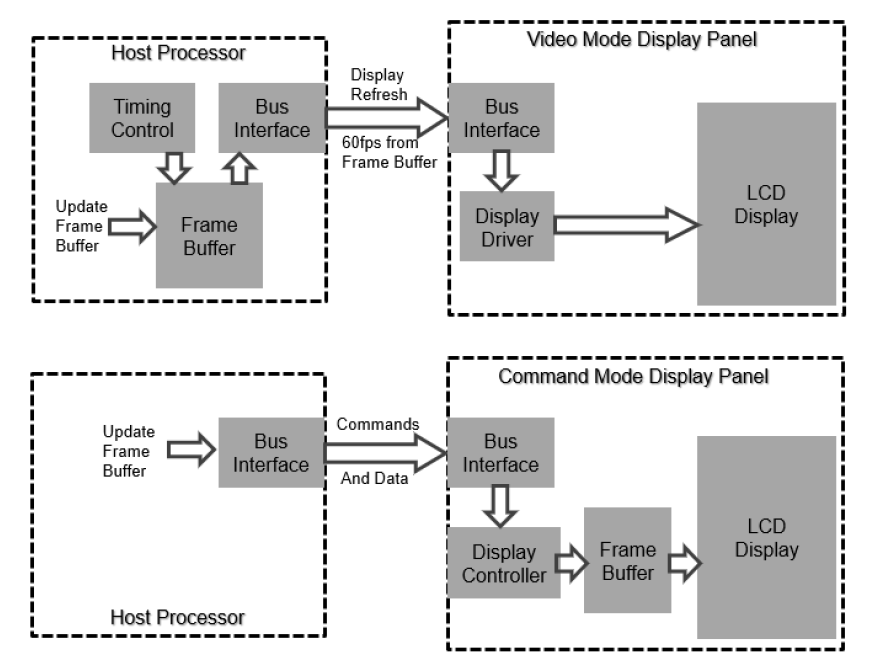

兼容 DSI 接口的 LCD 至少支持 Command 模式 和 Video 模式两种操作模式中的一种。至于实际使用哪种模式是根据具体 LCD 的结构和性能来决定的。我们后面举例所使用的就是 Video 模式的屏。

- Video 模式下主控制器到 LCD 间的数据传输是以实时像素流的方式进行的,且该像素流只能以 High-speed 模式进行传输。

- Command 模式下主控制器和 LCD 交换数据主要是通过发送命令和数据到 LCD 模块,该模块包含一个显示控制器,显示控制器包含本地寄存器和帧缓冲区。

图 2. Video Mode & Command Mode

此外,MIPI D-PHY 支持两种传输模式:High-Speed 模式(简称 HS 模式)和 Low-Power 模式(简称 LP 模式)。

- HS 模式用于高速同步数据传输,例如 Video 模式下的数据传输。HS 模式下的数据传输速率范围为 80 Mbps - 1.5 Gbps / lane。

- LP 模式主要用于控制命令传输,该模式也可用于低速异步数据传输。

二、MIPI DSI 时钟配置

这里我们以 RT500 EVK 接 720 × 1280 的 MIPI LCD 屏为例,该屏型号为 RK055HDMIPI4M (可在 NXP 官网搜到),屏的显示驱动为 RM68200。代码直接以 SDK_2_11_0_EVK-MIMXRT595 的例程 lvgl_demo_widgets_bm 为例,介绍 MIPI DSI 相关的时钟配置。

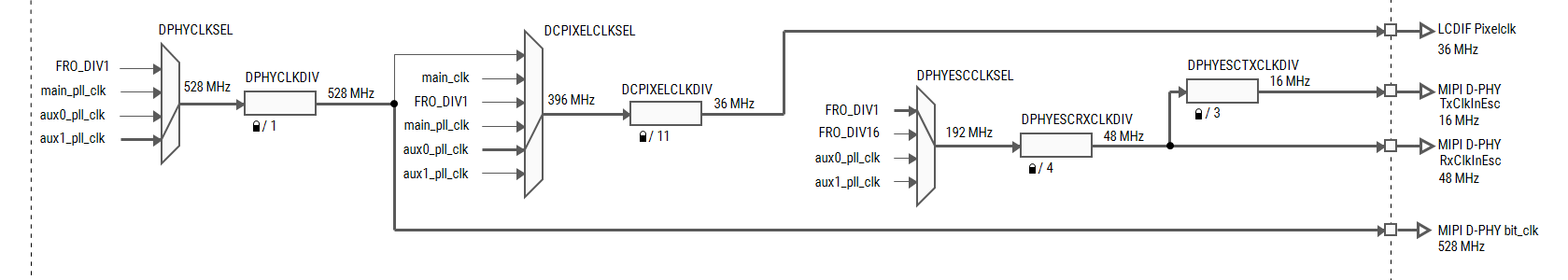

需要我们配置的时钟如下图,下面会分别介绍。

图 3. 相关时钟配置

2.1 Pixel_clock

该时钟为 LCDIF 相关的时钟,一般 RGB 接口中有 DCLK、VSYNC、HSYNC 等时序信号,其中 DCLK 就是这里的像素时钟。像素时钟与屏的分辨率和刷新率有关,计算公式如下:

Pixel_clock >= (Height + VSW + VFP + VBP) * (Width + HSW + HFP + HBP) * frame rate

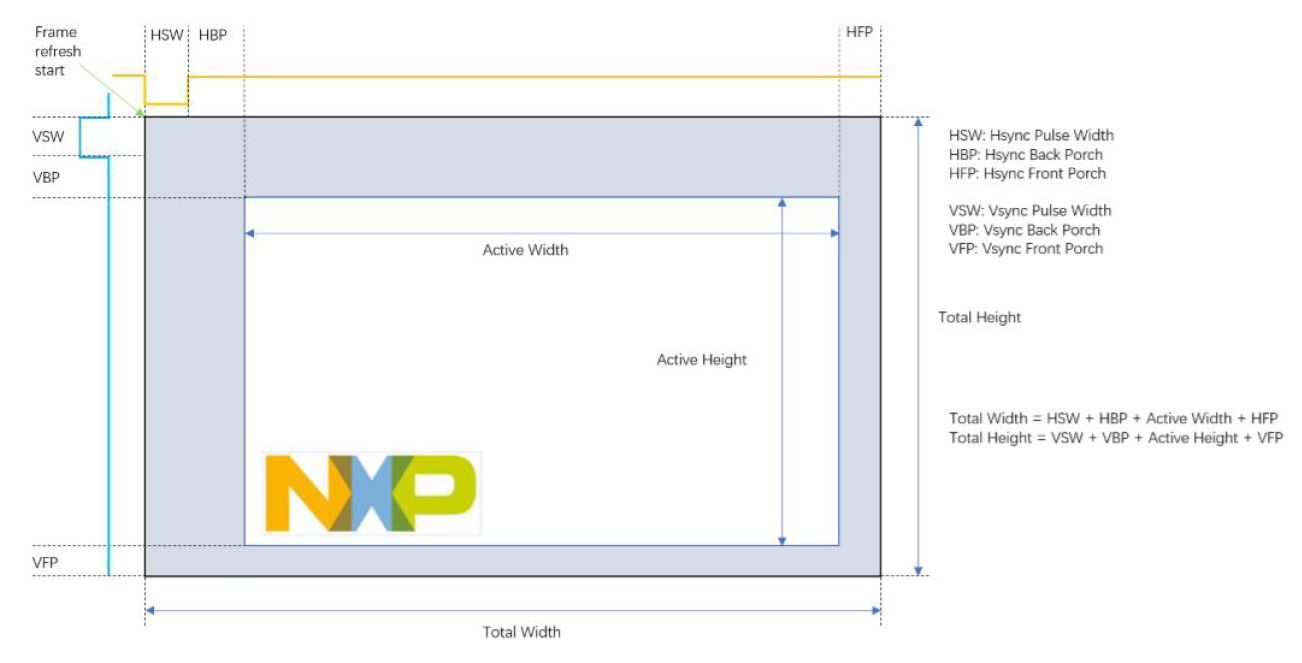

其中,Width = 分辨率的宽度,Height = 分辨率的高度。剩下的参数在屏的手册上可以找到,它们用于屏的时序信号同步,各参数含义如下图。

图 4. 屏时序参数的含义

对于 RGB 接口,在每个像素时钟沿(上升或下降),LCDIF Controller 从缓冲区中获取一个像素数据,将其转换为相应的像素格式(如 RGB888),并输出到 RGB 接口,然后,像素数据便会显示在 LCD 屏的有效区域上。下图是一帧画面数据显示过程的图解。

图 5. 一帧数据的显示过程

这些参数在屏的手册中会列出来,以我们使用的 720 * 1280 的屏为例,相关参数如下图。

图 6. 屏的时序参数

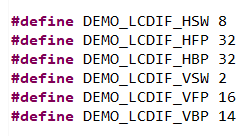

将这些参数代入到像素时钟的计算公式,即可计算出像素时钟。

Pixel clock = (Height + VSW + VFP + VBP) * (Width + HSW + HFP + HBP) * frame rate

= (1280 + 2 + 16 + 14) * (720 + 8 + 32 + 32) * 35Hz

= 36368640 Hz = 36.368640 MHz

在代码中,像素时钟的配置在函数 BOARD_InitLcdifClock() 中,这里是配置为了 36MHz,如下图所示。

图 7. Pixel clock

2.2 TxClkEsc & RxClkEsc

这俩是 MIPI DSI D-PHY 低功耗模式相关时钟。

TxClkEsc Clock:LP 模式发送时钟,该时钟信号的范围是12 MHz 至 20 MHz。

RxClkEsc Clock:LP 模式接收时钟,该时钟信号的最大值为 60 MHz。

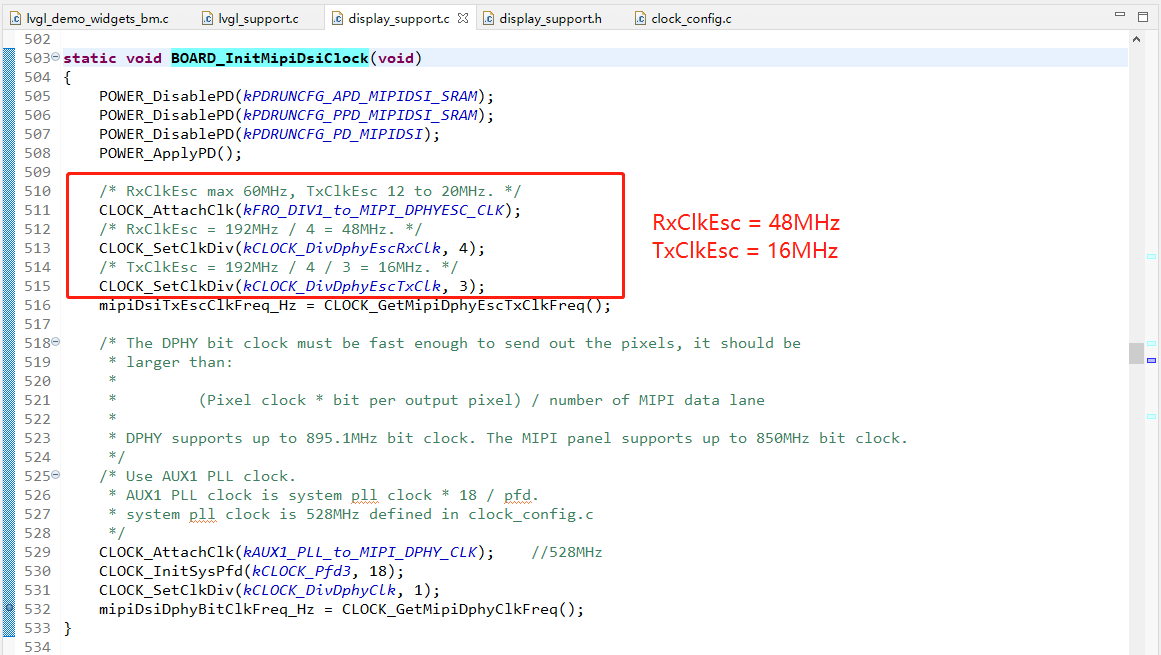

这里我们的屏取的是 RxClkEsc = 48MHz,TxClkEsc = 16MHz。在函数 BOARD_InitMipiDsiClock() 中配置,如下图。

图 8. RxClkEsc & TxClkEsc

2.3 Bit clock

Bit clock 是 MIPI DSI D-PHY 高速模式的相关时钟,用于数据 lane 的高速传输,与像素格式和数据 lane 的数量有关,计算公式如下:

Bit clock >= Pixel_clock * bit_per_pixel / MIPI_data_lane_numbers

这里我们使用 RGB565(16bit per pixel)颜色格式,数据线 lane 使用了 2 条,代入公式计算可得

Bit clock >= Pixel_clock * bit_per_pixel / MIPI_data_lane_numbers

= 36.368640 MHz * 16 / 2

= 290949120 Hz = 290.949120 MHz

这里 Bit clock 计算出来的是最小的值,实际设置要大于计算结果,不大到无法正常显示即可。

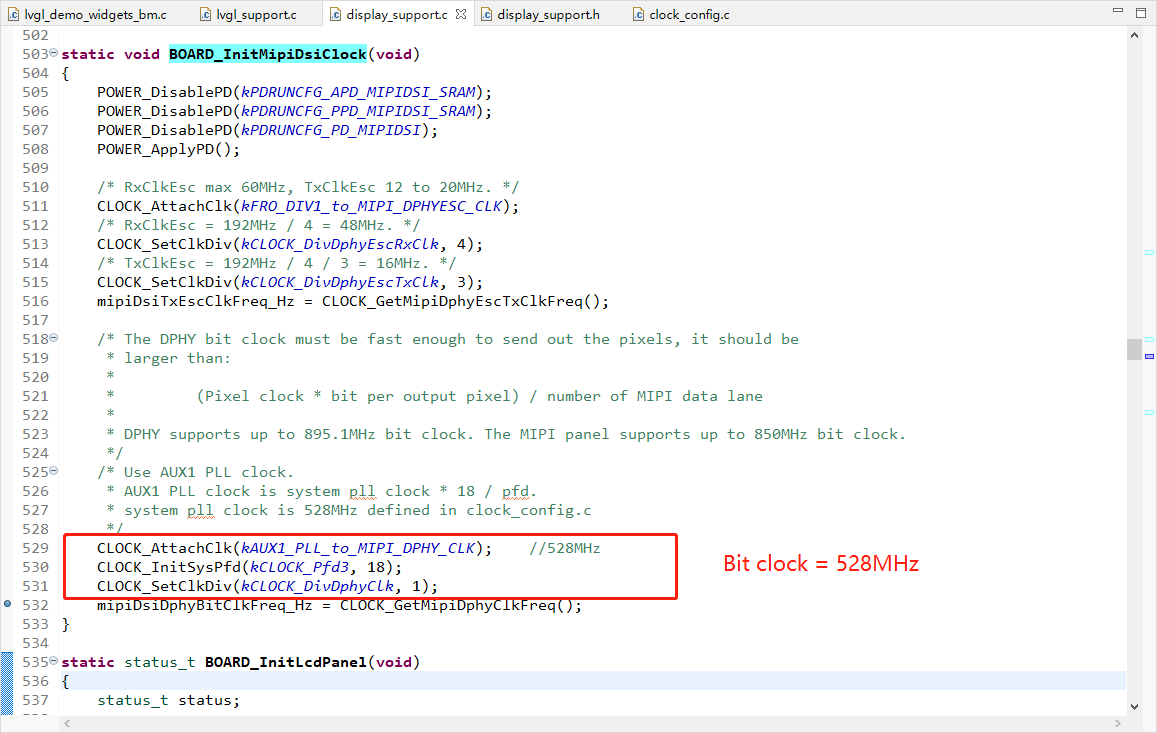

在代码中,Bit clock 也在函数 BOARD_InitMipiDsiClock() 中配置,这里是配置为了 528MHz,如下图。

图 9. Bit clock

三、参考资料

(1)IMXRT500RM.pdf,可在 NXP 官网下载:

https://www.nxp.com/webapp/sps/download/preDownload.jsp?render=true

(2)AN12302 - i.MX RT eLCDIF RGB Mode Use Case.pdf,可在 NXP 官网下载:

https://www.nxp.com.cn/docs/en/application-note/AN12302.pdf

(3)AN12940 - Use Case of RT1170 LCD Display System based on MIPI DSI.pdf,可在 NXP 官网下载: