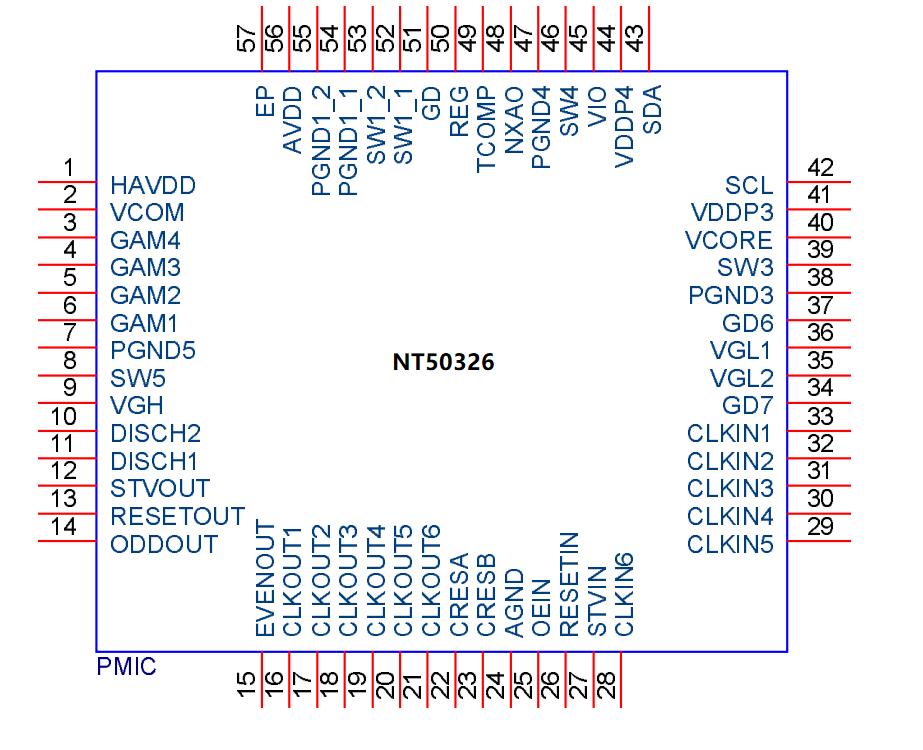

NOVATEK的NT50326属于一款非常成熟的产品,主要是由BUCK/BOOST电路、Gamma电路以及Lever shift三部分组成,下图是该PMIC的模型及pin脚定义:

首先咱们先来了解一下PMIC的后端技术。

1、PMIC 的研发阶段可分为两大部分,即前端设计和后端设计。

前端设计也称逻辑设计,包含规格制定、架构设计、针对模拟电路的门级电路设计和针对数字电路的硬件描述语言设计。 通过了份真验证,最后以形成完整逻辑电路和数字网表的形式交给后端人员作为前端设计完成的标识。

后端设计也称物理设计,包括版图绘制、工艺生产、封装测试等部分内容。 以芯片封装完成交付应用部门进行应用测试作为后端设计完成的标识。 当然在测试过程中发现问题,再返回到设计阶段修正或更改设计,重新生产、封装和测试,反复循环直至产品达到量产标准也是一个长期的过程。 PMIC 后端技术包括 EDA 工具的开发与应用、版图设计、生产工艺、封装技术等方面。

2、版图工具 (EDA Tools)

版图设计是后端设计中的重要组成部分。 版图工程师将设计完成的电路或数字代码转化成一系列几何图形,形成 GDSII 数据包括 IC 尺寸、各层的拓扑结构等有关器件的所有物理们息,交子工艺厂商进而生产出实际的半导体产品。 现今模拟集成电路版图仍以全定制为主,一款优秀的版图工具可以显著提高版图工程师的工作效率,同时也能得到更好的版图质量。

市面上主要有以下几款 IC 设计软件:

Virtuoso, 著名的 Cadence 公司的 IC 集成开发环境,包含版图编辑器 VirtuosoLE。 作为业界标准,其优点是功能强大完备,操作方便高效,界面友好漂亮,具有最广泛的应用支特等:缺点是价格昂贵,电脑软、硬件环境要求高,系统庞杂,工具众多,不易入手等。

Tanner Tools,美国 Tanner Research 公司开发的针对 PC Windows 平台的IC开发软件,其中包含版图编辑器L-Edil0,也是本项目的开发环境。 Tanner Tools 最大的特点是大大降低了软、硬件门槛,可在普通电脑的 Windows 环境中安装运行,而年许可证费用也大大低于 Cadence 和 Sysnopsys 等传统大牌公司。 其缺点是功能较之 Virtuoso 等工具少; 很少有工艺厂商会提供针对 Tanner Tools 的PDK包; 受限于软、硬件环境,软件稳定性和数据安全性等方面也亟待提高。

Aether, 是国内厂商华大九天开发的 IC设计软件,包含版图编辑器 Aether LET.

其优点是很好的国内客户支持,以及与国内工艺厂商都有广泛的合作,同时年许可费用更为低廉。 缺点是作为新兴 EDA 软件,知名度和信誉都还不够高,影响设计公司采用其产品,同时国际工艺厂商支持力度也不够。

评论