1.1 CapSense功能

PSoC 4和PSoC 6 MCU中的CapSense具有以下特性:

支持自电容和互电容触摸感应

功能强大的CapSense Sigma Delta(CSD)和CapSense Crosspoint(CSX)感应技术,能够为基于自电容和互电容的触摸感应提供一流的信噪比。

在覆盖材料和厚度不同的条件下仍能提供高性能感应(请参考CapSense基本原理、覆盖层材料和覆盖层厚度)

SmartSense™自动调试技术

接近感应的范围较大(接近感应距离可达30 cm)

防水功能(请参见防水功能)

伪随机序列(PRS)时钟源可降低电磁干扰(EMI)

功耗较低:工作电压低至1.71 V,休眠模式下的电流消耗低至150 nA

所有GPIO引脚都支持电容式感应和屏蔽1

允许将CapSense模块重新配置为ADC,并且所有GPIO引脚都支持ADC输入1

通过使用可编程参考电压(VREF),可提供优越的信噪比

支持用于降低电磁干扰(EMI)的扩频和可编程电阻开关

在CapSense扫描过程中,通过将初始化和配置过程分担给CapSense序列发生器,可降低CPU开销。

与PSoC 4100S器件相比,PSoC 4100S Plus器件具有以下附加功能:

提供更大的闪存存储器和更多的I/O

提供一个控制区域网络(CAN)模块

为加密应用提供用于安全密钥生成的真随机数

接受4至33 MHz频率范围的外部晶振(ECO)

1.2 PSoC 4和PSoC 6 MCU CapSense Plus特性

您可创建带有电容式触摸感应和其他系统功能的PSoC 4 CapSense Plus应用。 除了CapSense外,这些器件还有以下关键特性:

带单周期乘法的ARM® Cortex®-M0/M0+CPU,其工作频率为48 MHz,并且它的指令执行速度高达43 DMIPS

在环境温度范围为–40至85 °C中,工作电压范围为1.71 ~ 5.5 V

高达128 KB的闪存空间(CM0+的代码容量超过了采用8位解决方案的芯片的代码容量两倍)

高达16 KB的SRAM

多达94个可编程GPIO

独立的中心对齐PWM,其特点包括互补死区可编程输出、已被同步化的ADC操作(在PWM周期中用户可指定的时间内触发ADC的能力)和同步刷新(在所有的PWM上对PWM占空比变化进行同步化操作,以避免发生异常波形)

基于比较器的PWM停止(Kill)信号触发(以便在检测到过电流条件时终止电机驱动)

PSoC 4和PSoC 6 MCU中的CapSense具有以下特性:

支持自电容和互电容触摸感应

功能强大的CapSense Sigma Delta(CSD)和CapSense Crosspoint(CSX)感应技术,能够为基于自电容和互电容的触摸感应提供一流的信噪比。

在覆盖材料和厚度不同的条件下仍能提供高性能感应(请参考CapSense基本原理、覆盖层材料和覆盖层厚度)

SmartSense™自动调试技术

接近感应的范围较大(接近感应距离可达30 cm)

防水功能(请参见防水功能)

伪随机序列(PRS)时钟源可降低电磁干扰(EMI)

功耗较低:工作电压低至1.71 V,休眠模式下的电流消耗低至150 nA

所有GPIO引脚都支持电容式感应和屏蔽1

允许将CapSense模块重新配置为ADC,并且所有GPIO引脚都支持ADC输入1

通过使用可编程参考电压(VREF),可提供优越的信噪比

支持用于降低电磁干扰(EMI)的扩频和可编程电阻开关

在CapSense扫描过程中,通过将初始化和配置过程分担给CapSense序列发生器,可降低CPU开销。

与PSoC 4100S器件相比,PSoC 4100S Plus器件具有以下附加功能:

提供更大的闪存存储器和更多的I/O

提供一个控制区域网络(CAN)模块

为加密应用提供用于安全密钥生成的真随机数

接受4至33 MHz频率范围的外部晶振(ECO)

1.2 PSoC 4和PSoC 6 MCU CapSense Plus特性

您可创建带有电容式触摸感应和其他系统功能的PSoC 4 CapSense Plus应用。 除了CapSense外,这些器件还有以下关键特性:

带单周期乘法的ARM® Cortex®-M0/M0+CPU,其工作频率为48 MHz,并且它的指令执行速度高达43 DMIPS

在环境温度范围为–40至85 °C中,工作电压范围为1.71 ~ 5.5 V

高达128 KB的闪存空间(CM0+的代码容量超过了采用8位解决方案的芯片的代码容量两倍)

高达16 KB的SRAM

多达94个可编程GPIO

独立的中心对齐PWM,其特点包括互补死区可编程输出、已被同步化的ADC操作(在PWM周期中用户可指定的时间内触发ADC的能力)和同步刷新(在所有的PWM上对PWM占空比变化进行同步化操作,以避免发生异常波形)

基于比较器的PWM停止(Kill)信号触发(以便在检测到过电流条件时终止电机驱动)

12位的1 Msps ADC,具有“采样和保持”(S&H)功能,且无需序列开销,因而,可将整个ADC带宽使用于信号转换,而无需将其用于定序器开销

具有比较器模式和SAR输入缓冲能力的运算放大器

Segment LCD直接驱动器支持4个共用引脚

T/I2C串行通信通道

蓝牙低功耗(BLE)通信与版本4.0和版本4.1的多项特性相兼容。

可编程的逻辑模块,每个模块包括八个宏单元和一个可级联的数据路径(即为通用数字模块(UDB)),用于有效地执行可编程外设(如I2S)

控制器区域网络(CAN)

全面支持PSoC Creator设计入口、开发和调试环境,从而提供:

设计入口和构建(了解模拟路由)

用于所有的固定功能外设和通用的可编程外设的组件

文档和培训模块

支持将编译内容导入到MDK ARM环境(前面将其称为RealView)和其他环境内。

除了CapSense外,PSoC 6 MCU器件还有以下主要特性:

单CPU器件(Arm Cortex-M4),双CPU器件(Cortex-M4 and Cortex-M0+)。硬件中支持处理器间的通信

在1.71 V ~ 3.6 V的器件工作电压范围内,用户可以选择1.1 V或0.9 V的内核逻辑操作

高达2 MB的闪存存储器以及高达1 MB的SRAM

多达78个GPIO,可用于模拟、数字、CapSense或segment LCD功能

可编程模拟模块:两个运算放大器、可配置PGA、比较器、12位SAR ADC(1 Msps)、12位电压模式DAC

可编程数字模块、通信接口

12个UDB、32个TCPWM,可配置为16位/32位定时器、计数器、PWM或正交解码器

九个串行通信模块(SCB),可配置为I2C、SPI或UART接口

具有一个I2S接口和两个PDM通道的音频系统

SMIF接口,支持从外部四路SPI闪存实现的芯片内执行(XIP)以及动态加密和解密。

符合BLE 5.0规范的蓝牙智能连接(仅适用于BLE器件系列的PSoC 6 MCU)

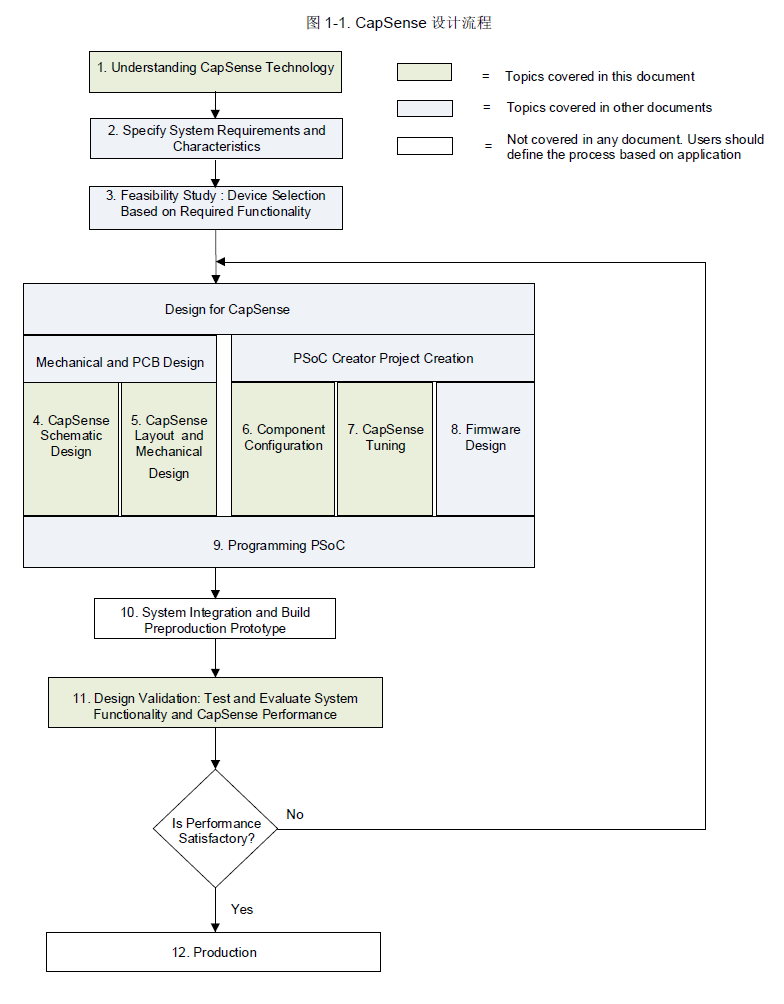

1.3 CapSense 设计流程

图1-1 显示的是典型的电容式感应产品的设计周期流程;本指南中提供的内容以绿色高亮显示。

评论