一、 PCIe总线概述

PCIe总线使用了高速差分总线,并采用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似。二、 PCIe端到端的数据传递

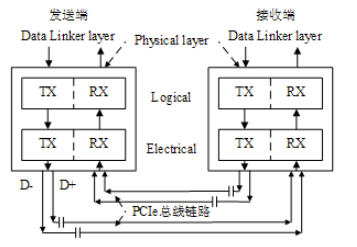

PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”,与单端信号相比,差分信号抗干扰的能力更强。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

三、 PCIe 链路介绍

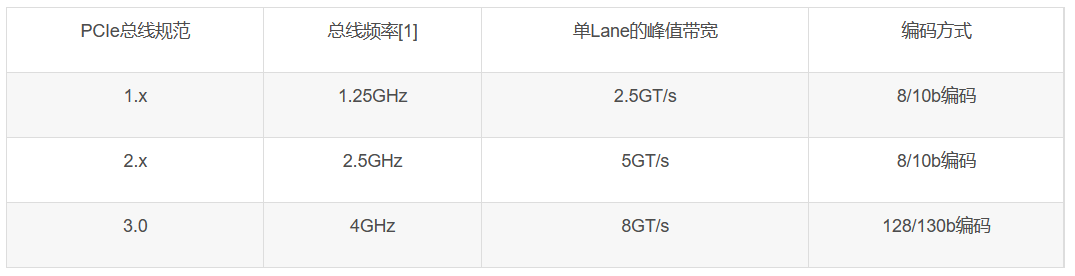

PCIe链路可以由多条Lane组成,目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即×1、×2、×4、×8、×12、×16和×32宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关,不同的PCIe总线规范所定义的总线频率和链路编码方式并不相同。PCIe总线规范与总线频率和编码的关系,如下表所示:

如上表所示,不同的PCIe总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同。PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。V3.0规范使用的总线频率虽然只有4GHz,但是其有效带宽是V2.x的两倍。

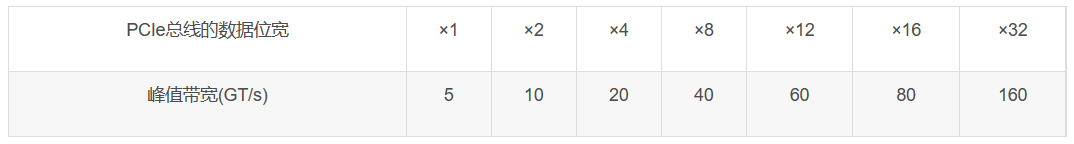

以V2.x规范为例,说明不同宽度PCIe链路所能提供的峰值带宽,如下表所示:

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰值带宽。GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率×数据位宽×2。 PCIe链路使用串行方式进行数据传送,然而在芯片内部,数据总线仍然是并行的,因此PCIe链路接口需要进行串并转换,这种串并转换将产生较大的延时。除此之外PCIe总线的数据报文需要经过事务层、数据链路层和物理层,这些数据报文在穿越这些层次时,也将带来延时。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含有时钟恢复模块CDR(Clock Data Recovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传递。使用了REFCLK+和REFCLK-信号对作为本地参考时钟。

四、 PCIe 设备电源信号

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

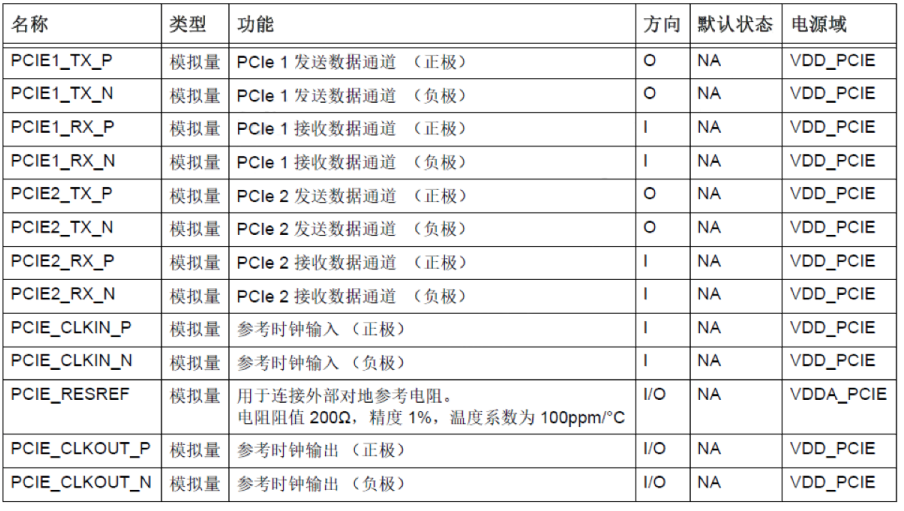

包括两个 PCIe3.0 接口,支持 Gen3(8Gbps) , 也向下兼容Gen2(5Gbps)和Gen1(2.5Gbps)。每个PCIe包括1组数据通道,支持RC模式和EP模式。

其中PCIe的发送数据通道线路需串联 0.1uF~0.22uF 电容,靠近CPU摆放;PCIe的接收数据通道线路需串联 0.1uF~0.22uF 电容,靠近终端摆放;

六、 SemiDrive X9H处理器 PCIe 电路设计

1. x9H 底板PCIe部分原理图设计

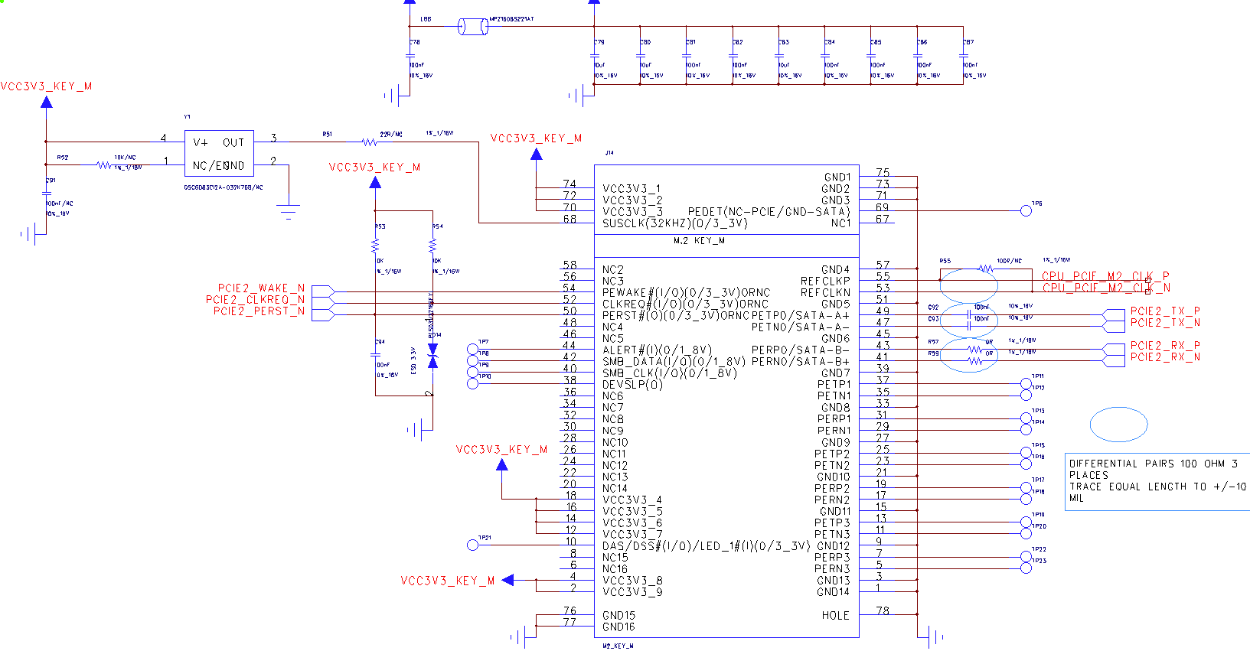

底板部分电路采 M.2 接口实现MPU 与 PCIe 设备进行 PCIe 数据通信,电路如下:

七、总结

PCIe 差分数据线按照100欧姆阻抗设计,差分线误差按照 10mil 设计,遵循标准的高速差分高速信号规则,保证信号的完整性;PCIe 信号线应原理晶振,感性设备和射频信号等,并在信号线过孔周边打不少于两个地孔。

八、参考文献

X9H处理器数据手册_Rev04.00.pdf

SD003_X9H_REF硬件设计指导.pdf

SD_X9H_REF产品用户手册.pdf