Vishay 高压4.5V to 60V input, 2A, 4A, 6A, 10A Vishay microBuck SC46x 设计与布局走线介绍!

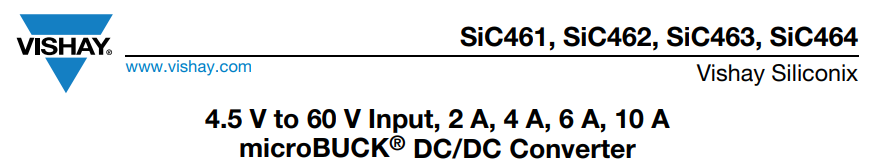

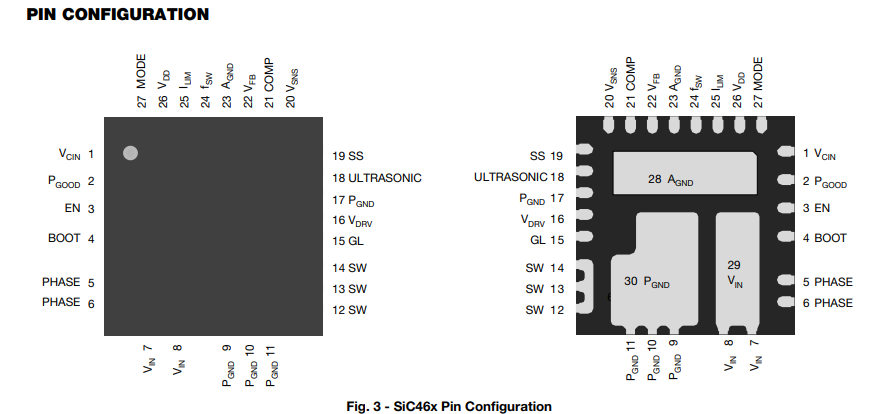

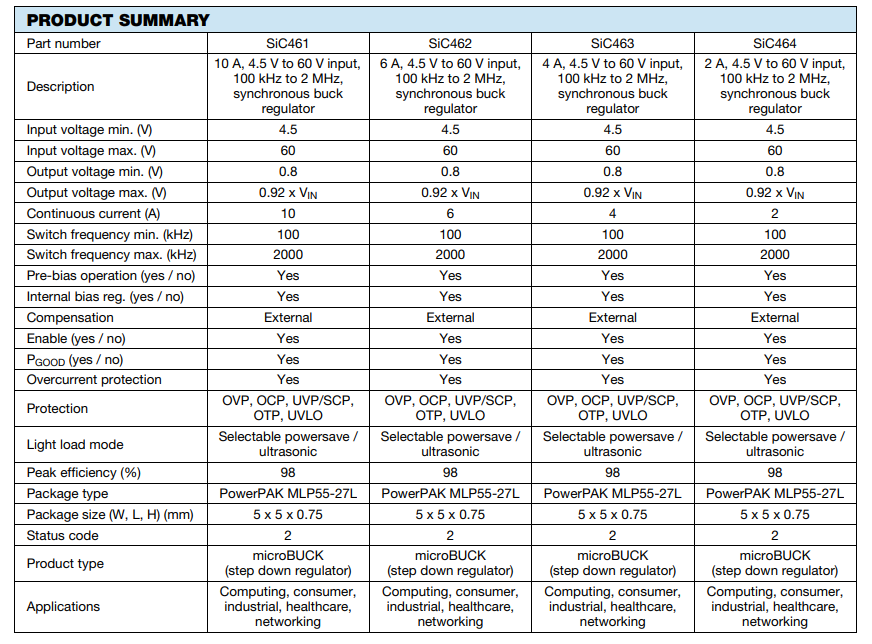

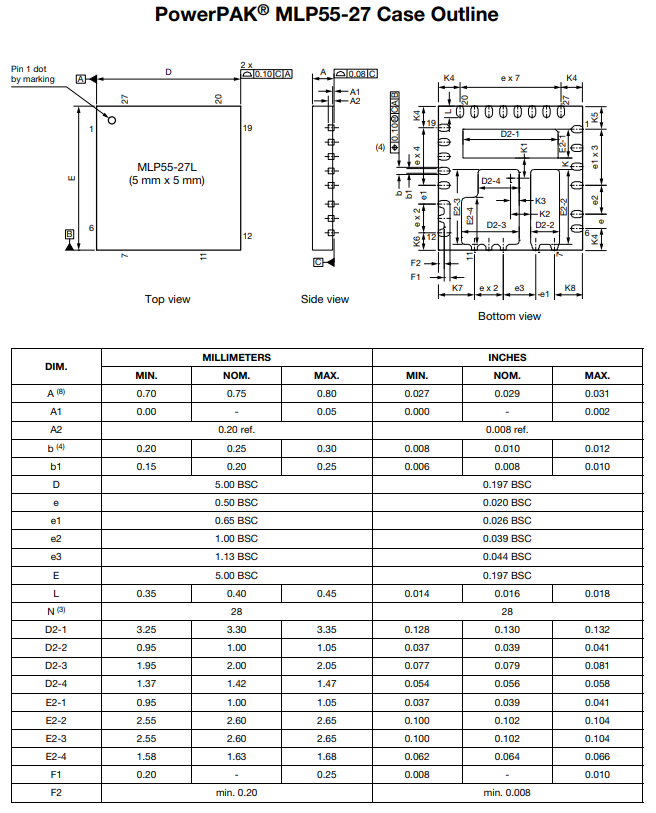

SiC46x 使用5x5 MLP55-27L包装。

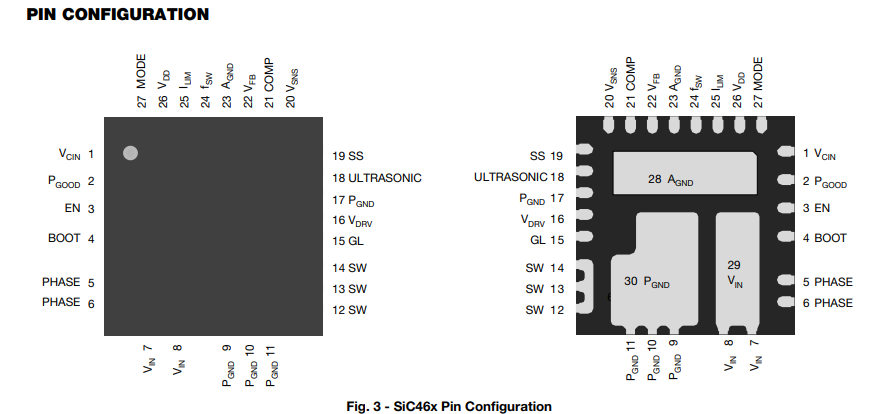

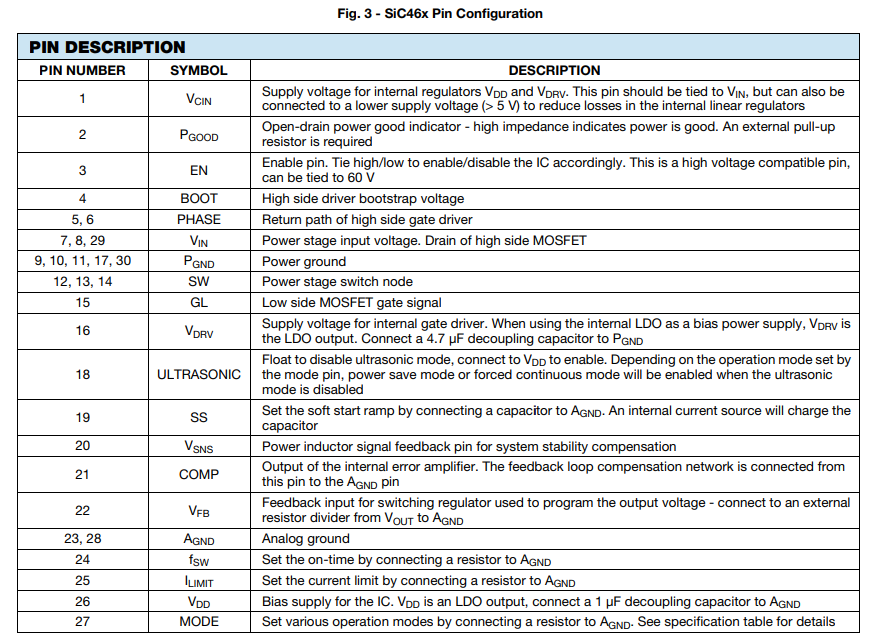

SiC46x脚位设计拥有ULTRASONIC避免Audio Noise与SS pin灵活的缓启动设置!搭配COMP与FSW让RD设计更灵活!

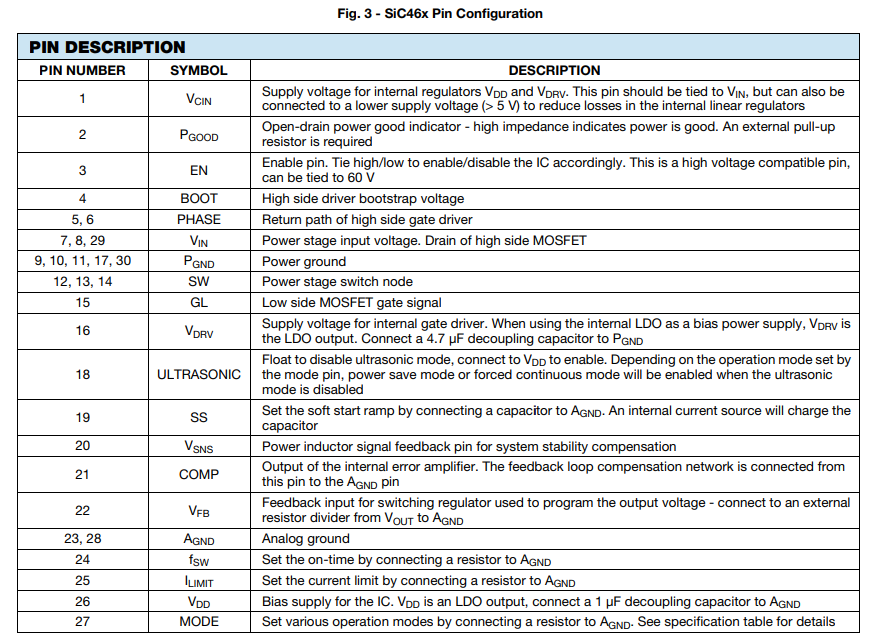

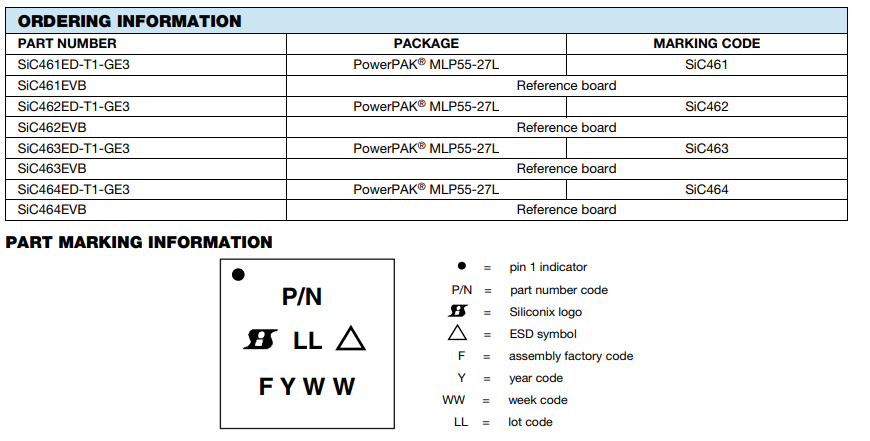

SiC46x系列产品从2A, 4A, 6A, 10A皆为Pin to Pin产品, 让RD可以自由选择使用状况, 避免Re-Desig 。

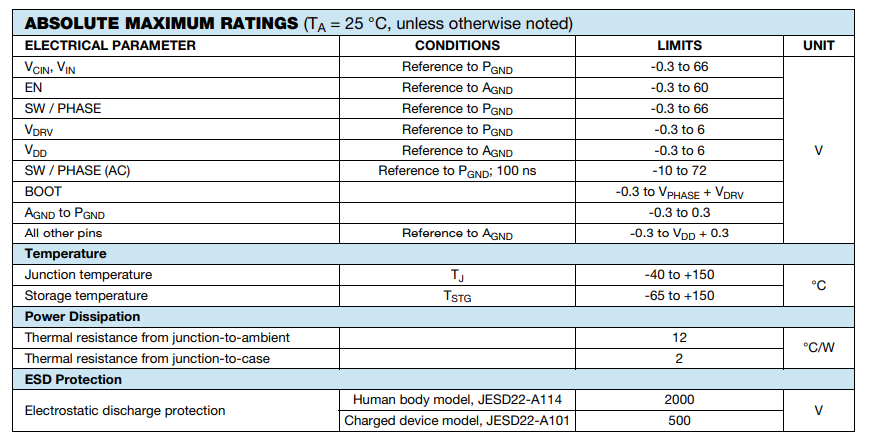

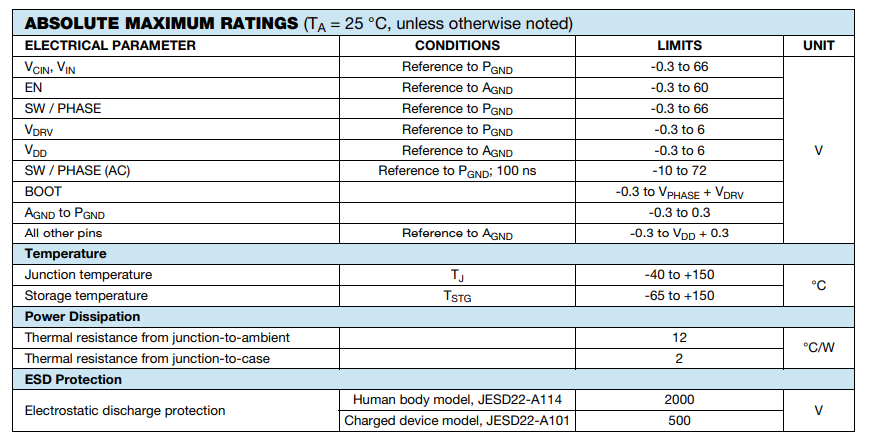

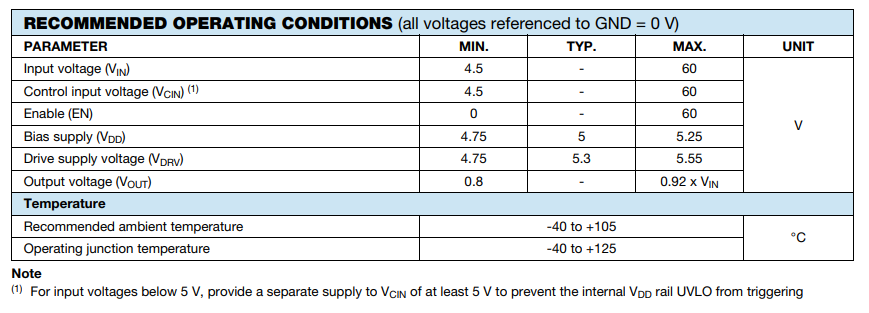

优于业界的绝对最大额定值 VIN高达66V

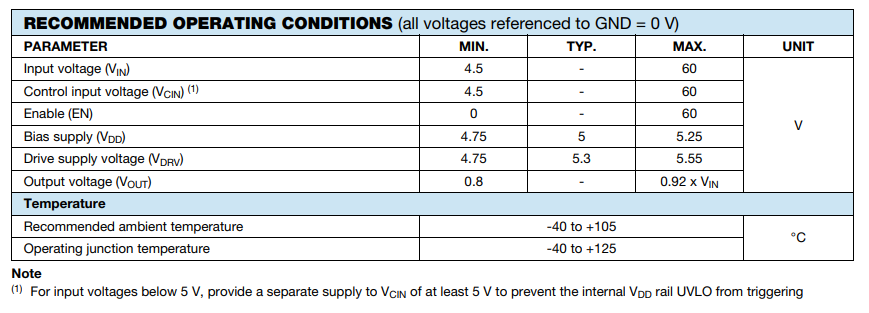

宽广的4.5V to 60V满足更多应用场景!

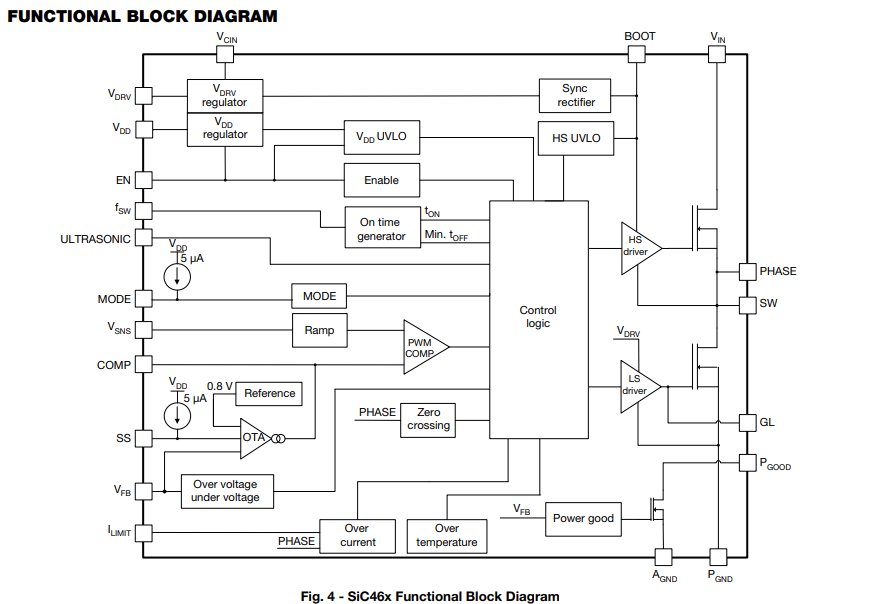

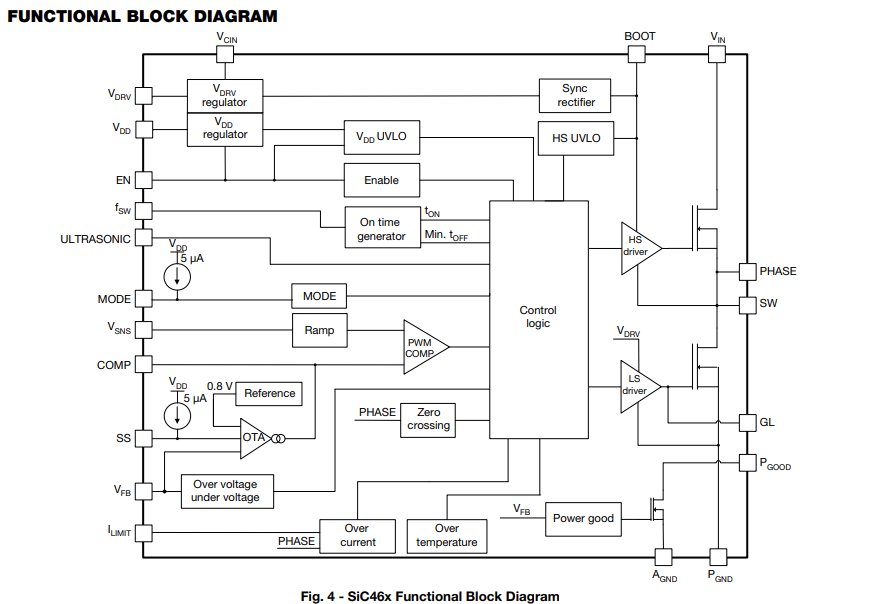

内部方块图建置UVLO & Over voltage & Over current & Over temperature完整保护客户电路!

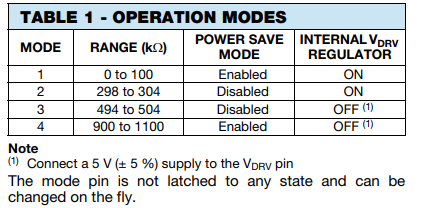

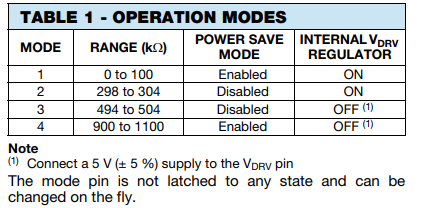

灵活的外部电阻自由设定Power SAVE MODE

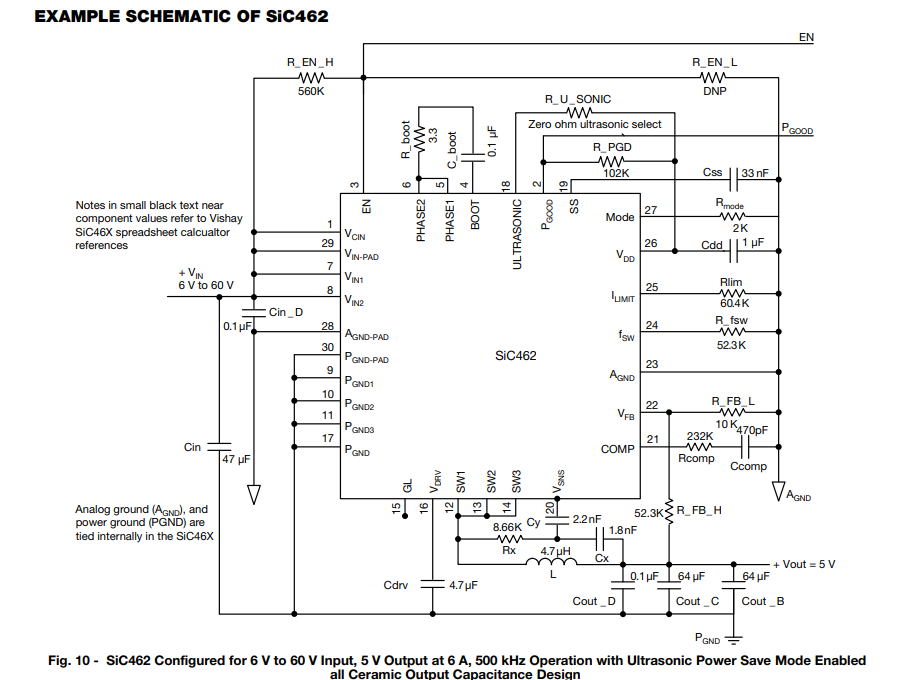

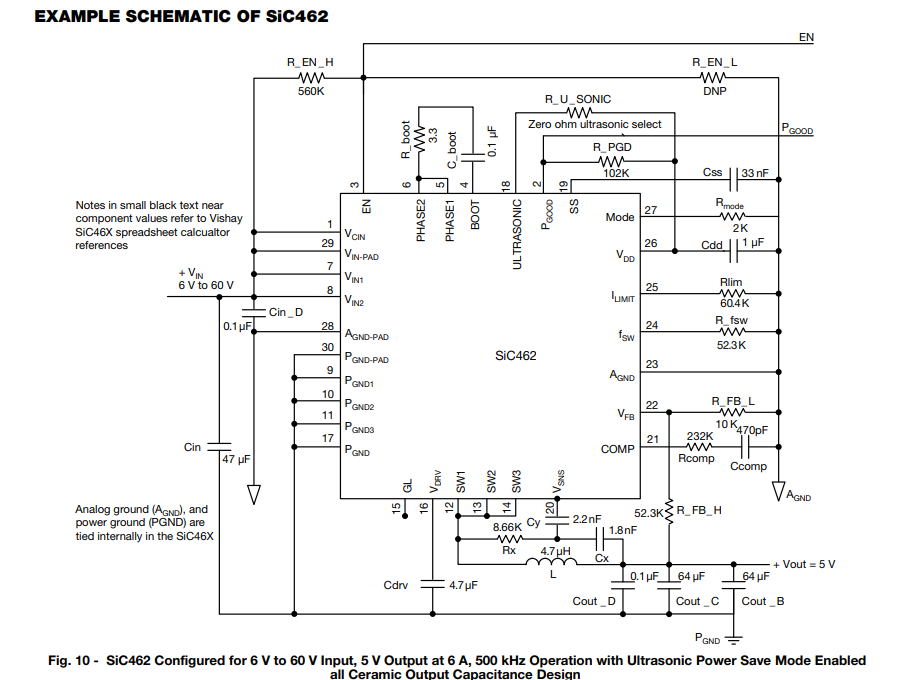

6V to 60V input to 5V Output at 6A 参考线路

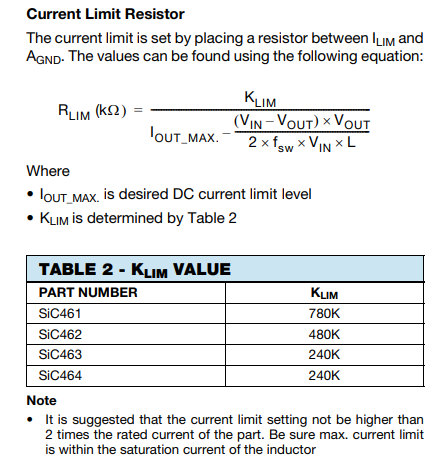

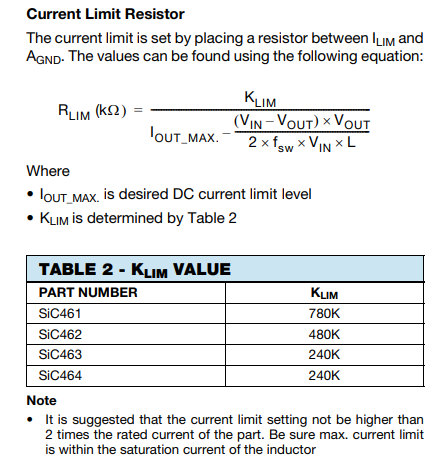

搭配RLIM设定更精准的Over current保护点!

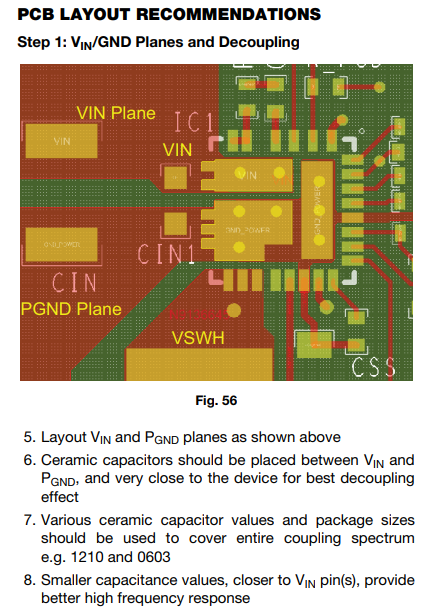

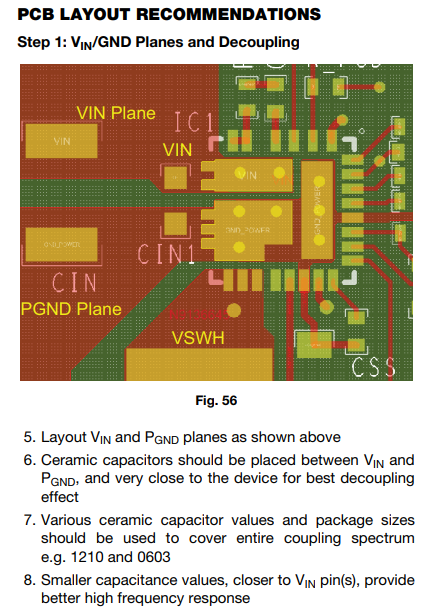

陶瓷电容建议靠近IC达到最佳去耦合影响, 使用1210或0603(C12=Cin1下到PGND), 小的容值可以提供更好的高频响应!

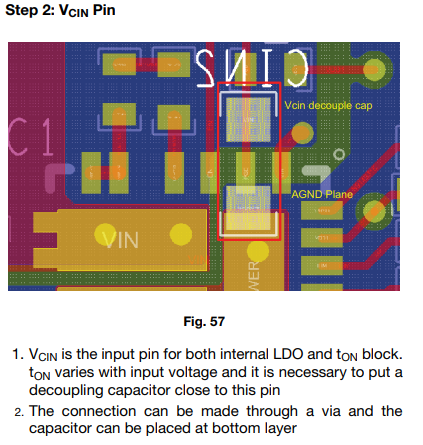

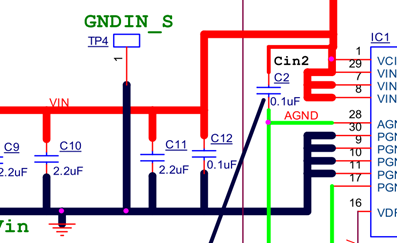

VCIN是提供内部LDO与Ton使用Cin2=C2要越近越好,可以通过Via将电容摆放到Bottom层, 但须注意VIA孔径!IC Pin一出来就透过VIA到Bottom层经过Cin2=C2直接到AGND!

SiC46x 使用5x5 MLP55-27L包装。

SiC46x脚位设计拥有ULTRASONIC避免Audio Noise与SS pin灵活的缓启动设置!搭配COMP与FSW让RD设计更灵活!

SiC46x系列产品从2A, 4A, 6A, 10A皆为Pin to Pin产品, 让RD可以自由选择使用状况, 避免Re-Desig 。

优于业界的绝对最大额定值 VIN高达66V

宽广的4.5V to 60V满足更多应用场景!

内部方块图建置UVLO & Over voltage & Over current & Over temperature完整保护客户电路!

灵活的外部电阻自由设定Power SAVE MODE

6V to 60V input to 5V Output at 6A 参考线路

搭配RLIM设定更精准的Over current保护点!

陶瓷电容建议靠近IC达到最佳去耦合影响, 使用1210或0603(C12=Cin1下到PGND), 小的容值可以提供更好的高频响应!

VCIN是提供内部LDO与Ton使用Cin2=C2要越近越好,可以通过Via将电容摆放到Bottom层, 但须注意VIA孔径!IC Pin一出来就透过VIA到Bottom层经过Cin2=C2直接到AGND!

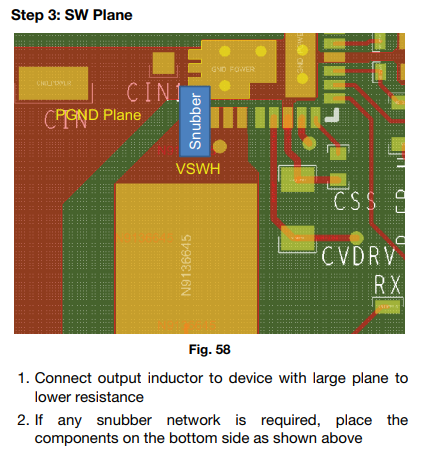

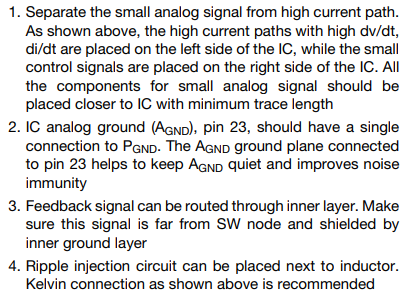

SW与电感plane可以大一些以得到更低等校电阻,可以将Snubber电路放到bottom层,但须注意中间层面须隔离避免SW感扰其他讯号!

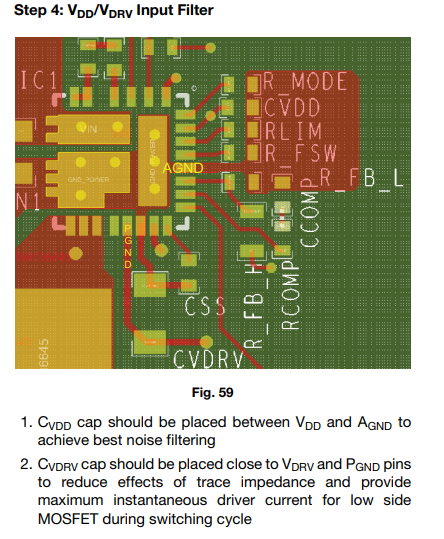

CVDD电容需摆放在VDD与AGND之间达到最佳抗躁能力,CVDRV需摆放在VDRV与PGND之间并且越近越好,减少影响trace impedance并且提供最大驱动电流for Low side MOSFET 开关使用。

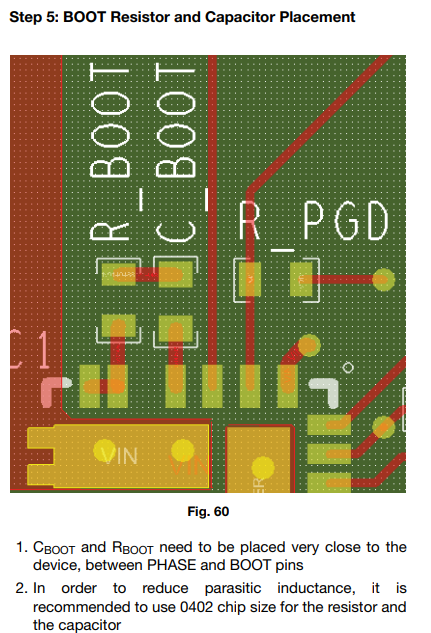

CBOOT and RBOOT离IC越近越好,为了减少寄生电感建议R&C使用0402包装!

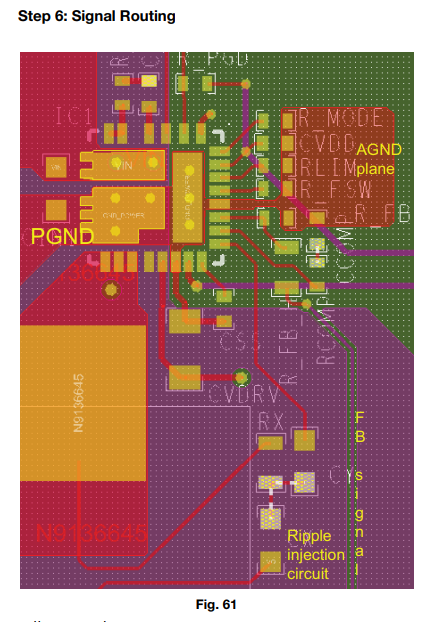

小讯号控制摆放在IC右侧并且靠近IC。

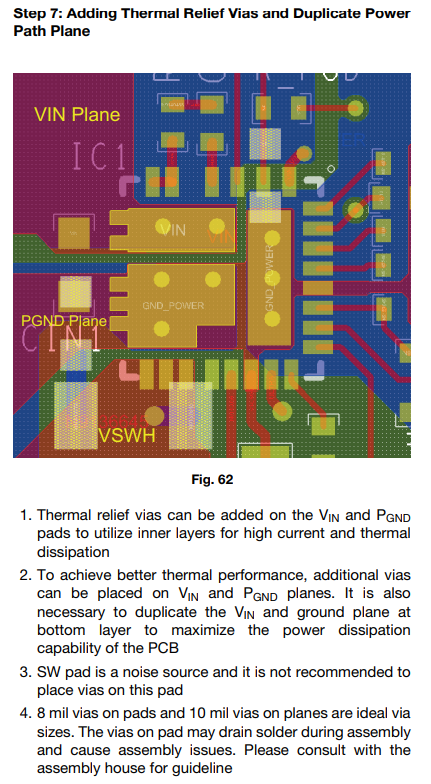

散热孔与散热走线建议参考原厂设计!

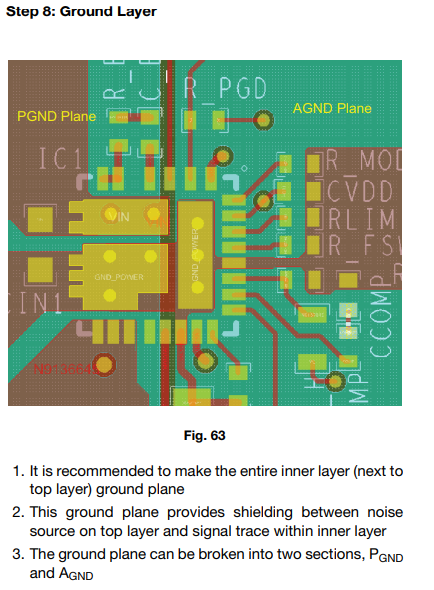

建议整个内层的ground plane左边PGND右边ANGD,透过VIA再到Top Layer。

SiC46x 系列产品完整的保护机制有2A & 4A & 6A & 10A版本。

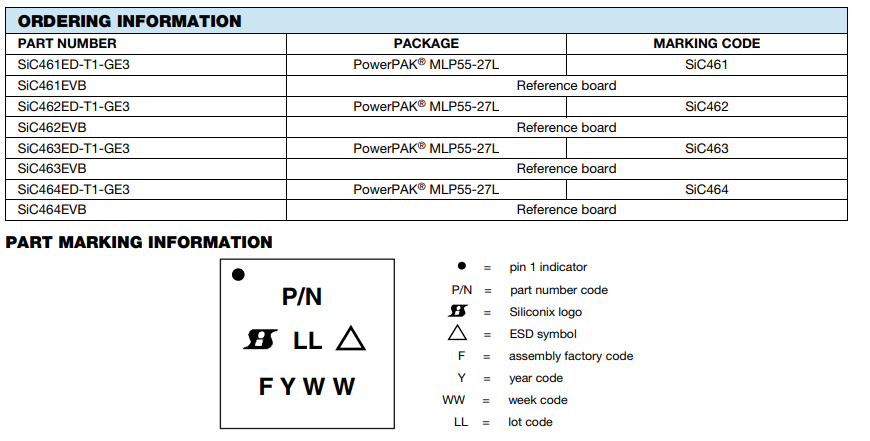

基本IC 包装资讯!

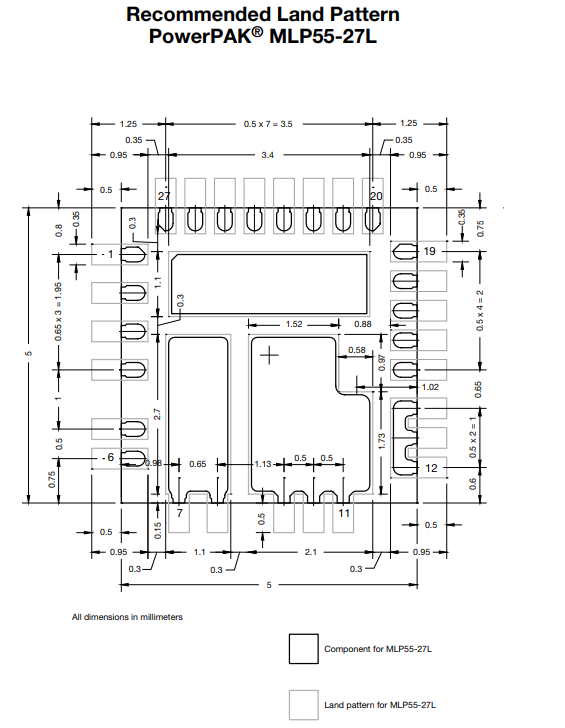

PCB Land Pattern尺寸

以上先关资料来源来自于Vishay 台湾威世有限公司

评论