1 LPC55S69 是什么?

LPC55S69 是 NXP Cortex-M33 双核架构的 MCU ,此次讨论是有关双核要如何启动和使用的流程,还有若是要启用两个 程序的关联设定,需要注意的事项。

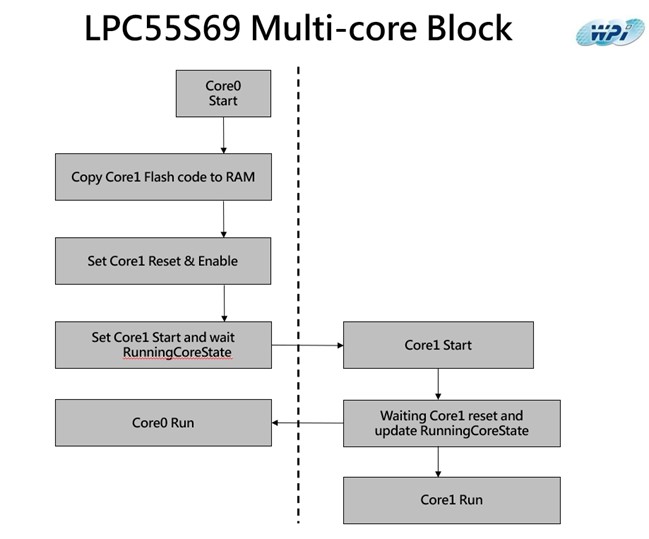

1.1 双核方块图

双核启用方块图,如图1.1.1

2 双核模式使用说明

- 如何从无到有

不管是使用 MCUxpresso 或是 Keil ,都是需要开两个 project 分别是使用 Core0 和 Core1

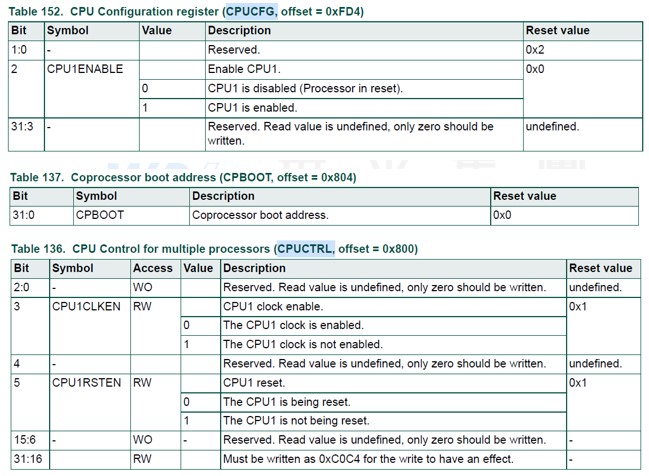

并且 先将 Core1 的 code 从 Flash 放在 要起始 RAM 上,在 Core0 将 CPUCFG 设成 Core1 要使用,并且将 Core1 的起始位址放在 RAM 上,最后再将 CPUCTRL 的 Core1 的 Clock 启动之后 Reset Core1,如‘图2.1’( 注1 )

SYSCON->CPUCFG |= SYSCON_CPUCFG_CPU1ENABLE_MASK;

/* Boot source for Core 1 from RAM */

SYSCON->CPBOOT = SYSCON_CPBOOT_CPBOOT((uint32_t)(char *)bootAddress);

详细可以参考 mcmgr_start_core_internal() 这个 function code,其中的方式,也是直接控制这些 register 来打开 Core1,所以要做到上面的步骤 Core0 需要知道 Core1 放置的 Flash 的起始位置,或者是要使用 link来做。

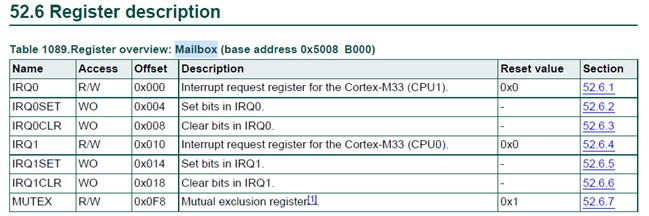

若是需要两边的程式有需要传输 ( 例如取值 ),就需要启动 Mailbox 和 share memory。

主要是使用 Mailbox 的中断 ( MBOXIRQ ),来传送和接收 share memory 的 address ,再透过此位址,来取得要沟通的资料,可使用 MAILBOX_GetValue() ,MAILBOX_SetValue() 或 用Mailbox 的 IRQ0 register来设定 Core0要给 Core1 的中断并放入一个 32 bits 资料过去,而 IRQ1 register 是反相的,用来设定 Core1要给 Core0 的中断,如‘图2.2’( 注1 )。

- 直接使用关连

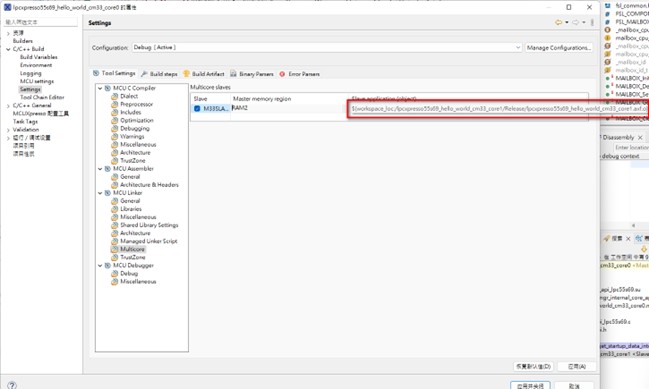

RAM size 的修改就会是在 MCU settings 内去修改了。

3 参考资料

注1 : 作者: NXP;出处 : https://www.mouser.com/pdfDocs/NXP_LPC55S6x_UM.pdf

评论