1. S32K344 FlexIO 介绍

1.1 简介

S32K344 包含一个 FlexIO 模块,FlexIO 是一种高度可配置的模块,可提供广泛的功能,包括:

- 模拟各种串行或并行通信协议,比如 UART、I2C、SPI、SAI,它既可以作为主机,也可以作为从机;

- 灵活的 16 位定时器,支持各种触发、复位、启用和禁用条件;

- 可编程逻辑块,它允许在片上实现数字逻辑功能和可配置的内部与外模模块交互;

- 可编程状态机,用于从 CPU 卸载基本系统控制功能。

表1.1.1 数据速率限制

|

FlexIO 操作 |

数据速率限制 |

|

Master Tx |

FlexIO_clk/4 |

|

Slave Tx |

FlexIO_clk/10 |

|

Master Rx |

FlexIO_clk/8 |

|

Slave Rx |

FlexIO_clk/6 |

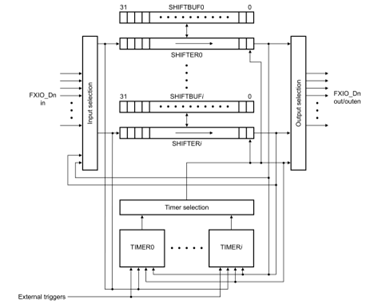

FlexIO 使用移位器、计时器和外部触发器将数据移入或移出 FlexIO。如下图所示,计时器控制数据移位的时间。可以将计时器配置为使用通用计时器功能、外部触发器或其他各种条件来确定控件。

图1.1-1 FlexIO 框图

FlexIO 包括一下特点:

- 具有发送、接收、数据匹配、逻辑和状态模式的 32 位移位寄存器数组;

- 双缓冲移位操作连续数据传输;

- 移位器串联以支持大规模传输;

- 自动生成启动与停止位;

- 支持 1、2、4、8、16 或 32 多位移位宽度并行接口;

- 中断、DMA、轮询发送和接收操作;

- 可编程波特率独立于总线时钟频率;

- 高度灵活的 16 位定时器,支持各种内部或外部触发、复位、使能和禁用条件;

- 可编程逻辑模式集成于外部数据逻辑功能片上,或结合引脚、移位器、定时器功能以产生复杂的输出;

- 可编程状态机从 CPU 卸载基本系统控制功能,支持多达八个状态、八个输出,何三个可选择输入的每个状态;

- 集成通用输入/输出寄存器和引脚上升或下降沿中断,以简化软件支持;

- 支持广泛的协议,包括但不限于:UART、I2C、SPI、I2S、Camera IF、Motorola 68K 或 or Intel 8080 bus、PWM 或 waveform 生成、输入捕获(脉冲边缘间隔测量)例如 SENT。

2. 功能描述

2.1 移位器操作

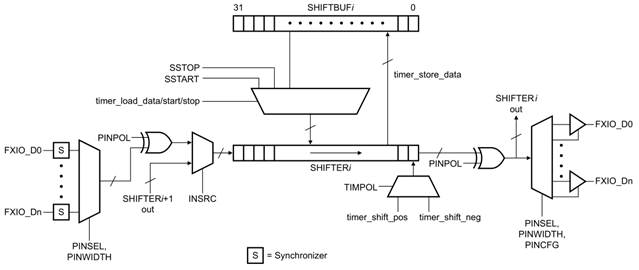

移位器负责缓冲和将数据移入或移出 FlexIO。移位、加载和存储事件的时间通过 SHIFTCTL[TIMSEL] 寄存器分配给移位器的定时器控制。移位器被设计成支持 DMA、中断或轮询操作。下图为移位器微架构的详细视图。

图2.1-1 移位器微体系架构图

移位器有发送、接收、匹配存储、连续匹配、状态、逻辑等模式,具体模式信息与寄存器读写操作本文不在此赘述详细了解请阅读 S32K344 用户参考手册。

2.2 定时器操作

FlexIO 16 位定时器控制移位寄存器的加载、移位和存储。计数器加载比较寄存器的内容,并在 FlexIO 时钟上递减到零。计数器可以执行一般定时器功能,如产生时钟或选择输出或 PWM 波形。定时器可以被配置为:

- 使能响应触发器、引脚或移位器条件;

- 始终或仅在触发器或者引脚边沿递减;

- 响应触发器或引脚条件复位;

- 在触发器、引脚条件或定时器比较上禁用。

定时器可以选择性地包括开始条件和停止条件。

虽然每个定时器都可以独立运行,但可以将一个定时器配置为与前一个定时器同时启用或禁用(例如:定时器 1 可以与定时器 0 同时启用或禁用),并且定时器输出可用于触发任何定时器。每个定时器使用的触发器是独立配置的,可以配置为定时器输出、移位器状态标识、引脚输入或外部触发输入。触发器配置与引脚配置分开,引脚配置可以配置为输入、输出数据或输出使能。定时器配置寄存器(TIMCFGn)必须在设置定时器模式(TIMOD)之前进行配置。

定时器有 8 位波特计数器模式、8 位高 PWM 模式、16 位计数器模式、禁用 16 位计数器模式、8 位字计数器模式、8 位低 PWM 模式、计数器使能和开始位、定时器衰减和复位、定时器禁用和停止位等模式,具体模式信息与寄存器读写操作本文不在此赘述详细了解请阅读 S32K344 用户参考手册。

2.3 引脚操作

每个定时器和移位器的引脚配置可以配置为使用任何一个极性的任何 FlexIO 引脚。每个定时器和移位器可以配置为输入、输出数据、输出使能或双向输出。配置为输出启用的引脚可以用作漏极(极性倒置,因为输出启用置位导致引脚上输出逻辑零)或控制双向输出上的启用。任何定时器或移位器都可以配置为控制引脚的输出使能,其中双向输出数据有另一个定时器或移位器驱动。

引脚操作有并行接口、引脚同步、引脚覆盖、引脚中断等模式,,具体模式信息与寄存器读写操作本文不在此赘述详细了解请阅读 S32K344 用户参考手册。

2.4 低功耗模式

如果使能了 FlexIO 功能时钟,则在低功耗模式下,FlexIO 仍能正常工作。

2.5 调试模式

如果设置了使能调试字段(CTRL[DBGE]),则 FlexIO 在调试模式下保持功能。

2.6 时钟

功能时钟

FlexIO 功能时钟与总线时钟是异步的,可以在低功耗模式下使能。在访问任何 FlexIO 寄存器之前,必须启动 FlexIO 功能时钟。如果 FlexIO 功能时钟至少等于总线时钟,则可以设置 CTRL[FASTACC] 字段以支持快速寄存器访问。

总线时钟

总线时钟仅用于总线访问控制寄存器和配置寄存器。

2.7 复位

芯片复位

在芯片复位时,FlexIO 的逻辑和寄存器被重置为其默认状态。

软件复位

FlexIO 在其控制寄存器中实现了一个软件复位字段。CTRL[SWRST] 将除了 CTRL 外的所有逻辑和寄存器重置为默认状态。

2.8 中断与 DMA 请求

表2.8.1 FlexIO 中断与 DMA 请求

|

标志 |

描述 |

中断 |

DMA 请求 |

低功耗唤醒 |

|

SSF |

移位器状态标志 |

Y |

Y |

Y |

|

SEF |

移位器错误标志 |

Y |

N |

Y |

|

TSF |

计时器状态标志 |

Y |

Y |

Y |

|

PSF |

引脚状态标志 |

Y |

N |

Y |

|

ETSF |

外部触发状态标志 |

Y |

N |

Y |

2.9 外围触发器

FlexIO 外围触发器与其他外设之间的连接是特定于设备的。

输出触发器

每个 FlexIO 定时器产生一个等于定时器输出的输出触发器。输出触发器不受定时器引脚极性配置的影响。

输入触发器

FlexIO 支持多个外部触发输入,可用于触发一个或多个 FlexIO 定时器。当使能 FlexIO 时,如果在外部触发器上检测到上升沿,则设置外部触发状态标志。外部触发器与 FlexIO 功能时钟同步,并且必须置位至少两个周期的 FlexIO 功能时钟才能正确采样。

3. FlexIO 模拟应用

3.1 UART

3.1.1 发送

可以使用一个定时器、一个移位器和一个引脚(如果支持 CTS,则为两个引脚)来支持 UART 传输。开始和停止位插入是自动处理的,并且使用 DMA 控制器支持多次传输。定时器状态标志用于指示何时传输每个字的停止位。

中断和空闲字符需要软件干预。在发送中断或空闲字符之前,必须更改 SSTART 和 SSTOP 字段以传输所需的状态,并且要传输的数据必须等于 FFh 或 00h。支持第二个停止位需要使用软件将停止位插入数据流(并增加要传输的位数)。当对 SHIFTBUFn 执行字节写入时(或者先传输 MSB 的 SHIFTBUBIS),寄存器的其余部分保持不变。这允许地址标记位或额外的停止位保持不受干扰。

3.1.2 接收

可以使用一个定时器、一个移位器和一个引脚(如果支持 RTS,则使用两个定时器和两个引脚)来支持 UART 接收。开始和停止位验证时自动处理的,并且使用 DMA 控制器支持多次传输。定时器状态标志用于指示何时接收到每个单词的停止位。

FlexIO 不支持对接收到的数据进行三重投票;数据只在每个比特的中间采样一次。可以使用定时器来实现传入数据上的故障滤波器,并使用不同的定时器来检测可编程长度的空闲路线。中断字符导致错误标志被设置,移位器缓冲区寄存器将返回 00h。

3.2 SPI

3.2.1 控制器

可以使用两个定时器、两个移位器和四个引脚支持 SPI 控制器模式。支持 CPHA=0 或 CPHA=1,并且可以使用 DMA 控制器支持传输。对于 CPHA=1,可以对多个传输保持置位选择,并且可以使用定时器状态标识来指示传输的结果。

停止位用于保证在目标选择否定和下一次传输之前至少有一个时钟周期。要启动每次传输,需要通过核心或 DMA 向传输缓冲区写入数据。

3.2.2 目标

SPI 目标模式可以使用一个定时器、两个移位器和四个引脚。支持 CPHA=0 或 CPHA=1,并且可以使用 DMA 控制器进行传输。对于 CPHA=1,可以对多个传输保持置位选择,并且可以使用定时器状态标志来指示传输的结束。

在外部目标选择置位之前,必须将传输数据写入传输缓冲区寄存器,否则将设置移位错误标志。

3.3 I2C

3.3.1 控制器

可以使用两个定时器、两个移位器和两个引脚来实现 I2C 控制器模式。一个定时器用于 SCL 输出,一个定时器用于控制移位器;两个移位器用于发送和接收字符,接收时发送机必须发送 FFh 到 3 状态输出。FlexIO 在每个字后插入一个停止位,以生成和验证 ACK 或 NACK。在启用 SCL 生成之前,FlexIO 等待第一次写入传输数据缓冲区。数据传输可以使用 DMA 控制器和在发送欠运行或接收溢出上设置移位错误标志来支持。

第一个定时器为整个包生成时钟(从 START 到Repeat START 或 STOP),因此比较寄存器必须用包中的时钟边总数(减去 1)进行编程。当引脚等于输出时,定时器支持使用复位定时器进行时钟拉伸。但是这将使始终高周期和时钟低周期各增加至少 1 个 FlexIO 时钟周期。第二个定时器使用 SCL 输入引脚来控制发送和接收移位寄存器。这使 SDA 数据保持时间增加了 2 个 FlexIO 时钟周期。

发送和接收移位器都必须为传输中的每个字进行检修。接收时,发送移位器必须发送 FFh,接收移位器返回 SDA 引脚上的数据。传输移位器在 SCL 引脚的最后下降沿上加载一个额外的字。如果生成 STOP 条件或重复 START 条件,则该字必须分别为 00h 或 FFh。在控制器-接收器传输的最后一个字期间,必须设置发送 SSTOP 位以生成 NACK。

如果检测到 NACK,接收移位寄存器置位一个错误中断,但是负责生成 STOP 或重复 START 条件。如果在控制器发送过程中检测到 NACK,中断必须立即将 00h(如果产生 STOP)或 FFh (如果产生重复 START)写入发送移位寄存器。在禁用两个定时器之前,必须等待 SCL 上的下一个上升边沿。在等待设置延迟重复启动或停止条件后,要禁用传输移位器。

为了保证 SDA 保持时间,I2C 控制器数据有效延迟两个周期,因为时钟输出在发送或接收移位器之前通过同步器。由于 SCL 输出与 FlexIO 时钟同步,因此同步延迟为一个周期,然后一个周期生成输出。

3.4 I2S

3.4.1 控制器

可以使用两个定时器,两个移位器和四个引脚支持实现 I2S 控制器模式。一个定时器用于生成位时钟和控制移位器,一个定时器用于生成帧同步。在启用位时钟和帧同步生成之前,FlexIO 等待第一次写入传输数据缓冲区。数据传输支持使用 DMA 控制器和移位器错误标志设置在发送欠运行或接收溢出。

位时钟频率是 FlexIO 时钟频率的偶数除法。初始帧同步置位与第一个位时钟边缘同时发生。计时器使用起始位确保在第一个输出数据之前一个时钟周期生成帧同步。

3.4.2 目标

可以使用三个定时器,两个移位器和四个引脚。对于单发送和单接收,可以使用其他的发送和接收组合。

传输数据必须在外部帧同步置位之前写入传输缓冲区寄存器,否则将设置移位错误标志。

I2S 目标的输出有效时间最大为 2.5 个周期,因为时钟同步的最大延迟为 1.5 个周期,再加上 1 个周期输出数据。

定时器 2 检测帧同步的下降沿(新帧的开始)并置位输出直到位时钟的上升沿(当帧同步正常采样时)。定时器 0 检测位时钟的上升沿,定时器 2 输出置位,并置位帧长度输出。定时器 1 检测位时钟下降沿定时器 0 输出置位和控制移位寄存器位 32 位传输。

3.5 发送接收器

使用一个定时器和一个引脚可以支持发送接收器。定时器配置为输入捕获模式,捕获引脚输入下降沿的计数器值。捕获计数器值后,将自动从计数器值 0 重新启动计数器。因此,捕获值总是表示前一个下降沿和当前下降沿之间的周期。CPU 中断或 DMA 触发器可以在每次捕获计数器时配置。整个发送帧解码与最新的刻度宽度调整是由 CPU 软件执行。

3.6 低功耗状态机

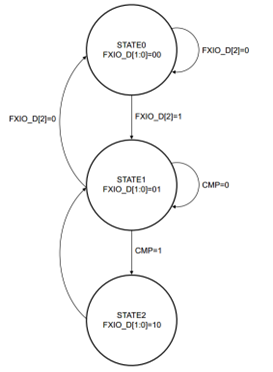

下表显示了假设状态机的示例,以说明移位器状态模式中允许的灵活性。

在这个示例里,FlexIO 等待 FXIO_D[2] 引脚置位,然后在比较器输出置位时在 FXIO_D[1:0] 引脚上以 FLEXIO_CLK/131072 的频率驱动互补方波输出,假设改比较器连接到外部触发器 15。有关实际 FlexIO 触发器映射,请参阅芯片特定的 FlexIO 信息。下图显示了此示例现实的状态和转换。

图3.6-1 状态图

3.7 键盘接口

键盘接口可以使用三个定时器和三个移位器支持 3×4 键盘矩阵,不过可以使用附加移位器支持更大的矩阵。该配置设计为四列配置为低电平有效开漏引脚,三行配置为启用上拉电阻的输入引脚。

一个移位器被配置为逻辑模式,以在任何行为输入为低电平(表明按下了某个键)时置位其输出。使用计时器来过滤移位器输出,以确保在执行列扫描之前按下按键的时间最短。

配置不同的移位器用于并行传输。当检测到按键时,使用此移位器扫描每一列。不扫描时,移位器输出配置为置位所有低电平有效开漏列输出以检测任何按键。使用专用定时器来控制发送移位器。

最后一个移位器配置为并行接收。使用此移位器捕获列扫描的结果,以便软件解码按下的键(或多个键)。尽管行状态也可以通过移位顺序推断,但此配置捕获每次扫描的行和列引脚的状态。使用专用定时器来控制接收移位器,其移位评率为发送移位器频率的一半。

当接收移位寄存器中存在按键扫描的结果时,FlexIO 继续监视行输入,并可以通过一次按键触发多次扫描。为了支持去抖动,可以将多少次连续臊面视为单词按键。

4. 外部信号

表4-1 外部信号

|

信号 |

描述 |

方向 |

|

FXIO_Dn(n=0…31) |

双向 FlexIO 移位器和定时器引脚 |

输入或输出 |

5. FlexIO 寄存器描述

FlexIO 基础地址:4032_4000h

|

偏移 |

寄存器 |

宽度 (以位为单位) |

存取 |

复位值 |

|

0h |

Version ID Register (VERID) |

32 |

RO |

0201_0003h |

|

4h |

Parameter Register (PARAM) |

32 |

RO |

0420_0808h |

|

8h |

FlexIO Control Register (CTRL) |

32 |

RW |

0000_0000h |

|

Ch |

Pin State Register (PIN) |

32 |

RO |

0000_0000h |

|

10h |

Shifter Status Register (SHIFTSTAT) |

32 |

W1C |

0000_0000h |

|

14h |

Shifter Error Register (SHIFTERR) |

32 |

W1C |

0000_0000h |

|

18h |

Timer Status Register (TIMSTAT) |

32 |

W1C |

0000_0000h |

|

20h |

Shifter Status Interrupt Enable (SHIFTSIEN) |

32 |

RW |

0000_0000h |

|

24h |

Shifter Error Interrupt Enables (SHIFTEIEN) |

32 |

RW |

0000_0000h |

|

28h |

Timer Interrupt Enable Register (TIMIEN) |

32 |

RW |

0000_0000h |

|

30h |

Shifter Status DMA Enable (SHIFTSDEN) |

23 |

RW |

0000_0000h |

|

38h |

Timer Status DMA Enable (TIMERSDEN) |

32 |

RW |

0000_0000h |

|

40h |

Shifter State Register (SHIFTSTATE) |

32 |

RW |

0000_0000h |

|

48h |

Trigger Status Register (TRGSTAT) |

32 |

W1C |

0000_0000h |

|

4Ch |

External Trigger Interrupt Enable Register (TRIGIEN) |

32 |

RW |

0000_0000h |

|

50h |

Pin Status Register (PINSTAT) |

32 |

W1C |

0000_0000h |

|

54h |

Pin Interrupt Enable Register (PINREN) |

32 |

RW |

0000_0000h |

|

58h |

Pin Rising Edge Enable Register (PINREN) |

32 |

RW |

0000_0000h |

|

5Ch |

Pin Falling Edge Enable Register (PINFEN) |

32 |

RW |

0000_0000h |

|

60h |

Pin Output Data Register (PINOUTD) |

32 |

RW |

0000_0000h |

|

64h |

Pin Output Enable Register (PINOUTE) |

32 |

RW |

0000_0000h |

|

68h |

Pin Output Disable Register (PINOUTDIS) |

32 |

WORZ |

0000_0000h |

|

6Ch |

Pin Output Clear Register (PINOUTCLR) |

32 |

WORZ |

0000_0000h |

|

70h |

Pin Output Set Register (PINOUTSET) |

32 |

WORZ |

0000_0000h |

|

74h |

Pin Output Toggle Register (PINOUTTOG) |

32 |

WORZ |

0000_0000h |

|

80h-9Ch |

Shifter Control N Register (SHIFTCTL0-SHIFTCTL7) |

32 |

RW |

0000_0000h |

|

100h-11Ch |

Shifter configuration N Register (SHIFTCFG0-SHIFTCFG7) |

32 |

RW |

0000_0000h |

|

200h-21Ch |

Shifter Buffer N Register (SHIFTBUF0-SHIFTBUF7) |

32 |

RW |

0000_0000h |

|

280h-29Ch |

Shifter Buffer N Bit Swapped Register (SHIFTBUFBIS0-SHIFTBUFBYS7) |

32 |

RW |

0000_0000h |

|

300h-31Ch |

Shifter Buffer N Byte Swapped Register (SHIFTBUFBYS0-SHIFTBUFBBS7) |

32 |

RW |

0000_0000h |

|

380h-39Ch |

Shifter Buffer N Bit Byte Swapped Register (SHIFTBUFBBS0-SHIFTBUFBBS7) |

32 |

RW |

0000_0000h |

|

400h-41Ch |

Timer Control N Register (TIMCTL0-TIMCTL7) |

32 |

RW |

0000_0000h |

|

480h-49Ch |

Timer Configuration N Register (TIMCFG0-TIMCFG7) |

32 |

RW |

0000_0000h |

|

500h-51Ch |

Timer Compare N Register (TIMCMP0-TIMCMP7) |

32 |

RW |

0000_0000h |

|

680h-69Ch |

Shifter Buffer N Nibble Byte Swapped Register (SHIFTBUFNBS0-SHIFTBUFNBS7) |

32 |

RW |

0000_0000h |

|

700h-71Ch |

Shifter Buffer N Halfword Swapped Register (SHIFTBUFHWS0-SHIFTBUFHWS7) |

32 |

RW |

0000_0000h |

|

780h-79Ch |

Shifter Buffer N Nibble Swapped Register (SHIFTBUFNIS0-SHIFTBUFNIS7) |

32 |

RW |

0000_0000h |

|

800h-81Ch |

Shifter Buffer N Odd Even Swapped Register (SHIFTBUFOES0-SHIFTBUFOES7) |

32 |

RW |

0000_0000h |

|

880h-89Ch |

Shifter Buffer N Even Odd Swapped Register (SHIFTBUFEOS0-SHIFTBUFEOS7) |

32 |

RW |

0000_0000h |

|

900h-91Ch |

Shifter Buffer N Halfword Byte Swapped Register (SHIFTBUFHBS0-SHIFTBUFHBS7) |

32 |

RW |

0000_0000h |

由于篇幅所限本文仅介绍 S32K344 FlexIO 模块部分内容,如想了解更多资料与设计,请联系我们 atu.sh@wpi-group.com。

6. 参考文献

[1] S32K3XX Reference Manual.pdf,NXP

[2] S32K3XX Data Sheet.pdf,NXP

欢迎在博文下方留言评论,我们会及时回复您的问题。如有更多需求,欢迎联系大联大世平集团 ATU 部门:atu.sh@wpi-group.com

作者:Hobo Xu/ 许宁

评论