|

开发板 |

代码包 |

示例 SPI |

拨码 |

|

SD103_E3_GATEWAY_EPOWERTRAIN_A03_041 |

MCAL3.0+PATCH 4676506 |

SPI7 |

1110 |

表 (1)

二、测试过程

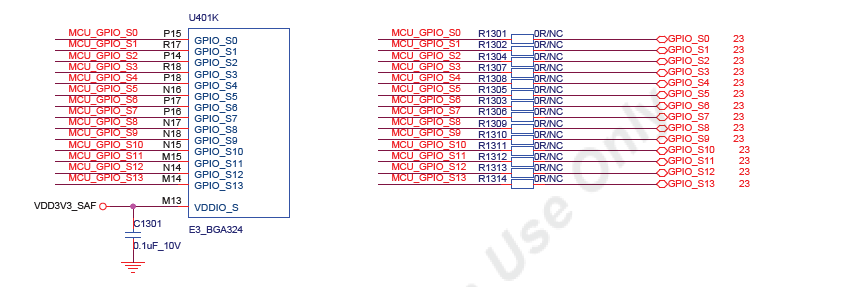

1、原理图

图 (1)

图 (2)

开发板上贴 R1311、R1312、R1313、R1314;SPI7 的四个引脚引到 J2305.

2、Datasheet

|

Pin Name |

MUX |

Moudule |

Function |

Default |

|

GPIO_S10 |

MUX3 |

SPI7 |

SS0 |

|

|

GPIO_S11 |

MUX3 |

SPI7 |

SCLK |

|

|

GPIO_S12 |

MUX3 |

SPI7 |

MISO |

|

|

GPIO_S13 |

MUX3 |

SPI7 |

MOSI |

|

表 (2)来源:表 Pin Multiplexing of Digital GPIO Pins in Safety Domain

3、配置 MCAL

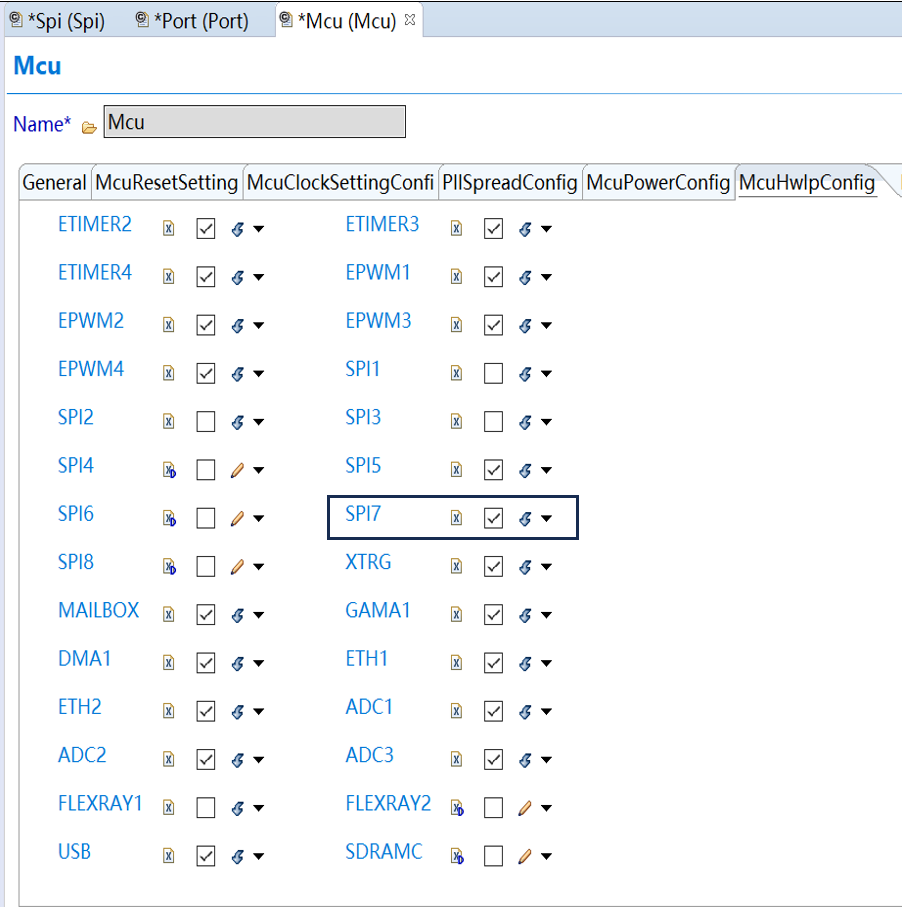

3.1、Mcu

图 (3)

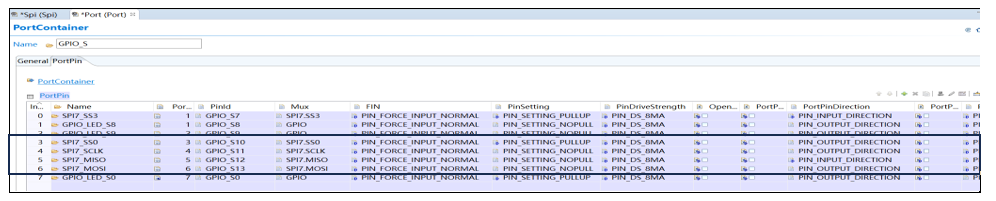

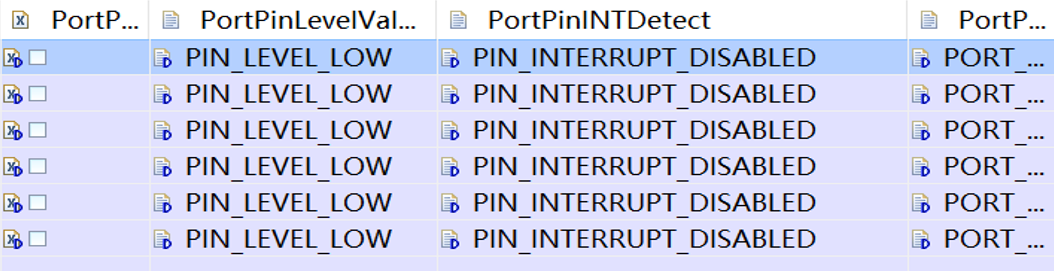

3.2、Port

图 (4)

图 (5)

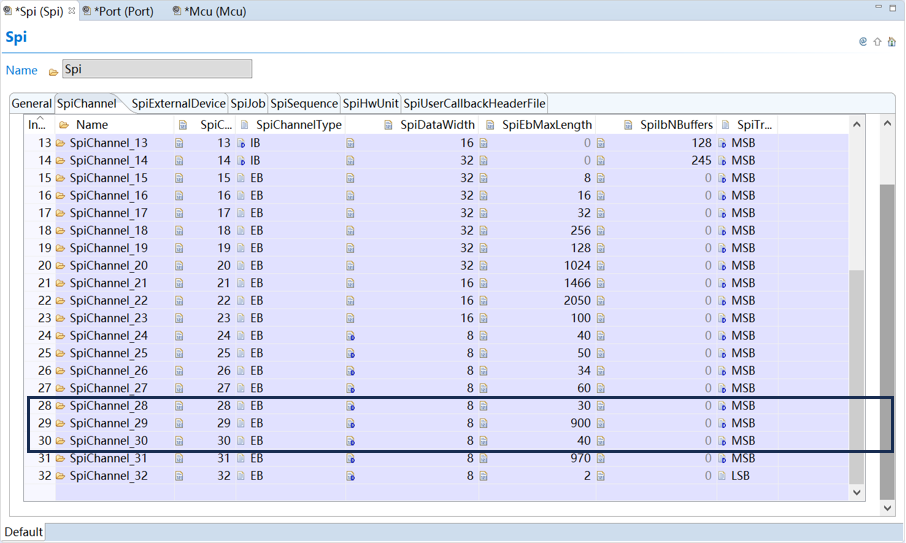

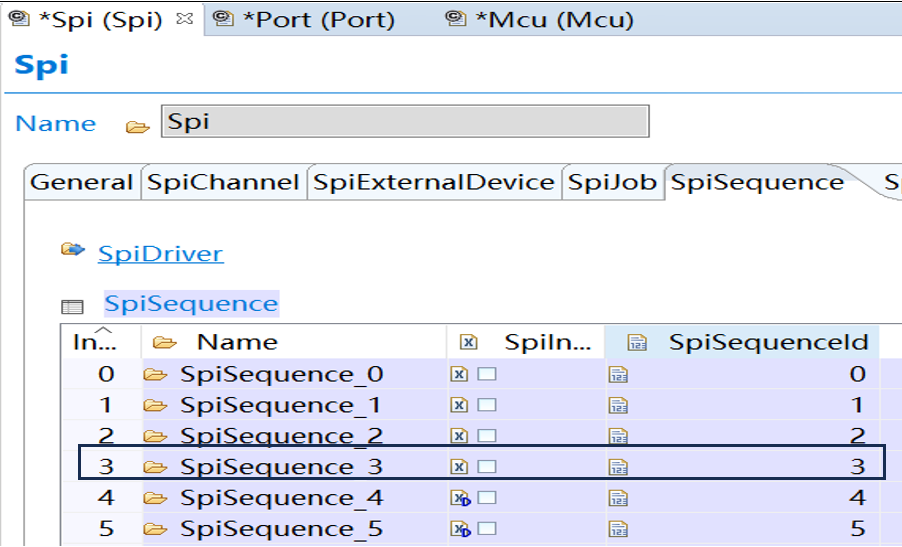

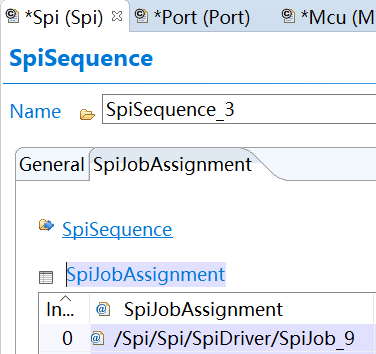

3.3、Spi

图 (6)

SpiEbMaxLenth 等同于 spi_test.c 中的 SPI_BUFFER_SIZE_CHANNEL_x。

SpiChannel:

- SpiChannId:全局唯一的数据 Buffer 识别号,配置过程必须保持这个编号连续且单调递增,生成时会根据 BufferId 编号排序。

- SpiChannelType:数据 Buffer 类型主要有两种 IB 和 EB 区别和意义如下:

IB:内部 Buffer,由 Spi 驱动内部定义生成对应的数组,用户在数据传输前需先通过 WriteIB 接口将数据由用户提供的内存区域拷贝到驱动内部的 Buffer 中,然后在数据传输完成后通过 ReadIB 将数据从 Spi 驱动内部拷贝到用户目的内存区域。

EB:外部 Buffer 这里的外部概念强调是 Spi 驱动的外部,就是用户定义的数据缓存区,数据传输前必须通过 Setup_EB 接口设置外部数据缓存区地址及长度信息;数据传输完成后接收到的数据已经直接存放在用户指定的内存地址空间中,对比 IB 的类型的数据 Buffer 这里少了 1-2 次数据拷贝操作,但是在使用异步传输时要求用户提供的数据 Buffer 对应的内存空间在数据传输过程中不能有除了 Spi 驱动外的软件写入,要保证 Spi 驱动的独占访问,常见的错误使用方式是将数据 Buffer 定义在函数体内(栈上),当接口退出后栈会被其他的上下文使用此时就会出现竞争写栈空间导致收发的数据错误。

注:用户层提供的外部 Buffer 需要注意地址对齐,使用 dma 模式时统一按 32 字节对齐;否则不使用 DMA 时按数据位宽对应对齐 4-8bits 按 1 字节对齐,9-16bits 按 2 字节对齐,16-32bits 按 4 字节对齐;并且即使不需要更新此 EB 通道的数据缓冲区地址,每次传输前都需要重新调用接口设置 EB Buffer 的地址信息---即使此时设置的地址可能每次都是相同的。

- SpiDataWidth:

传输的数据宽度,单位 bit。这里需要说明的是内部在处理不同数据宽度的时候实际是还是按字节 (4-8bits)、双字节(9-16bits)、字(17-32bits) 的方式来进行处理的,也就是对 EB 类型的数据 Buffer 而言,用户也需要遵循这个规则;同一个SpiJob 下的所有数据 Buffer 的数据宽度都必须保持一致。

- SpiDefaultData:

默认发送数据,当用户不配置时候默认为全 FF 值,具体取决于数据宽度配置。

- SpiEbMaxLenth:

仅当数据 Buffer 类型为 EB 时此选项有意义,其限制了这个数据 Buffer 允许传输的数据长度的最大值,实际传输过程传输的数据量可以小于这个值。

- SpiNBuffers:

仅当数据 Buffer 类型为 IB 时此选项有意义,其定义了这个数据 Buffer 的数据长度,实际传输时也永远是这个长度。

- SpiTransferStart:

定义当前数据 Buffer 的 bit 序,LSB 为低 bit 优先反之为高 bit 优先;同一个 SpiJob 下的所有数据 Buffer 的比特顺序都必须保持一致。

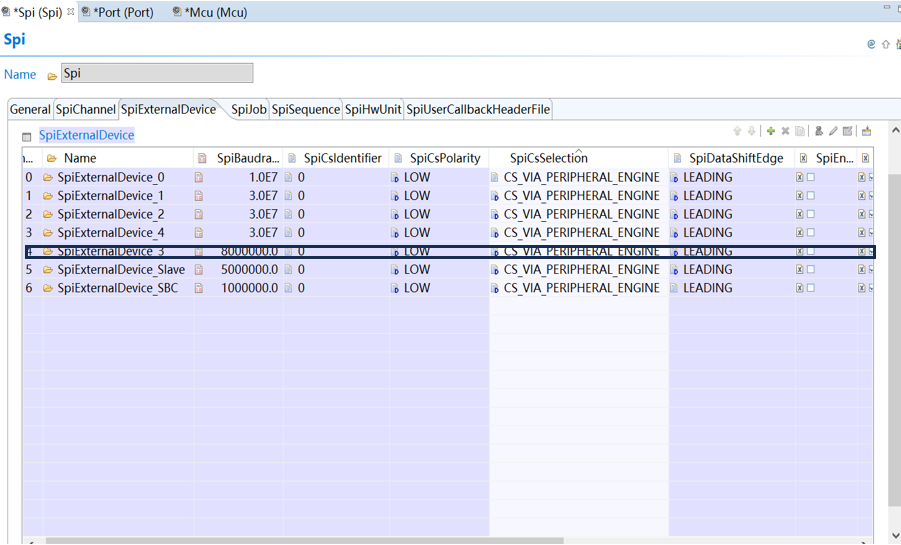

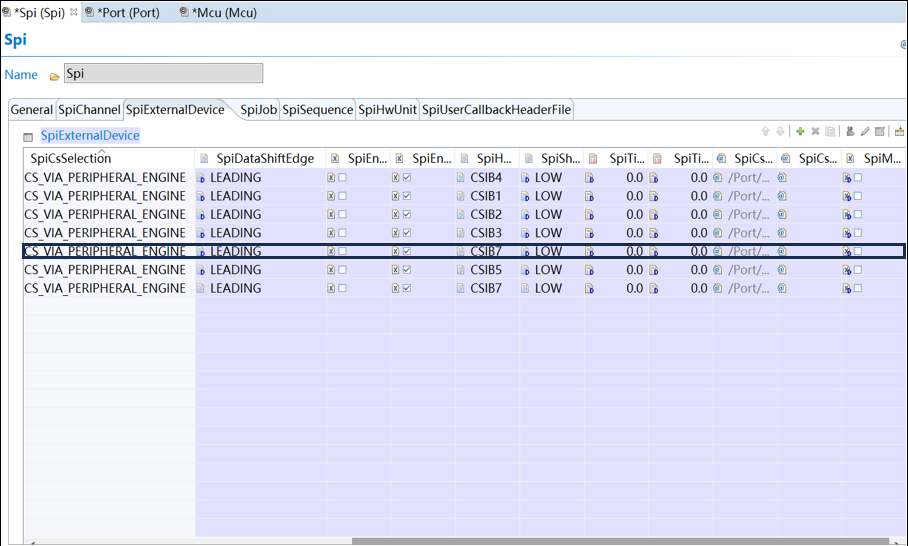

图 (7)

图 (8)

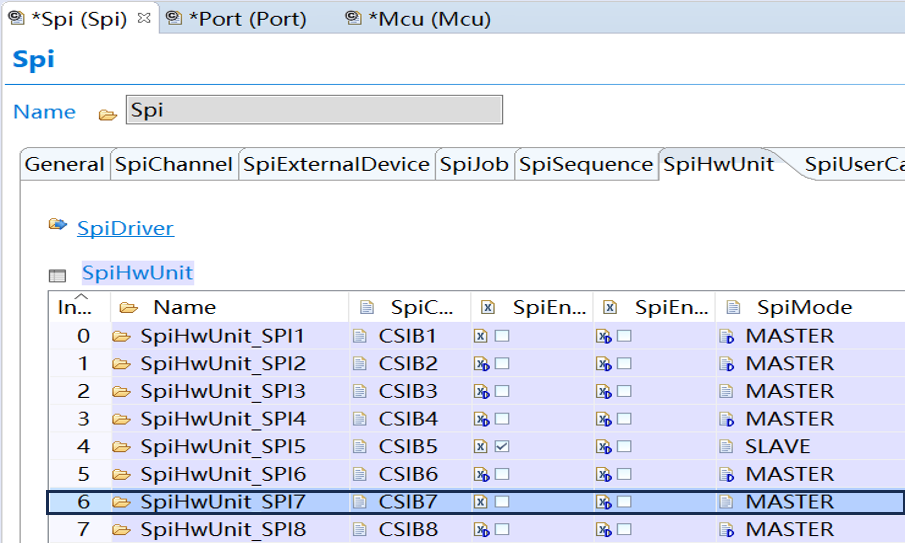

SpiExternalDevice:

- SpiBaudrate:单位 bps, 500000 就是 500Kbps,Master 模式最大支持到 25Mpbs@100M (当走线或对端 Slave 移出数据的时机偏晚时需要使能 Master 的 MISO 采样延迟,以确保正确采样 MISO 值),Slave 模式最大支持到 25Mbps@100M 最小 200K。

- SpiCsPolarity:片选信号极性。

- SpiEnableRx:是否使能接收。

- SpiHwUnit:指示此设备挂接在哪一路 SPI 控制器上 SPI1-SPI8 对应 CSIB1-CSIB8,当作为 Slave 时意义相同。

- SpiTimeClk2Cs:片选信号有效后延时多少秒(实际是以 sclk 的周期为单位)后再出 sclk 信号,对应通用概念建立时间,仅仅在使用硬件 CS 且作为 Master 模式此配置参数有意义。

- SpiTimeClk2CsEnd:传输结束 sclk 信号停止后延时多少秒(实际是多少个 sclk 的 clk 周期)后再驱动片选信号取消片选,对应通用概念的保持时间,仅仅在使用硬件CS且作 Master 模式此配置参数有意义。

- SpiCsViaGpio:当选择通过软件控制 GPIO 来驱动片选信号的情况下这里需要配置,指定一个 GPIO 引脚作为片选信号的控制。当使用软件控制 GPIO 来驱动片选信号时需要注意此时硬件 SS0 信号如果不特殊处理,可能会同时出现硬件驱动的片选信号 SS0 和软件控制的 GPIO 两个片选信号同时选中两个外部设备从而导致通信冲突,特殊处理方式参 SpiCsPin 配置项说明。

- SpiCsIdentifier:Spi 控制器支持四个 CS 引脚信号控制,使用 0-3 对应 SS0-SS3;当 SpiCsSelection 选择 VIA_GPIO 时,此配置项无效,但要求配置为 0。

- SpiDataShiftEdge/SpiShiftClockIdleLevel:配置 SPI 通信时序参考后续的表格。

- SpiCsSelection:配置当前设备使用的 SPI 控制器硬件控制的片选信号还是软件通过 GPIO 驱动的。

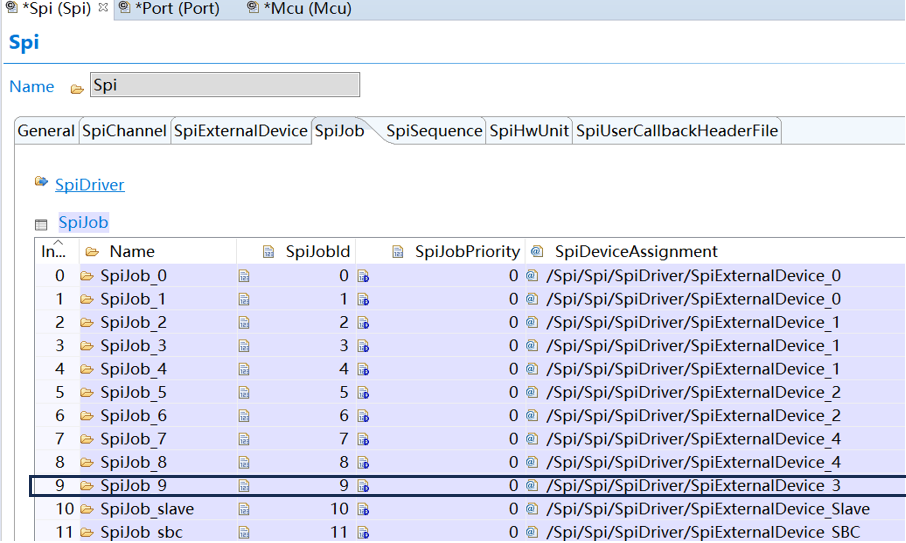

图 (9)

图 (10)

图 (11)

图 (12)

图 (13)

4、IAR

Spi_test.c 函数结构:

SPI_BUFFER_SIZE_CHANNEL

fifo_init;fifo_show:static void fifo_init(void* addr,uint32 val,uint32 len,uint8 width),第二个参数是 SPI 的值,共 32 位无符号整型;

Tc_spi_asny_03

Tc_spi_async_03_less

async_transmit_slave

Tc_spi_async_loop_back

Tc_spi_async_loop_back_early_cs_end

spi_loop_demo

Spi_test.c 默认不做更改。

5、硬件连接

图 (14)

LAP-C PRO(32128M) A0 连接 GPIO_S10 做 SPI7_SS0;

LAP-C PRO(32128M) A1 连接 GPIO_S11 做 SPI7_SCLK;

LAP-C PRO(32128M) A2 连接 GPIO_S13 做 SPI7_MOSI;

LAP-C PRO(32128M) GND 连接 GPIO_S10 做 SPI7_GND;

6、SPI 测试

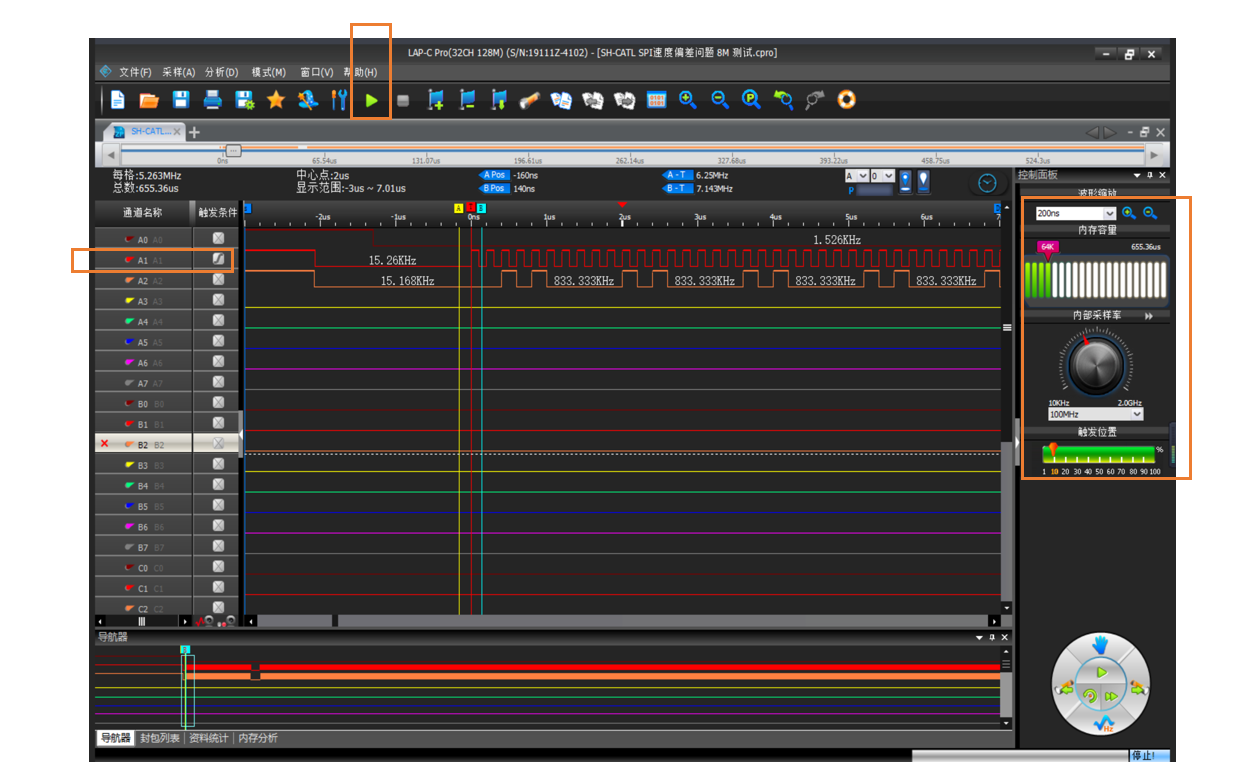

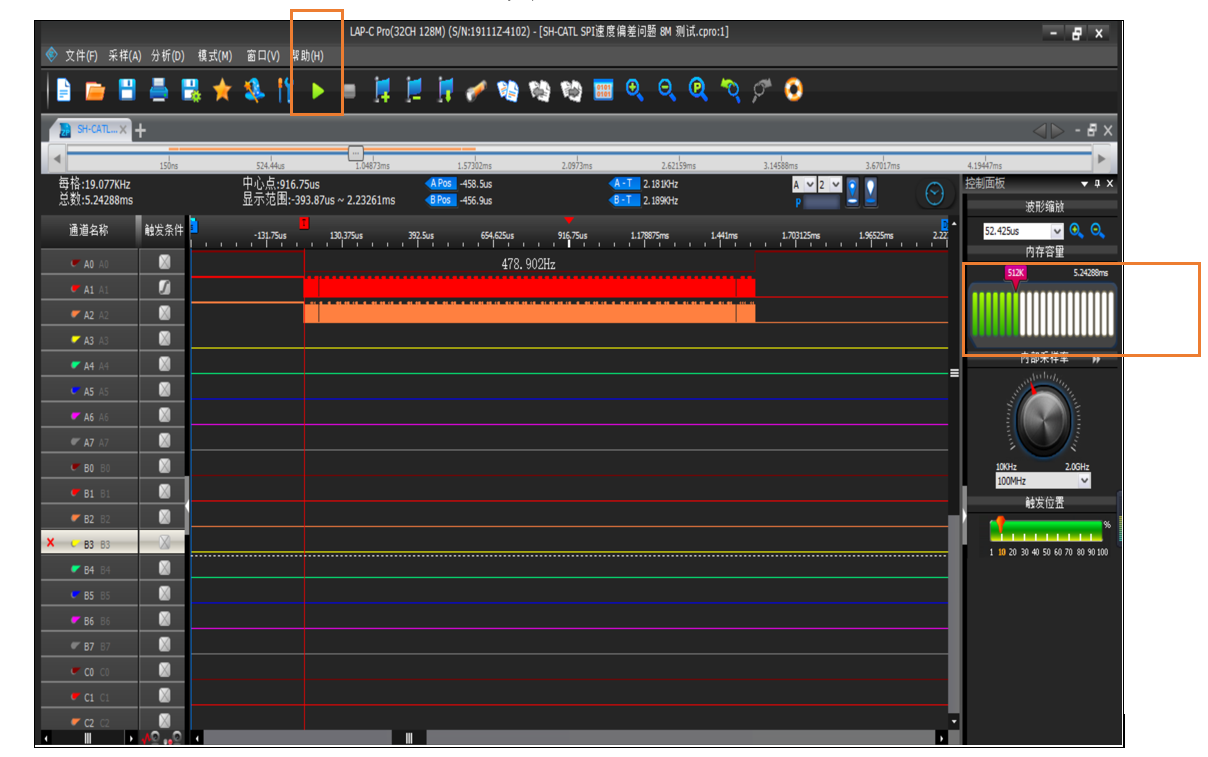

6.1、使用逻辑分析仪 LAP-C PRO(32128M)

图 (15)

图 (15)

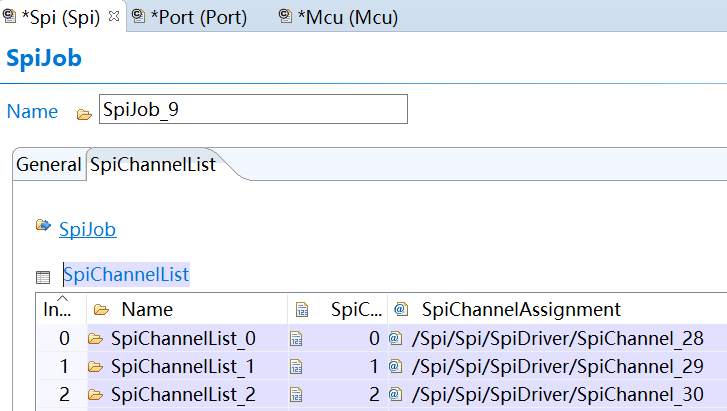

图 (16) 一个 JOB 三个通道:channel_28,channel_29,channel_30

一个片选内只有一个 JOB 的内容。

channel_28:0010 1000 0010 1000 0010 1000 0010 1000

channel_29:0010 1001 0010 1001 0010 1001 0010 1001

channel_30:0011 0000 0011 0000 0011 0000 0011 0000

一个时钟周期内传递一个 bit 的数据。

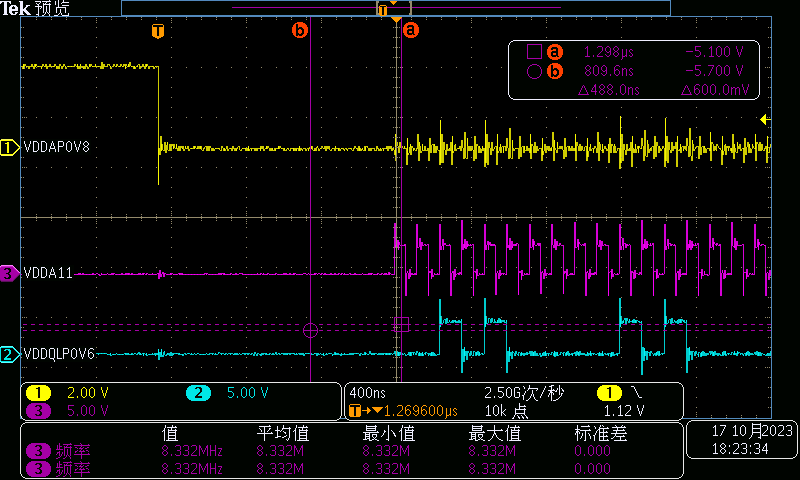

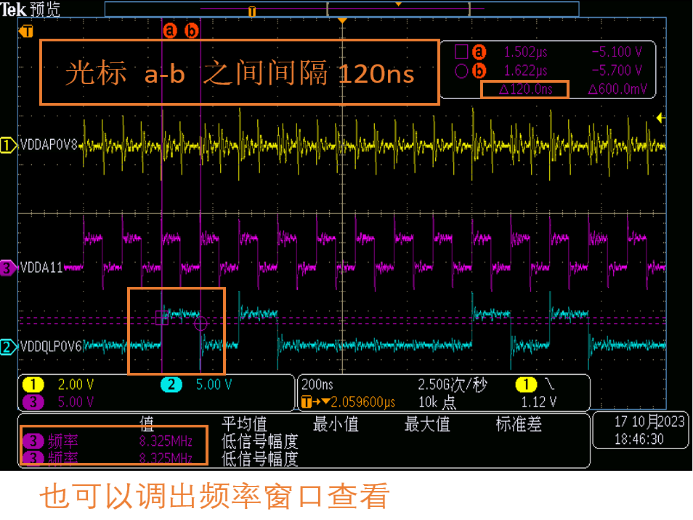

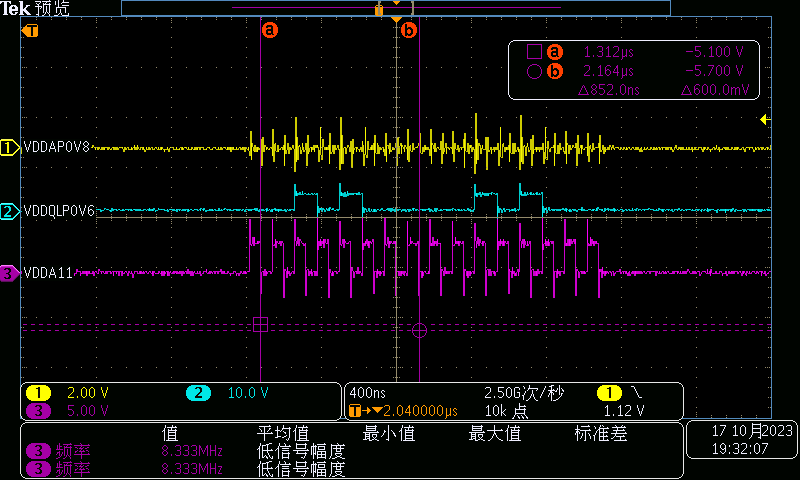

6.2、使用示波器(Tektronix MDO3054)

图 (17)

图 (18)

SS0:gpio_s10->示波器通道 1

SCLK:gpio_s11->示波器通道3

MOSI:gpio_s13->示波器通道 2

频率 8M 如何计算得知:一个 bit 是 120ns,1/120ns≈8.333M。

图 (19)

若 SpiChannel_28 的 SpiEbMaxLength 设为 4,则传输的数据是 2828=0010 1000 0010 1000。

图 (20)

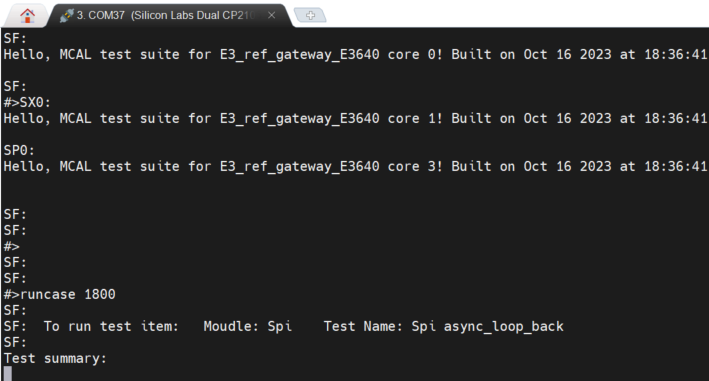

7、串口发命令

Help->listcase->runcase 1800;

图 (21)

注1:SPI 四种模式

|

SpidataShiftEdge |

SpiShiftClockIdLevel |

Spi mode |

|

LEADING |

LOW |

MODE1 |

|

TRAILING |

LOW |

MODE0 |

|

LEADING |

HIGH |

MODE3 |

|

TRAILING |

HIGH |

MODE2 |

表 (3)

MODE0:时钟线空闲时低电平,第一个跳变沿(采样点)在第一个 bit 的中间

MODE1:时钟线空闲时低电平,第二个跳变沿(采样点)在第一个 bit 的中间

MODE2:时钟线空闲时高电平,第一个跳变沿(采样点)在第一个 bit 的中间

MODE3:时钟线空闲时高电平,第二个跳变沿(采样点)在第一个 bit 的中间

注2:Spi 会根据 MCU 配置支持 1,3,5 三种数量的多核场景,默认不在 ResM 进行任何配置的情况下,Spi 工作在单核模式所有的资源划分在 SF 核心上。当有需要将不同 Spi 控制器分在不同核心上时需要在 ResM 模块中进行配置,详见 《SemiDrive_E3_MCAL User Guide》。

参考资料:

《E3400&E3600 Series MCU Datasheet Release 00.16》

《E3400&E3600 MCU Technical Reference Manual Release 00.12》

《SD103_E3_REF_GATEWAY_ePOWERTRAIN_A02_丝印图》

《SD103_E3_REF_GATEWAY_ePOWERTRAIN_A02_SCH》

《SemiDrive_E3_MCAL User Guide》,适用 MCAL PTG3.0 及后续版本

欢迎在博文下方留言评论,我们会及时回复您的问题。如有更多需求,欢迎联系大联大世平集团 ATU 部门:atu.sh@wpi-group.com

作者:Rita Liu / 刘倩

评论