一、Semidriver E3400 & E3600 系列时钟

1、以 E3430 为例,时钟模块

处理器集成了以下时钟和复位生成块。

① RC_RTC :RC 32KHz 振荡器

② RC_OSC :RC 24MHz 振荡器

③ PLL :PLL

④ CKGEN :时钟发生器

⑤ RSTGEN :复位发生器

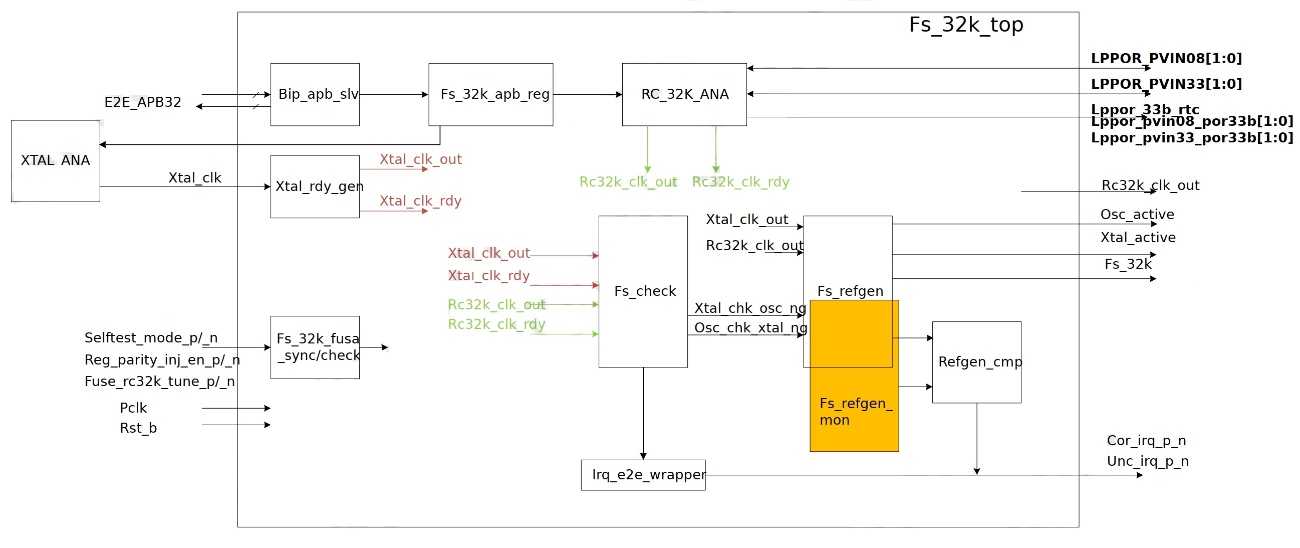

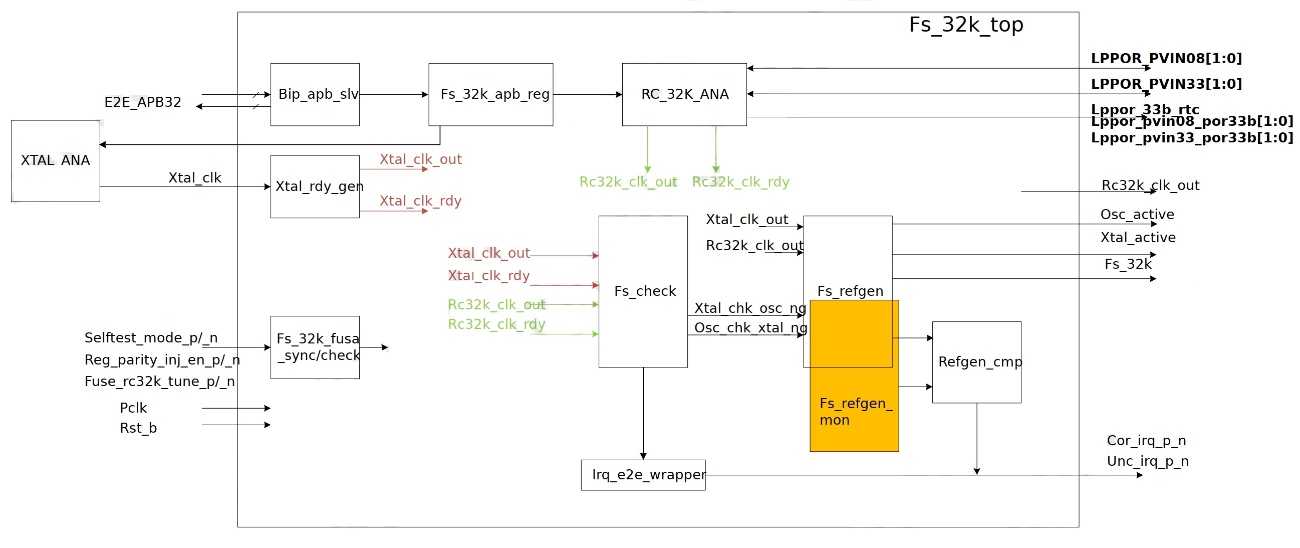

2、FS_32K

FS_32K 是一种具有故障保护功能的 32KHz 系统发生器。

FS_32K 的主要功能如下:

• 支持片外 xtal 32KHz 时钟源。

• 支持片上 RC 32KHz 时钟源。

• 支持故障保护自动切换。

FS_32K 的高级框图如下:

(1)FS_32K 时钟模块时钟来源

① 时钟源一般默认是内部 RC32K

特性如下: RC 32K 时钟模块的供电来自 RTC_VDD

| Parameter | Symbol | Condition | Min | Typ | Max | Unit |

| VIN power | VIN | - | 3 | 3.3 | 3.6 | V |

| Power consumption | Iout | - | 0.5 | 1.2 | uA | |

| Frequency | Fre | 20 | 32 | 50 | kHz | |

| Setting time | Tset | When power up | - | 0.3 | 1 | ms |

| Duty Cycle | Duty | - | 45 | 50 | 55 | % |

| RTC POR threshold | Vpor_rtc | - | 0.6 | 1.5 | 2 | V |

| RTC BOR threshold | Vbor_rtc | - | 0.46 | 1 | 1.37 | V |

② 用户可以自行切换到外部晶振 32.768K

(2)FS_32K 时钟模块时钟切换

① 切换到外部晶振需要等 MCU 上电后一秒进行切换

② 切换函数如下:

Mcu_RtcTrySwitchToXtal(FS_32K_BASE_ADDR);

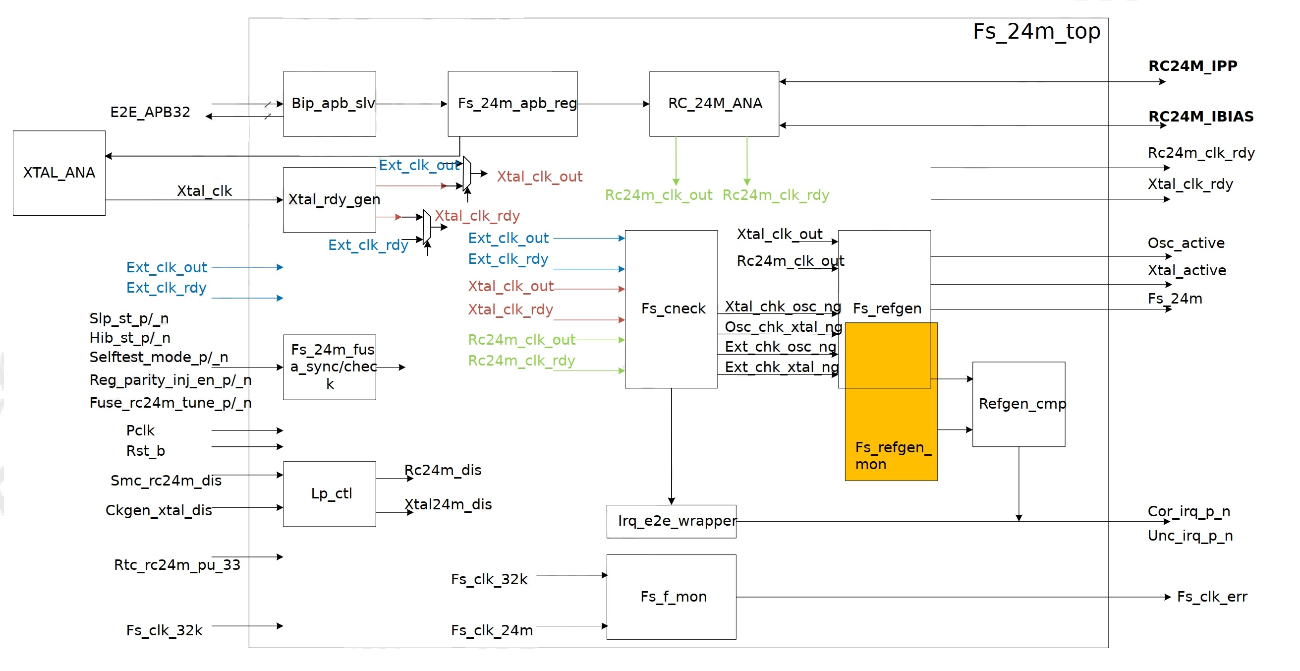

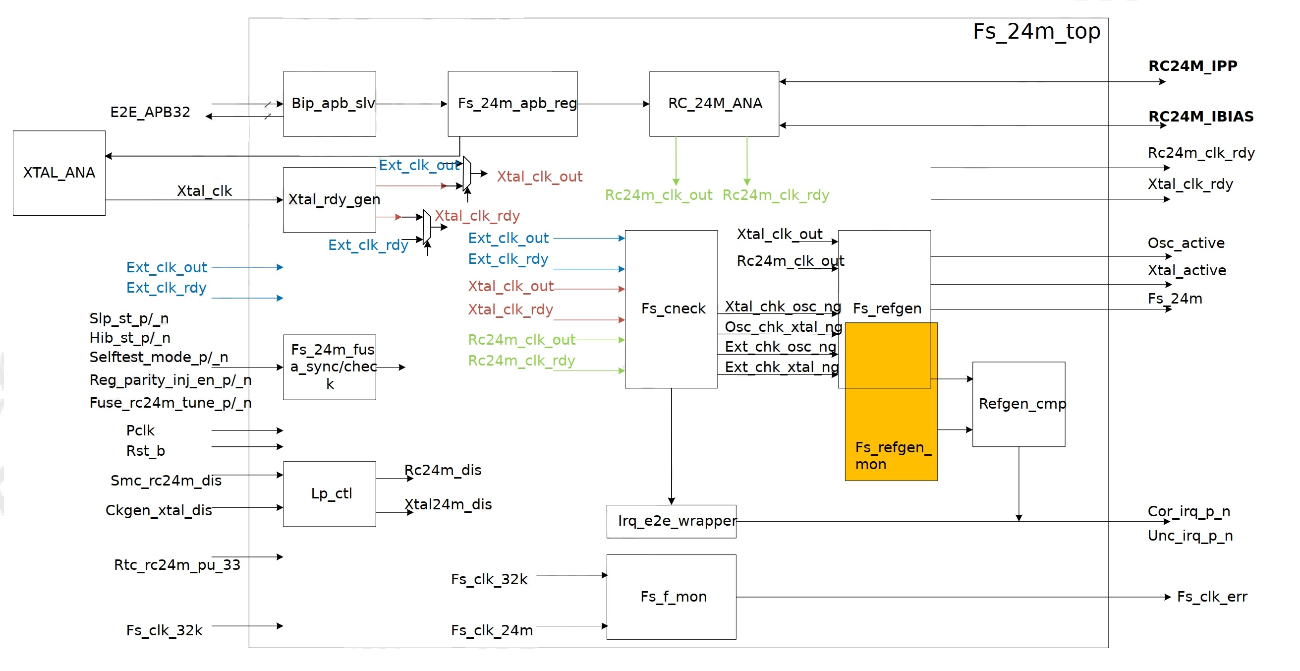

3、FS_24M

FS_24M 是一种具有故障保护功能的 24MHz 系统发生器。

FS_24M 的主要功能如下:

• 支持片外 xtal 24MHz 时钟源。

• 支持片上 RC 24MHz 时钟源。

• 支持片外单端 24MHz 时钟源。

• 支持故障保护自动切换。

FS_24M 的高级框图如下:

(1)FS_24M 时钟模块时钟来源

① 默认使用内部 RC 24M 时钟源后自动切换外部 24M

时钟初始化后,使用的是外部的 24M 时钟源,寄存器已经配置使用外部 24M 晶振

内部 RC 24M 时钟源特性如下:(一般使用外部时钟源,只看外部晶振特性)

| Parameter | Symbol | Condition | Min | Typ | Max | Unit |

| VIN power | VIN | - | 3 | 3.3 | 3.6 | V |

| Power consumption | Iout | - | 45 | 55 | 75 | uA |

| Frequency | Fre | 22 | 24 | 26 | MHz | |

| Clock start up Time | Tstart | When power |

up

4、FS_32K & FS_24M 安全机制

(1)每个时钟模块有自己的监控模块

当 failsafe function 开启,内部时钟和外部时钟可以在任何一方时钟缺失时,自动切换。

(2)功能安全机制

Fs_clk_32k 和 Fs_clk_24m 相互检查监控,当阈值超过设定值,功能安全机制可以读到时钟的错误。

此监视器可通过软件关闭,默认为启用状态。Fs32k 的频率范围是从 12k~128k, Fs24m 频率范围默认为6m~48m。这个阈值可以是由软件改变。在更改阈值之前,软件需要关闭监视器。

5、PLL

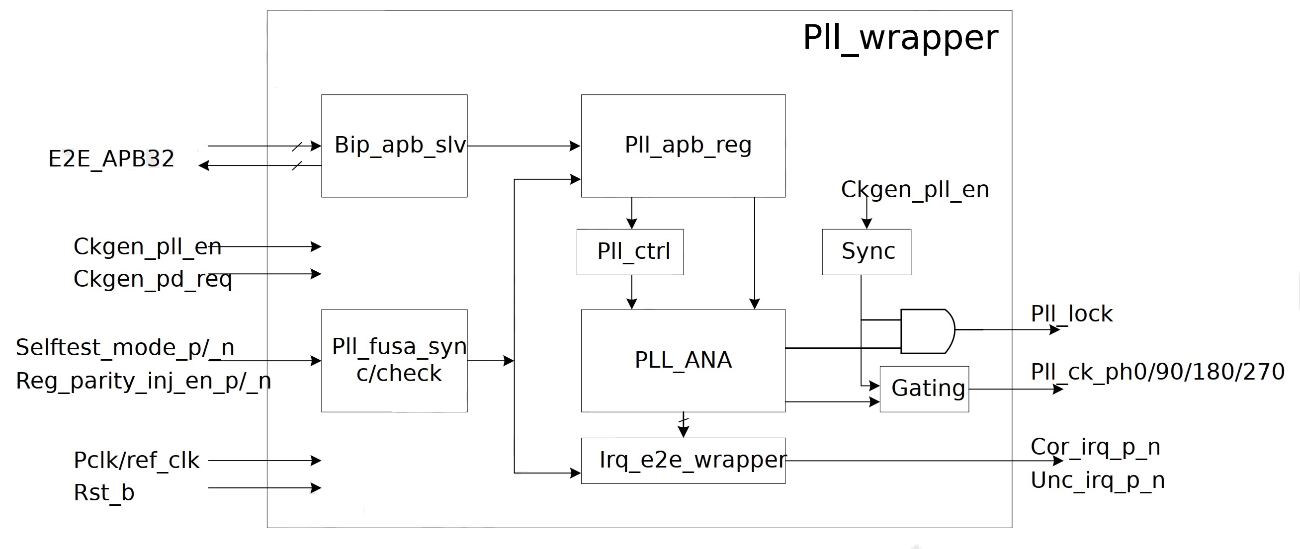

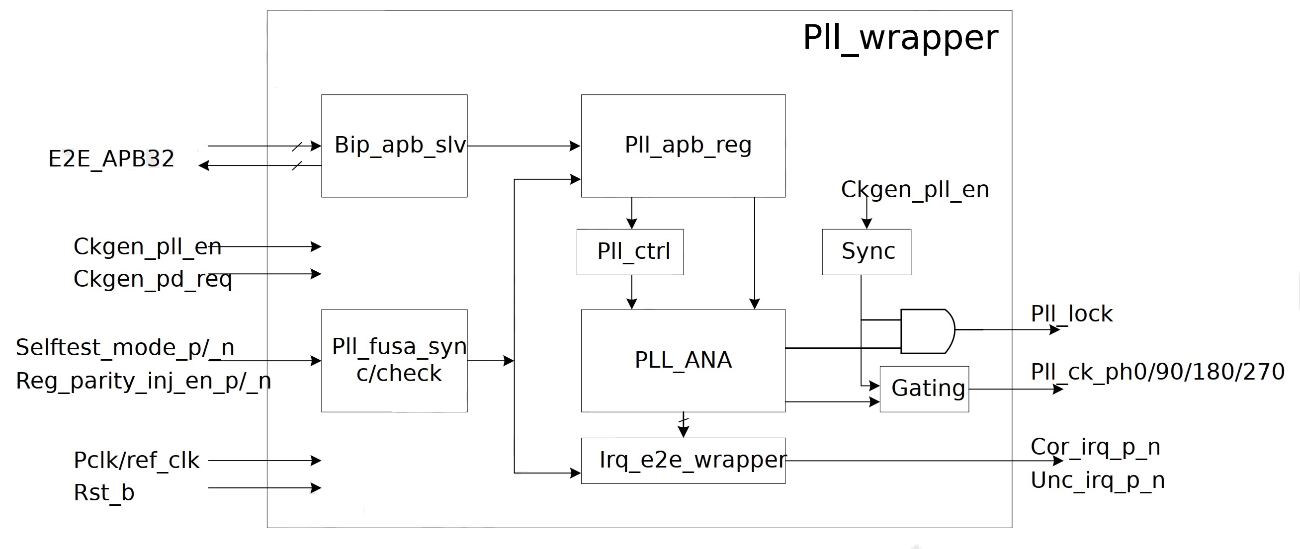

PLL_WRAPPER 的主要功能如下:

• 与 CKGEN 合作完成 PLL 时钟分配。

• 模拟 Pll 状态监视器。

• 模拟 Pll 控制

E3430 主频达到 600MHz,一般采用 PLL 倍频方式提升主频。

PLL_WRAPPER的高级框图如下:

(1) PLL 时钟来源

PLL 时钟源是 Fs_24M ,E3430 MCAL Release 版本工程时钟源就是外部晶振 24M.

PLL 特性如下:

| Parameters | Symbol | Min | Typ | Max | Unit |

| Input Power Supply | AVDD_SAFETY / AVDD_AP | 3 | 3.3 | 3.6 | V |

| Reference Frequency range | Fin | - | 24 | - | MHz |

| Output Frequency range | Fout | 400 | - | 1200 | MHz |

| Duty Cycle | DUTYout | 48 | 50 | 52 | % |

| Period Jitter (Peak to Peak) | Tpj | - | - | 2% | Tout |

| Fractional Accuracy | Fraaccu | - | 1/2^(24) | - | |

| SSC Modulation Rate | F ssc_m | 30 | - | 33 | KHz |

| SSC Modulation Range | Fssc_rg | 0.10% | - | 3.10% | Fout |

| SSC Modulation Step | Fssc_step | - | 0.10% | - | Fout |

| Start Up Time (max) | Tstar | - | 120 | - | uS |

| Power consumption | IDC | 5 | - | mA |

(2)PLL 时钟误差计算

PLL Period Jitter (Peak to Peak) 最大是 2% , 对于各个模块的时钟来计算,有以下公式,举个例子,假如 600M 主频,配置到 CAN 的波特率是 500K, 那么 CAN 的时钟的 Jitter 就是:

jitter=1/1mhz*2%/sqrt(600/0.5)

另外,外部的晶振的误差也必须加上,才是最终的时钟误差。

二、时钟配置

1、MCAL Release 版本代码

在 MCAL EB 配置中,目前已经配置了各个模块的时钟源,用户只需要勾选使用即可,暂时没有开放给用户自己配置时钟树。

三、参考

芯驰官网:TRM & Datasheet 手册

评论