1、简介

越来越多的行动装置和其他电子设备使用了不同的半导体零件来实现其高性能,做为 LDO 负载的半导体部件,例如图像感测器,若 LDO 的输出电压变动,就有可能引起电子元件的动作不良或性能劣化。因此,LDO 必须提供稳定的电源电压,以实现高效能的半导体元件正常运作。

电源抑制比 (PSRR) 是 LDO 最重要的性能项目之一。本文介绍 PSRR 的原理,并透过了解频率特性和输出电容器对 PSRR的影响,为电子设备设计中选择和使用合适的 LDO 提供了帮助。

2、LDO 电源抑制比 (PSRR) 的重要性及其定义

LDO (线性调节器) 是指将电池或 DC-DC 转换器等产生的直流电压 (LDO的输入电压) 转换为其他更低的直流电压后输出的电源元件。此时,对 LDO 的输入电压不一定是理想的直流电压,它可能包含涟波,对由 LDO 供电的电子设备产生不良影响。

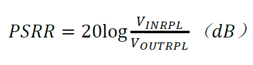

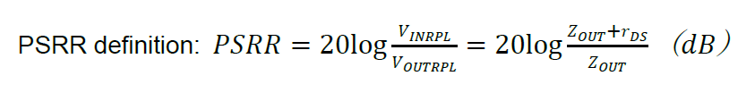

LDO 的 PSRR 即其抑制输入电压 (VIN) 涟波的能力,由下列等式指定。

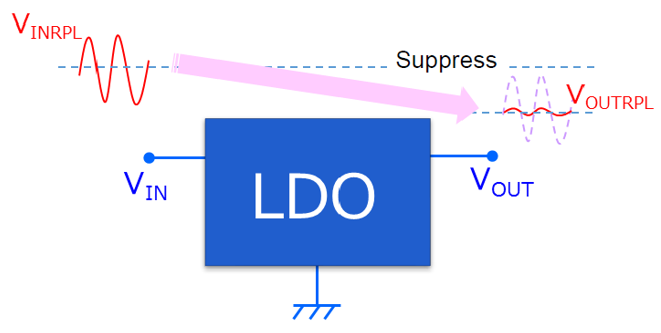

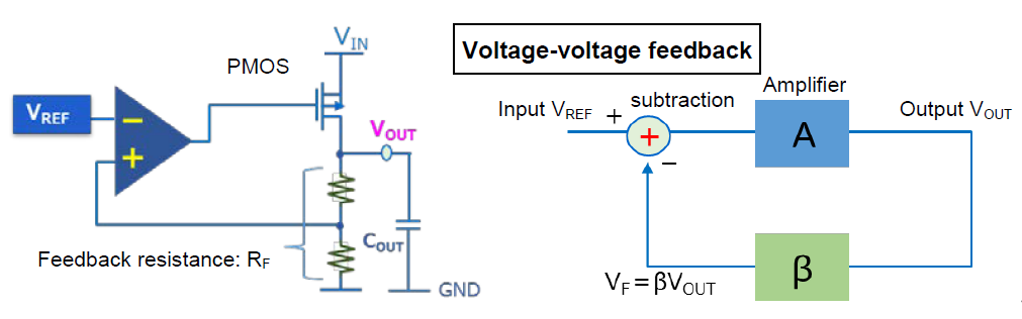

下图显示了具有 PMOS的典型 LDO 以及提供给其负载的输出电压波形。

VINRPL : LDO 输入电压 VIN 的涟波分量

VOUTRPL : LDO 输出电压 VOUT 的涟波分量

3、LDO PSRR 频率依赖性的基础原理

3.1 决定 PSRR 的因素

哪些因素决定 LDO 的 PSRR?

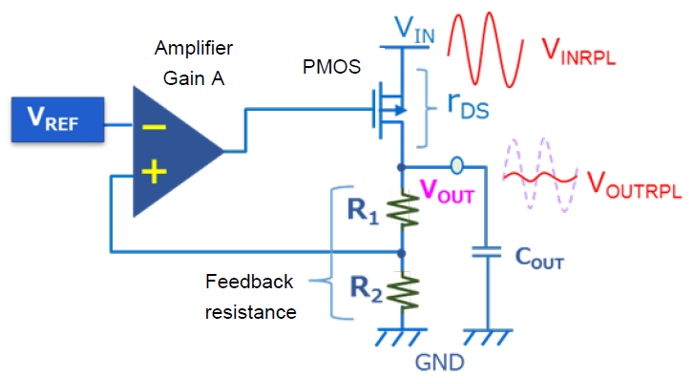

上图为一典型 LDO 的电路图。 如果 PMOS 传输元件的闸极电压涟波等于 VIN 上的涟波 (VINRPL),则闸极电压与 VIN 同时变化,同时保持恒定的电压差。在这种情况下,PMOS 传输元件不会因 VIN 涟波而将任何电流传输至输出。这是正确的,因为从理论上讲,PMOS 传输元件的闸极电压和输入电压 (VIN) 具有相等的涟波。在这种情况下,VIN 涟波电压会根据 LDO (即负回授的低阻抗) 的输出阻抗 (ZOUT) 与 PMOS 传输元件的输出电阻 (rDS) 比值来划分。 因此,PSRR 由此分压比决定。

此外,LDO 输出阻抗 ZOUT 由于负回授而变低 (下文将描述ZOFB),但由于 LDO内部放大器的增益是实现低 LDO 输出阻抗所必需的元件,因此 PSRR 也具有频率依赖性。

3.2 负回授对 LDO 输出阻抗降低的影响

LDO 是电压-电压回授 (串并联回授),将输出电压 (VOUT) 施加到输入,以维持稳定的输出电压。使用负回授的额外好处是降低输出阻抗 (ZOUT)。

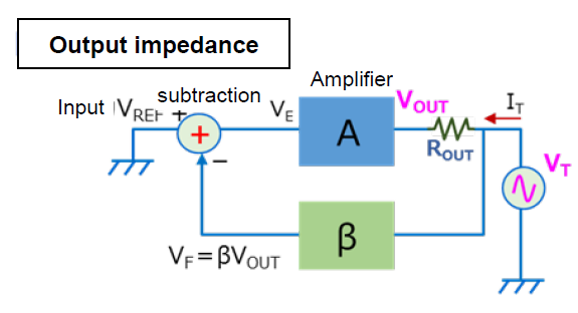

其输出电阻可以透过在输出端输入测试讯号 VT 来计算,如下图所示,在不乘以负回授的情况下,输出电阻 ROUT 减小到约 1/Aβ(A: LDO 内部放大器的增益,β: 回馈因数)。

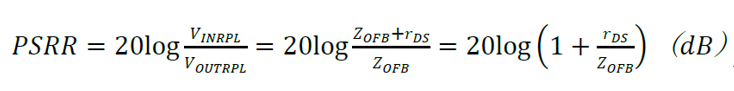

由于典型负回授系统中的放大器具有 100dB 量级的大增益 (A),因此输出阻抗 (ZOFB) 小得可以忽略不计,小于放大器固有输出阻抗 (ROUT) 的万分之一。 考虑到这一点,PSRR 可计算如下:

如 PSRR 公式所示,如果输出阻抗 ZOFB 远小于输出 PMOS 的输出电阻 (rDS),则 PSRR 值将会更高。包含在上式输出阻抗 ZOFB 中的 LDO 中的放大器的增益具有频率特性,并且在高频区域中其增益降低。因此,负回授对输出阻抗的降低效应在高频区域会降低,PSRR 也会随之在高频区域恶化。

3.3 LDO 频率依赖性详述

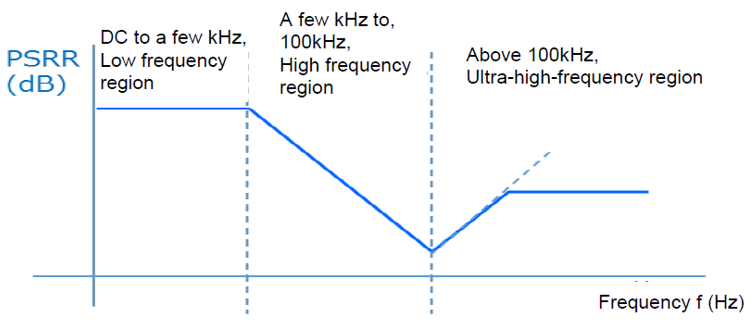

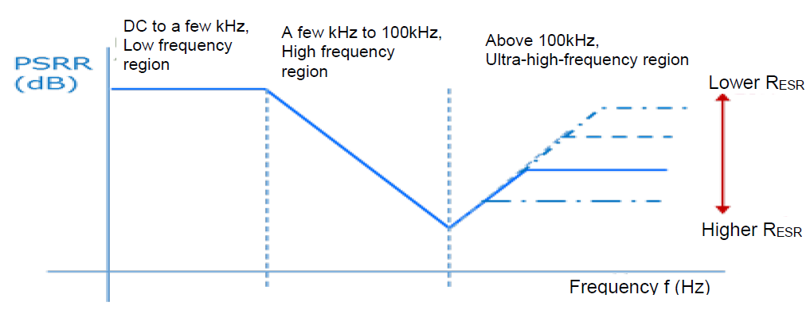

LDO 的 PSRR 具有频率依赖性,通常在低频区域 PSRR 较高,在高频区域 PSRR 较低,大致分为以下三个区域:

・从 DC 到几 kHz 的低频区域

・几 kHz 至 100kHz 的高频区

・约 100kHz 或更高的超高频区域

与低频区域的情况一样,高频区域的 PSRR 是 VIN 纹波除以负回授 LDO 输出阻抗 (ZOFB) 与 PMOS 输出电阻 (rDS) 的比率。在高频区域,内部放大器的增益取决于频率,决定了 LDO 的输出阻抗 (ZOFB)。 因此,ZOFB 随著频率的增加而减少。在这种情况下,PSRR 随著增益的减少而变小。

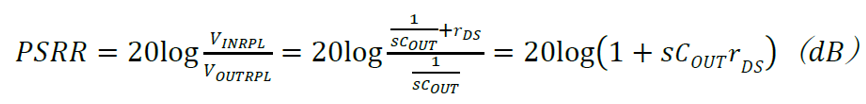

由下面的方程式得知,当输出电容器 (COUT) 越大,PSRR 越高。

如上图,PSRR 在高频区域下降。较大的电容器 (COUT) 让 PSRR 在相对较低的频率下再次增加,因为它提供较低的电容阻抗 (即较大的 COUT)。 因此,大输出电容有助于在高频下保持高 PSRR。相反地,当输出电容器 (COUT) 较小时,PSRR 持续下降直至相对较高的频率。 (前提:假设等效串联电阻 (RESR) 是恒定的)

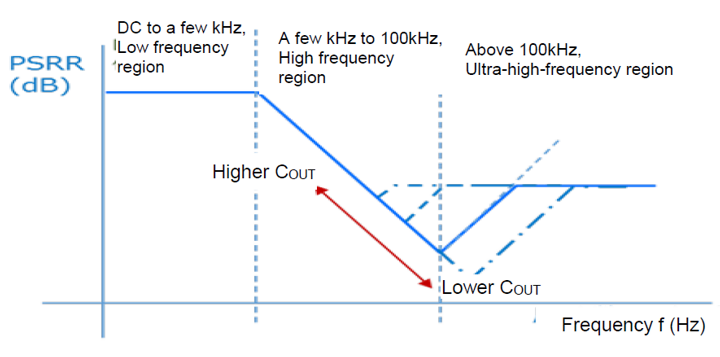

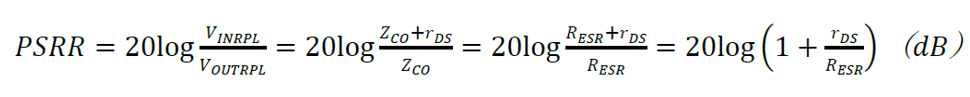

以下方等式所示,在超高频区域,具有较低等效串联电阻 (RESR) 的输出电容器 (COUT) 可提供较高的 PSRR。

参考下图,前提为假设输出电容值 (COUT) 恒定。

为了提高 PSRR,使用具有最大电容值和较小等效串联电阻 (RESR) 的输出电容器 (COUT) 是有益的。然而,大输出电容器 (COUT) 会导致 LDO 输出电压 (VOUT) 上升期间突波电流增加,甚至在最坏的情况下会导致振荡。 此外,输出电容器具有较小的等效串联电阻 (RESR) 不能提供足够的抗振荡能力。

实际上,由于 LDO 内外存在的寄生电感和电抗的影响,PSRR 的频率特性在大约 100 kHz 以上的超高频区域表现出复杂的波形。

4、总结

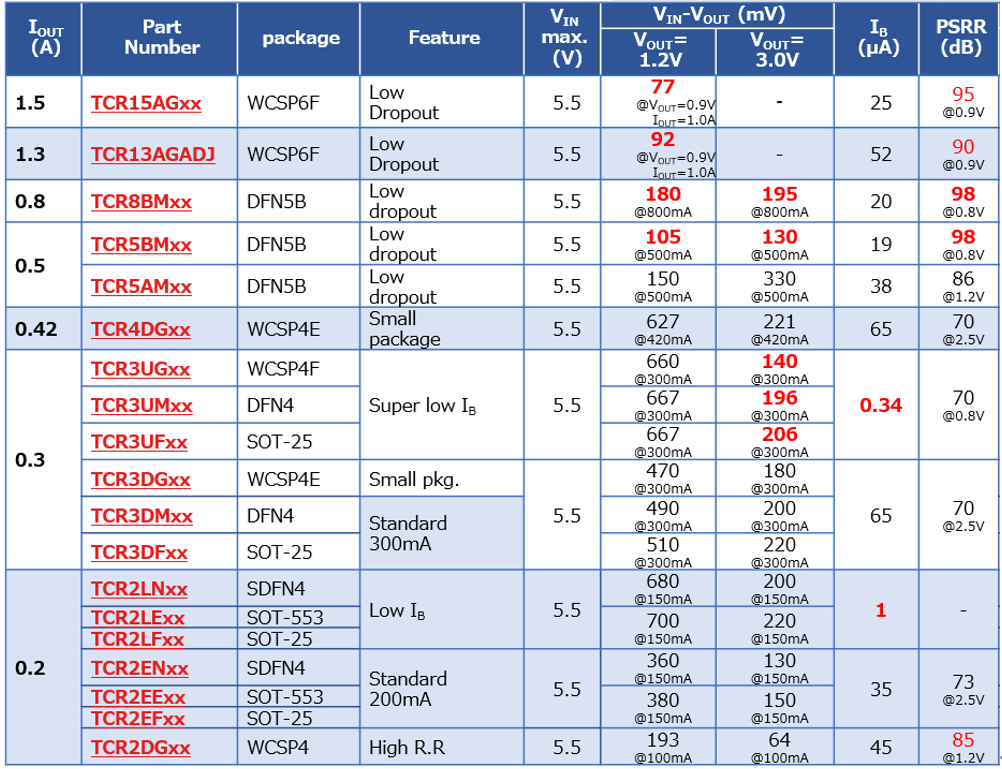

PSRR 是选择 LDO 的一项重要因素,即使在高频下也需要高 PSRR。为了提高 PSRR,使用具有适当且最大容值和低等效串联电阻 (RESR) 的输出电容器 (COUT) 是有效的。东芝的 LDO 在各方面参数之间进行了最佳化设计,低压系列产品中,目前已提供最高 PSRR 可达 98dB 的产品,输出电流分别有 0.5A 及 0.8A,最小封装则约为 1*1 的 SMD 和 BGA 型式。

点击连结以取得更详细的资讯

参考来源