PN7160虽已普遍使用,但开发初期进行软体整合时,如没有相关经验,容易发生问题(虽然NXP有提供相关的整合文件);本篇将介绍软体的整合步骤与问题分享。

另外,PN7160可以整合在Android与Linux上,本篇是介绍Android平台(目前支援A11-A13)。

- 确认硬体线路

在开始进行整合或是过程中,请务必与HW同仁确认相关线路是没问题的。

- 抓取code

- Driver code

$ git clone https://github.com/NXPNFCLinux/nxpnfc.git drivers/nfc

与i2c与spi等相关的程式码。

在platform端设定时请确认对应的address与每个pin对应之GPIO是否设置正确。

- AOSP adaptation

- 导入NFC patch

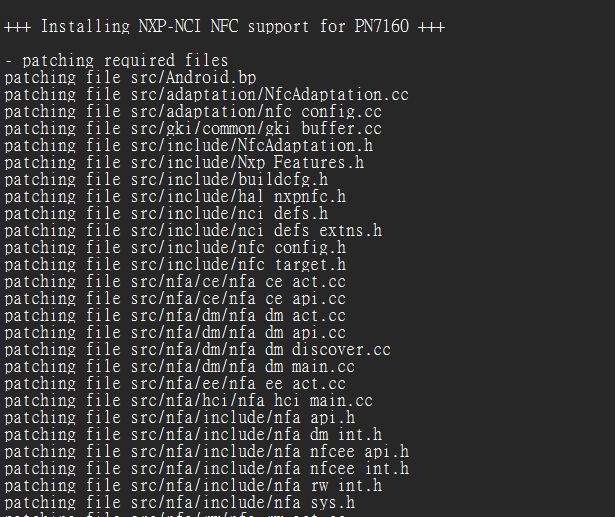

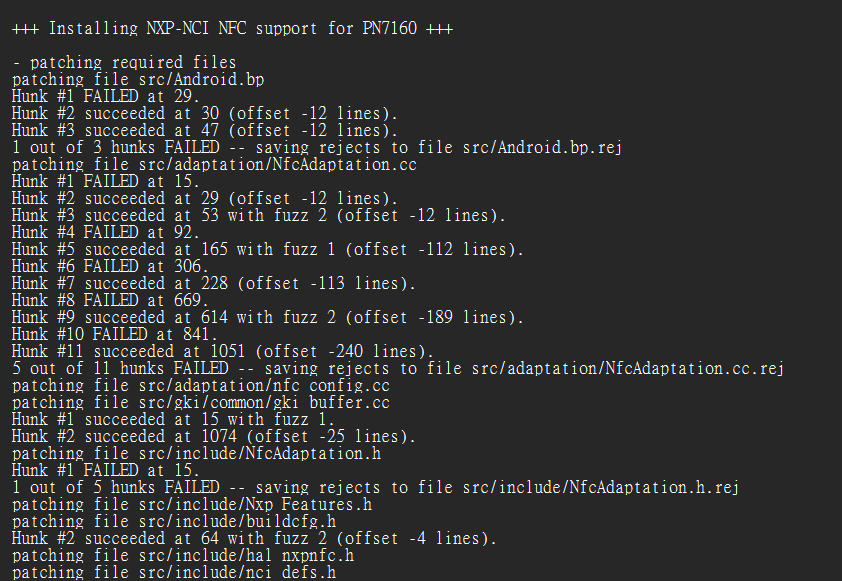

执行资料夹底下的install_NFC.sh,会自动将对应的patch导入。执行过中请确认是否有error message;如果有,请自行用手动修改,将patch内容进行整合。

•执行install_NFC.sh成功,没有冲突发生。

•执行install_NFC.sh过程有发生错误,需手动修改。

- 修改.conf档案

- Debug level在案子开发初期,建议全开。

###############################################################################

# Logging Levels. Suggested value for debugging is 0x03.

# NXPLOG_EXTNS_LOGLEVEL - Configuration for extns logging level

# NXPLOG_NCIHAL_LOGLEVEL - Configuration for enabling logging of HAL

# NXPLOG_NCIX_LOGLEVEL - Configuration for enabling logging of NCI TX packets

# NXPLOG_NCIR_LOGLEVEL - Configuration for enabling logging of NCI RX packets

# NXPLOG_FWDNLD_LOGLEVEL - Configuration for enabling logging of FW download functionality

# NXPLOG_TML_LOGLEVEL - Configuration for enabling logging of TML

NXPLOG_EXTNS_LOGLEVEL=0x03

NXPLOG_NCIHAL_LOGLEVEL=0x03

NXPLOG_NCIX_LOGLEVEL=0x03

NXPLOG_NCIR_LOGLEVEL=0x03

NXPLOG_FWDNLD_LOGLEVEL=0x03

NXPLOG_TML_LOGLEVEL=0x03

- 依照案子设定,调整clock来源与频率。

###############################################################################

# System clock source selection configuration

#define CLK_SRC_XTAL 1

#define CLK_SRC_PLL 2

NXP_SYS_CLK_SRC_SEL=0x02

clock来源是外挂XTAL,NXP_SYS_CLK_SRC_SEL要设置为0x01;由内部PMIC提供则为0x02。

###############################################################################

# System clock frequency selection configuration

#define CLK_FREQ_13MHZ 1

#define CLK_FREQ_19_2MHZ 2

#define CLK_FREQ_24MHZ 3

#define CLK_FREQ_26MHZ 4

#define CLK_FREQ_38_4MHZ 5

#define CLK_FREQ_52MHZ 6

NXP_SYS_CLK_FREQ_SEL=0x02

在clock来源是PMIC的状况下,需依照硬体状况设置对应的频率。

- platform相关的设定

不同平台会有不同之设定,请务必依照平台规则进行整合。

- compile code

将文件提到之所有内容进行整合后,确认是否能编译image成功;如有error再依照message进行修改,一般error都是与平台相关设定整合有遗漏。

后续将编译完成的image进行烧录,确认NFC是否能正常enable/disable;如有遇到问题可先自行确认log状况,后续再与NFC vendor进行讨论。

参考来源