1.氮化镓GaN按照制造工艺,可以分为常开的耗尽型(D-mode)和常关的增强型(E-mode)两种类型, ST 氮化镓GaN 是E-mode (P-GaN) 工艺,以下的讨论都基于P-GaN 。

在电源系统中,对于所有的功率器件,选择正确的栅极驱动电路及进行合理设计,是实现电源系统最佳性能和增强稳定性的必要条件。但是对于GaN ,驱动的设计有些棘手,因为一些参数对GaN更为关键。

为保证可靠性和高性能,Layout布局、驱动IC,正确的外部元件等是需要考虑的关键问题,下图是GaN驱动电路的影响因素。

相对于 SI-MOS , VGS关断电压、VGS最大额定电压并不重要,但是对于E-mode (P-GaN) 却是重要参数,因此,驱动设计也更复杂,主要问题如下:

- Vgs(th) 阈值,如ST--SGT65R65AL ,Vth type 为8V,比SI-MOS 小很多,对栅极驱动因寄生参数引起的震荡更加敏感。

- Vgs 最大值,如ST--SGT65R65AL ,仅为7V,要求栅极驱动信号尽可能的干净,避免尖峰电压。

- dv/dt和di/dt约束:由于GaN HEMT是非常快的器件,高的dv/dt和di/dt会严重影响器件的开关行为。

- Layout注意事项:基础前面的陈述(栅极电压和快速开关),布局优化是GaN器件的基本步骤。

2. 在接下来的叙述中,我们将从以下几个方面进行分析:

- VGS最大值。

- 寄生电感、PCB布局和驱动电路位置。

- 高dv/dt和异常导通,可从两个方向考虑:栅极电阻选择,负电压关断。

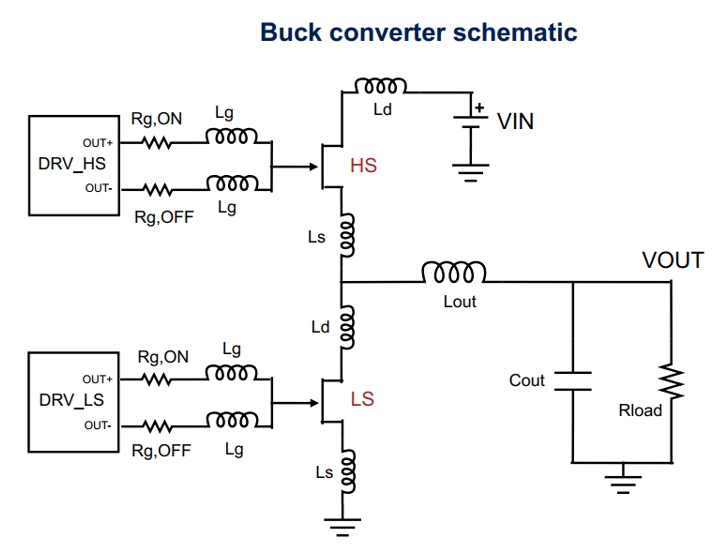

为了更好的理解GaN 的驱动电路设计,下面以Buck电路为例讨论,半桥拓扑可类似参考。

- 输入电压:400V

- 输出电压:200V

- 输出电流:10A

- 工作频率:300K

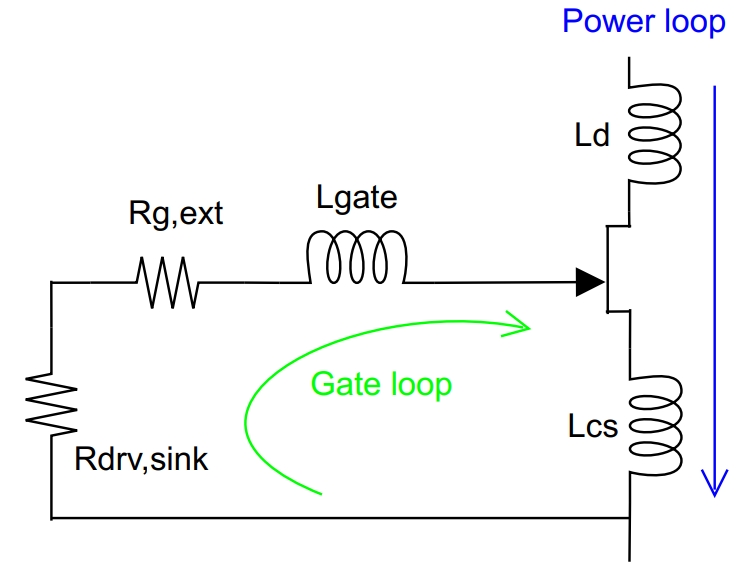

电路图如下,其中 Ls是源极寄生电感,Ld是漏极寄生电感,而Lg是栅极寄生电感。

2.1, VGS最大值

对于E-mode (P-GaN) GaN-MOS,最大允许栅极到源极电压(VGS-max)通常为5V或6V,但器件需要4到5V才能完全导通,从而导致非常窄的裕度 。

阈值电压VGS(th)非常低(从1到2V),当其用于高dV/dt应用时,对干扰更加敏感。

因此,GaN HEMT的栅极驱动设计相当尴尬。栅极-源极驱动信号必须非常干净,不能有过压尖峰和震荡。

以上要求的实现方法:

(a) 使用非常稳定的电源,比如LDO。

(b) 必须避免米勒效应和栅极杂散噪声。优化设计以降低栅极电感(Lg):驱动必须尽可能靠近GaN器件(如下图)

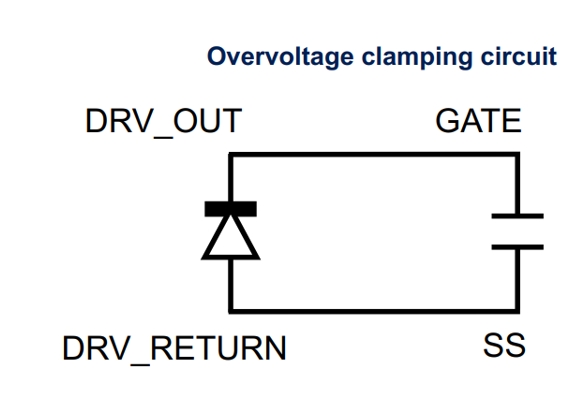

(c) 使用简单的过电压箝位电路(齐纳二极管和陶瓷电容)有助于减少潜在的尖峰电压(下图)

2.2, 寄生电感、Layout和驱动器位置

由于 GaN 器件能够非常快速地进行开关,因此与封装相关 的寄生效应非常重要。在某些情况下,它们会严重限制其性能。

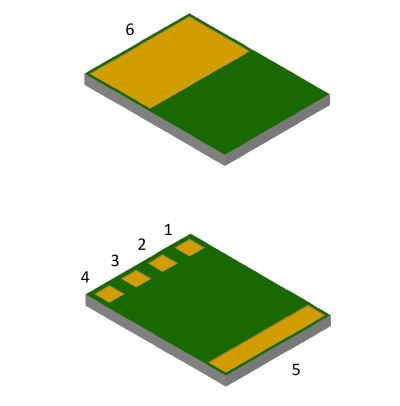

ST PowerGaN 封装具有非常低的寄生电感,优异的热性能。

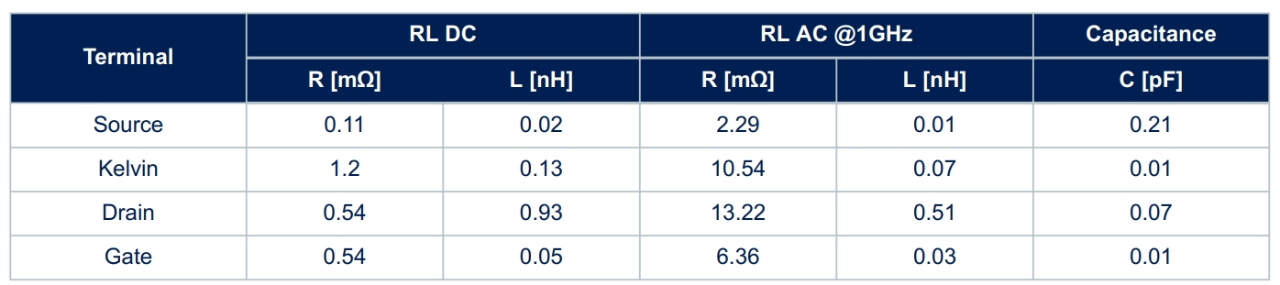

RLC寄生参数分布:

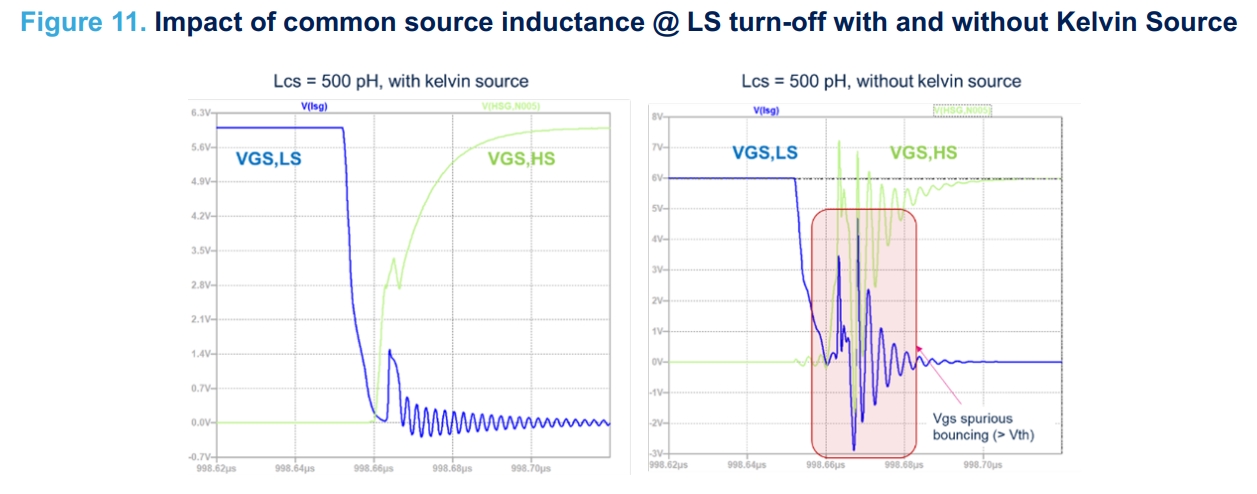

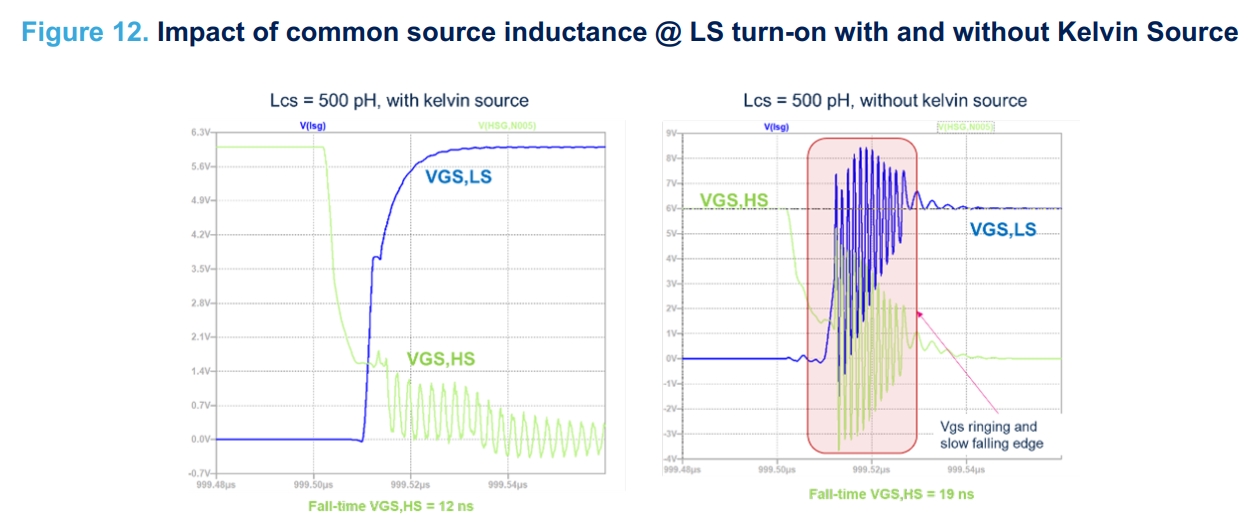

在所有寄生元件中,共源电感 (CSI,Lcs) 最为重要,因为它会影响电气性能。总体 CSI 是封装内部的源电感和封装本身的引线电感之和。在漏源极电路中存在高 di/dt 的情况下,CSI 有可能在漏源电压和栅源电压之间产生振铃,从而导致损耗增加和开关错误。在 E-mode (P-GaN) 器件中,由于安全裕度有限,VGS 中的振铃甚至可能导致栅极击穿。

也就是说,为了最大限度地减少寄生电感, SMD无引脚封装是性能良好易于使用的选择。

另一种解决方案是提供开尔文源极引脚,以从栅极环路去除CSI。虽然这可以解决误开关问题,但漏极到源极振铃仍然存在。

如上图所示,寄生电感可能影响GaN开关行为,特别是:

(A) Lcs(共源电感)在驱动回路和功率回路之间存在;它两端的高di/dt会产生压降,影响导通和关断时间,并导致不必要的振铃。Kelvin引脚对于改善开关行为和清除栅极源极信号中不期望的振铃非常有用

(下图):

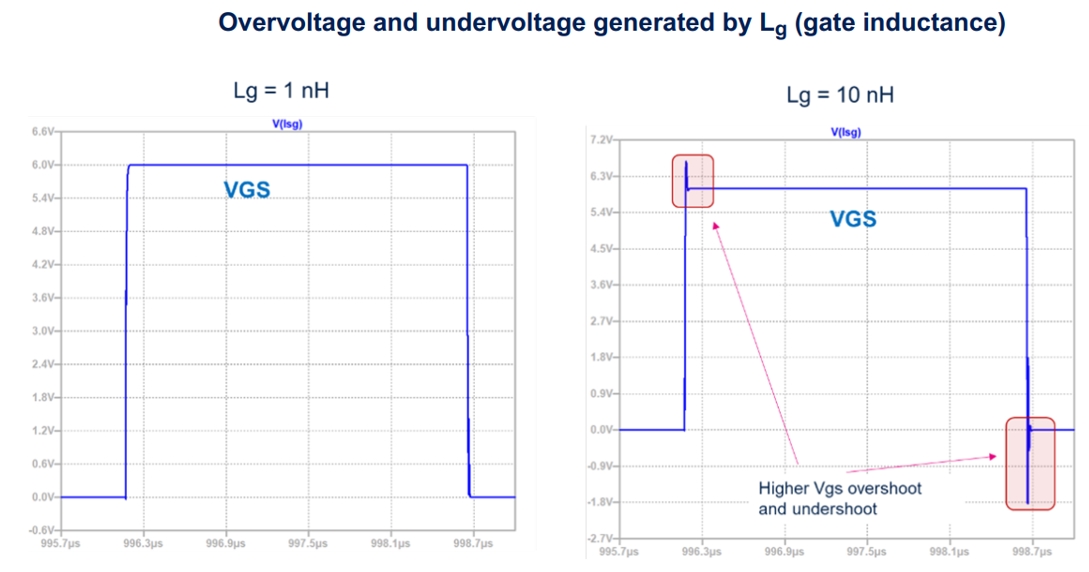

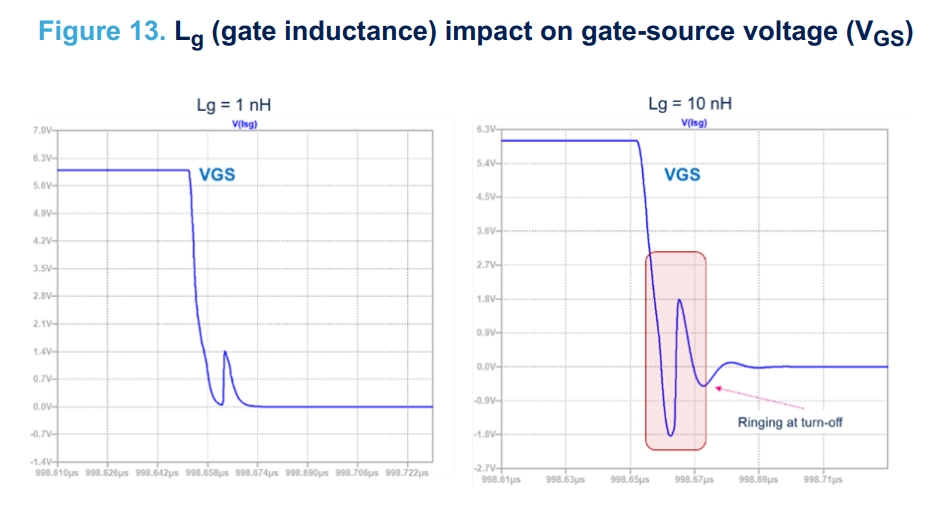

(B) L g 影响栅极-源极信号,增加杂散振铃(下图), 了最大限度地减少寄生电感,通常的做法是,把驱动器、栅极电阻器和GaN尽可能靠近。

2.2, 高dV/dt和杂散导通

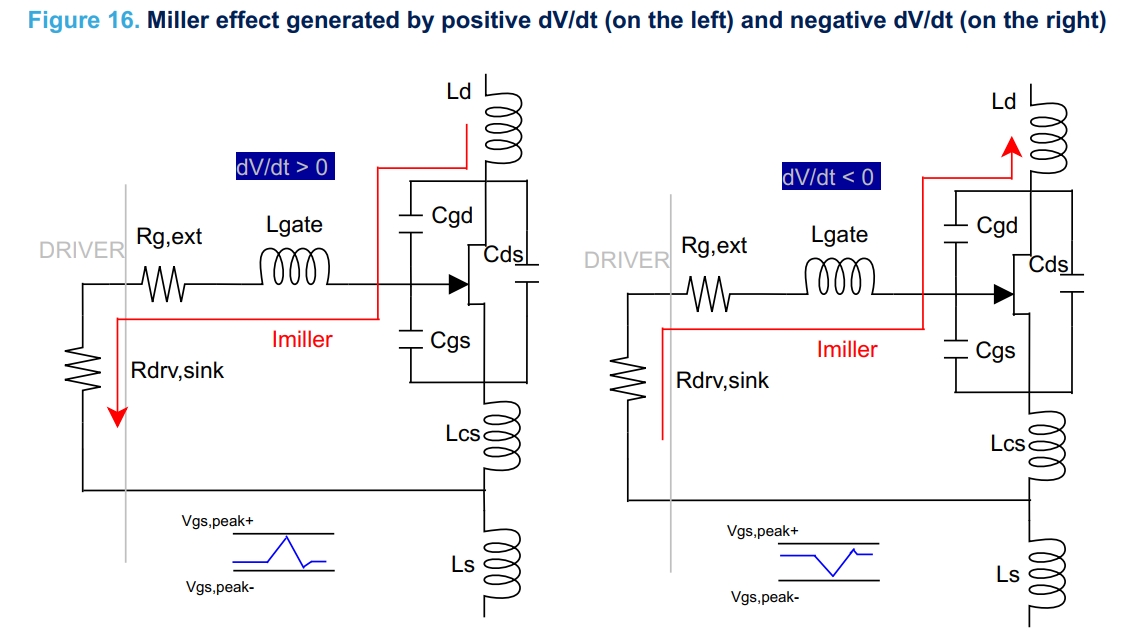

驱动GaN高速开关的另一个制约因素是dV/dt效应。功率开关器件的电压转换斜率(dv/dt)由各种寄生电容和栅极驱动电路之阻抗引起,由米勒电容的充电和放电速率决定。高dv/dt在高电压输入的桥式拓扑中常见,并且这种现象由于氮化镓的高速开关性能而加剧。

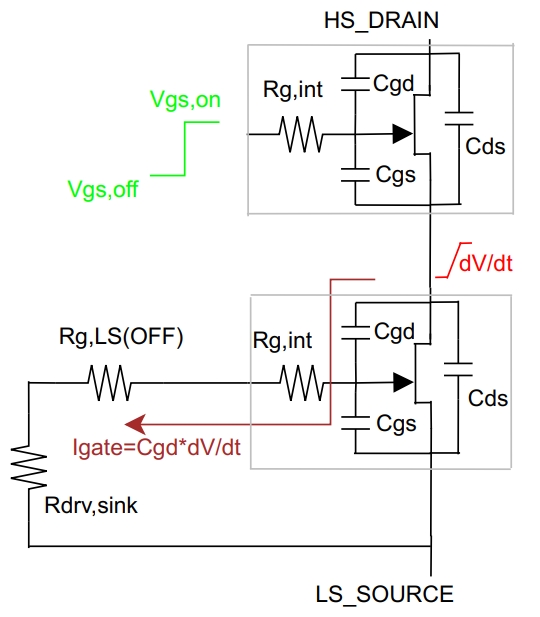

在桥式拓扑中,当上管导通时,下管的米勒电容会向栅极注入电流。如果注入到栅极的电流足够大以使栅极电压高于器件阈值电压,则可以观察到寄生导通,从而导致较低的效率甚至损坏器件。

如果在下管两端出现正dVDS/dt,则在栅极处看到的杂散电压尖峰可以估算如下:

由于在桥拓扑的中点上施加正或负dV/dt,栅极和源极之间的杂散电压可能出现在上升和下降两个瞬态边沿。

米勒效应可以通过减小栅极环路电感、选择具有低漏电阻的驱动器以及向栅极引脚施加负偏压来优化,目标是当通过米勒电容的电流尖峰发生时将栅极电压保持在期望阈值以下。

提高dv/dt耐用性可使用不同策略:

- 驱动电阻的选择 :为了实现GaN HEMT的最佳性能,必须进行独立的开关控制,从而实现dV/dt优化和开关损耗最小化。

- 主动米勒钳位

- 负压关断

- 选择合适的驱动器

注: 本文原始文件来自ST应用手册 《AN5583-emode-gan-technology-tips-for-best-driving-stmicroelectronics 》,可在ST官网下载。

评论