一、 概述

本文主要介绍 SemiDrive E3 SSDK boot_core 示例,示例主要实现的功能为 sf core boot 其他 core。使用的为 debug 模式调试,所有核的代码均使用 IAR 的 download and debug 功能下载在 ram 中运行。

硬件设备:E3640 GATEWAY 开发板

软件包:SSDK PTG3.0

二、 代码下载及 demo 介绍

使用 SemiDrive support 系统上的 SSDK Builder,选择型号 E3640 和示例 app_demo/boot_core 生成参考代码。

首先将拨码开关拨至 1110 模式,上电后进入调试模式。

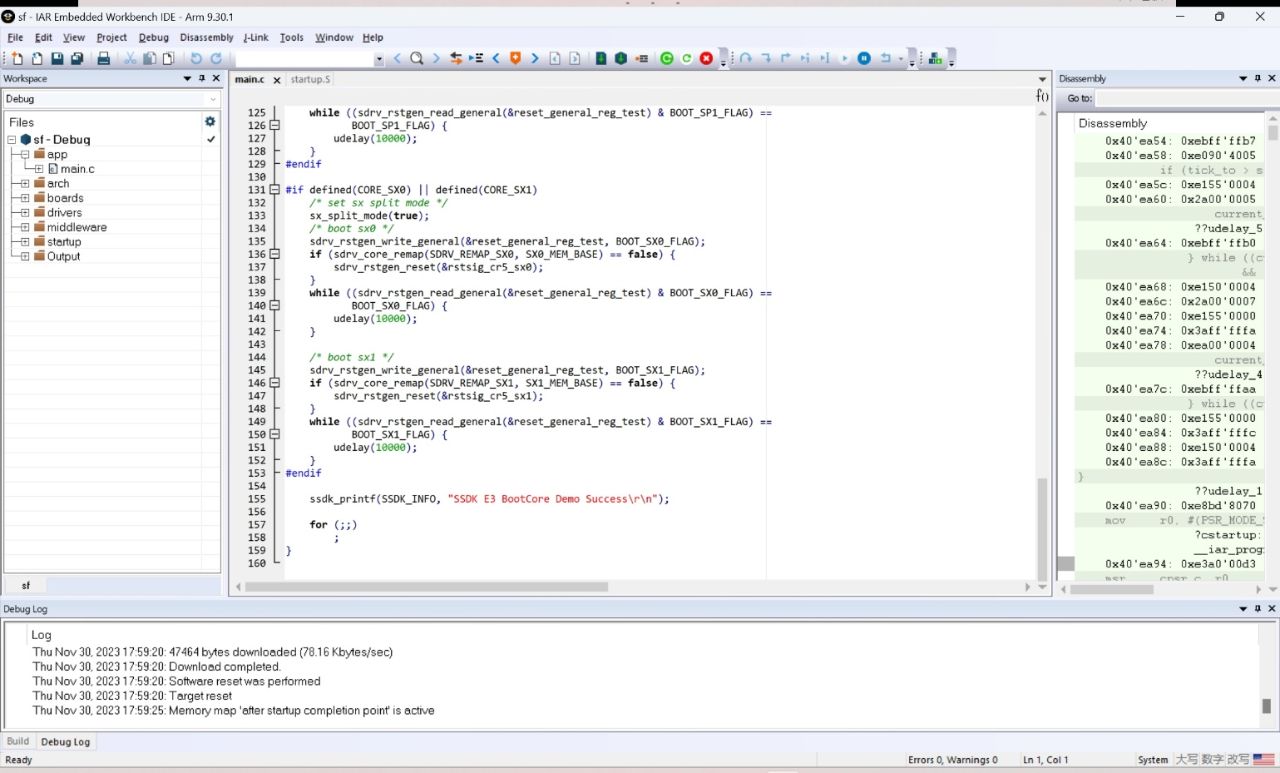

打开 sf 文件夹下的 IAR 工程,编译后点击 download and debug,下载镜像至 E3 gateway 开发板,并点击 go 启动调试,此时串口中会打印 log “Welcome to E3 BootCore Demo, this is core SF”。

图 2.1 SF 核程序运行界面

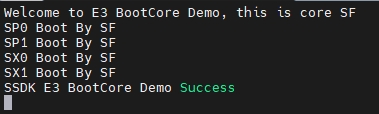

然后依次打开 SP0、SP1、SX0 和 SX1 的 IAR 工程,编译后点击 download and debug,下载镜像至 E3 gateway 开发板,并点击 go 启动调试,此时串口会分别打印 log,“SP0 Boot By SF”、“SP1 Boot By SF”、“SX0 Boot By SF” 和 “SX1 Boot By SF”,最后会打印 log “SSDK E3 BootCore Demo Success” 表示示例成功运行。

图 2.2 运行成功 log

三、 代码解析

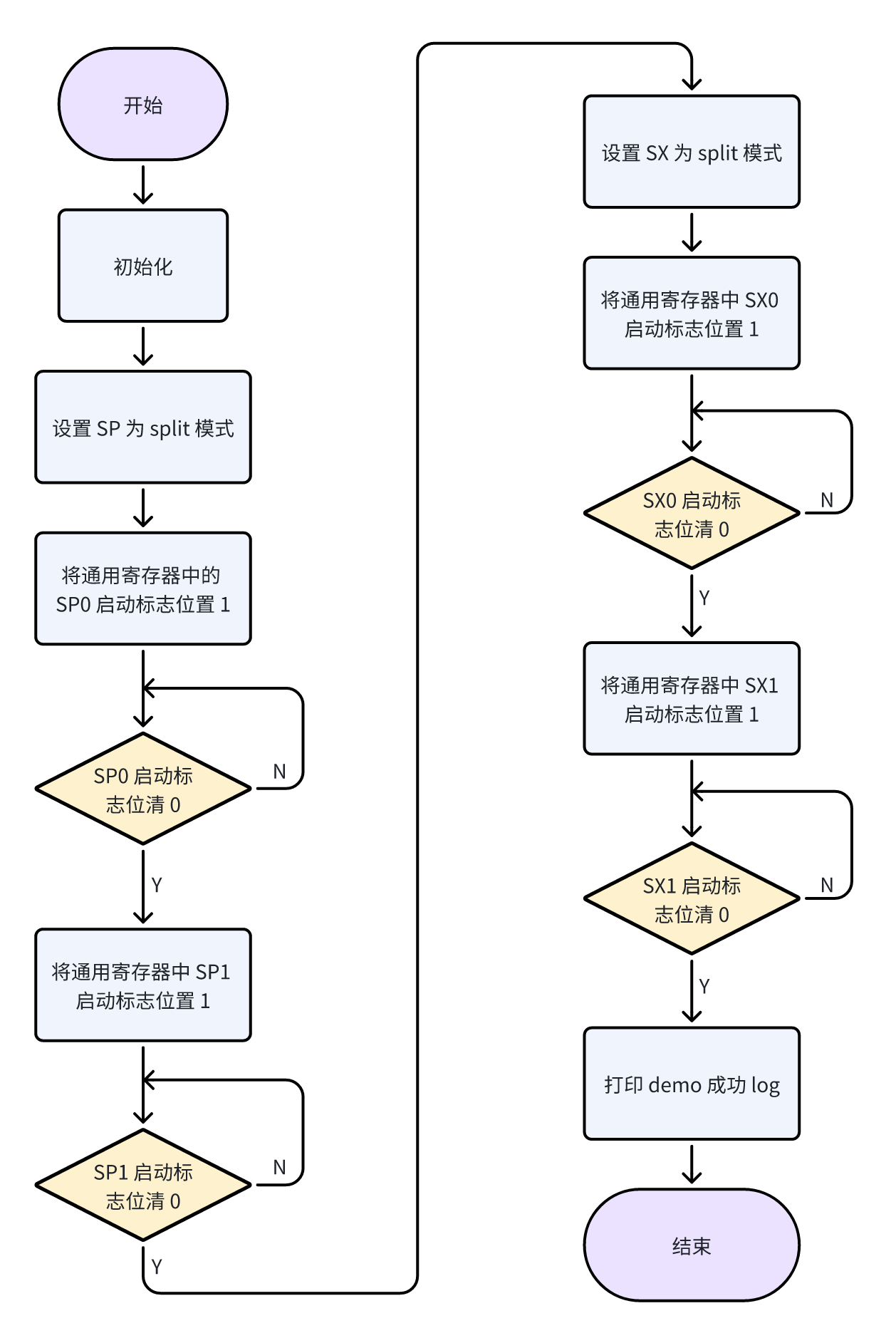

3.1 SF 程序流程

首先进行初始化,复位 VIC1 模块、初始化 clock 时钟、VIC1 中断、Pinmux 配置和串口号等,并打印欢迎信息。

使用 sp_split_mode(true); 将 SP 设置为 split 模式,SP0 和 SP1 作为两个核使用。

使用 sdrv_rstgen_write_general(&reset_general_reg_test, BOOT_SP0_FLAG); 将通用寄存器中 SP0 标志位即第 0 位,设置为 1。然后使用 sdrv_core_remap(SDRV_REMAP_SP0, SP0_MEM_BASE) 跳转到 SP0 核的地址,如果未跳转成功,则 reset SP0 core。成功跳转后,进入 while 循环,读取通用寄存器的第 0 位,判断是否为 0 。因为 SP0 核的程序在成功启动后,会将通用寄存器的第 0 位清 0。

SP0 成功启动跳出 while 循环后,下一步 boot SP1,与 SP0 的步骤一致,sdrv_rstgen_write_general(); 将通用寄存器的第 1 位设置为 1。然后使用 sdrv_core_remap() 跳转到 SP1 核的地址,未成功则 reset SP1 core。成功跳转后,进入 while 循环,读取通用寄存器的第 1 位,判断是否为 0。在 SP1 核的程序成功启动后,SP1 程序会将通用寄存器的第 1 位清 0,从而 SF 核程序跳出 while 循环。

SX0 和 SX1 的部分与 SP0 和 SP1 的部分一致,等到所有的核启动后,则打印 demo 运行成功 log。

SF 核的代码流程图如下:

图 3.1 SF core 程序流程图

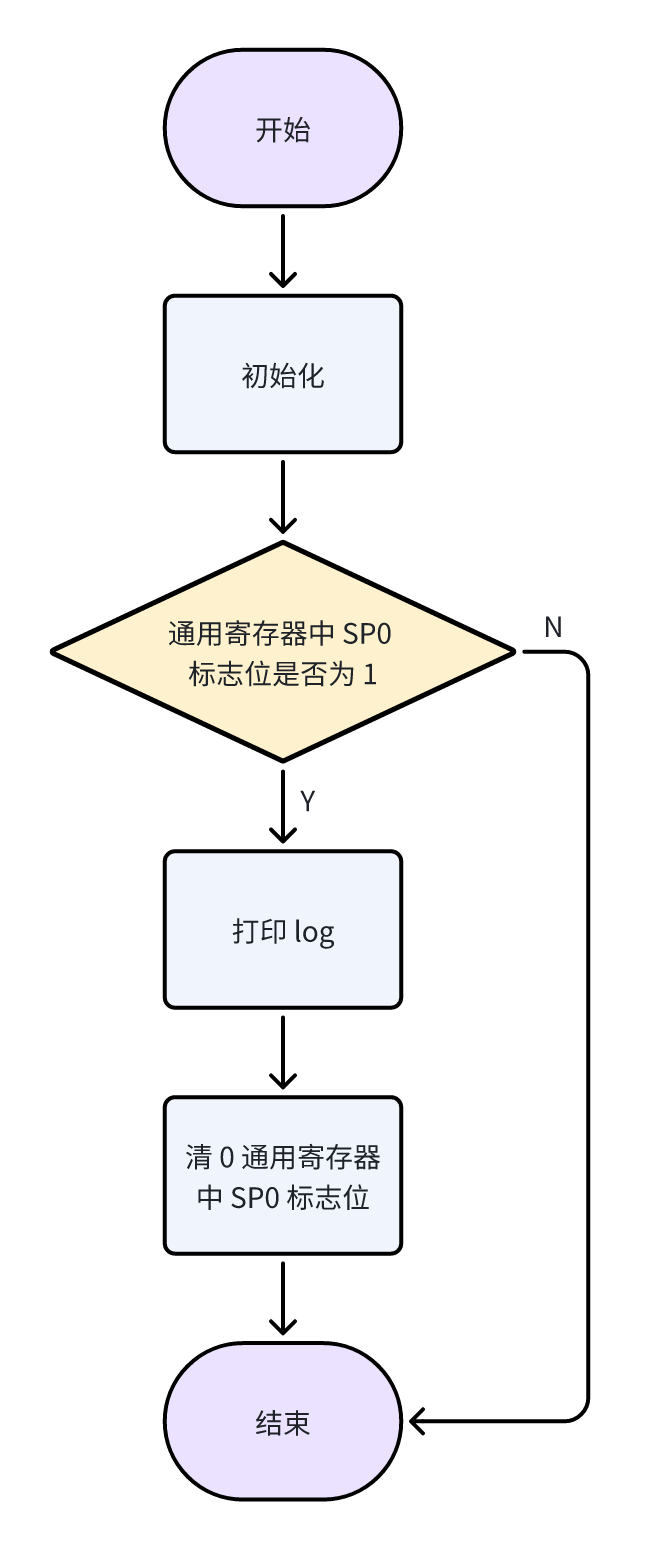

3.2 SP0/SP1/SX0/SX1 程序流程

SP0、SP1、SX0 和 SX1 的代码逻辑一致,以 SP0 core 代码为例进行解析。

首先进行初始化,复位 VIC2、初始化 VIC2 中断和串口。然后通过读取通用寄存器中 SP0 标志位,即第 0 位是否为 1,来判断是否是由 SF 核启动的 SP0 程序,如果是则打印 “SP0 Boot By SF”的 log,然后再将通用寄存器 第 0 位设置为 0,之后进去 for 死循环。

SX0 核的代码流程图如下:

图 3.2 SX0 核代码流程图

四、 拓展分析

4.1 lock step 和 split

示例中配置了 sp_split_mode() 和 sx_split_mode() 两个 API,用于配置 SP 和 SX 是作为 lock_step 还是 split 使用,作为锁步核时,程序只需要下载一份。

4.2 通用寄存器

参考 TRM 的13.4 Reset Generator 章节,AP 域和 Safety 域均有 8 个 32 位的 通用寄存器,寄存器名称为 GENERAL_REGn,offset 为 0x2004。

示例中使用的是 id 为 2 的通用寄存器,根据 boot_core.h 中的宏定义,可以看到将 bit0 作为 SP0 的标志位,bit1 作为 SP1 的标志位,bit2 作为 SX0 的标志位,bit3 作为 SX1 的标志位。

通用寄存器在 global reset 和看门狗复位的情况下都不会丢失。所以可以作为 OTA 升级的标志位,在 APP 中置位其中一个 bit,复位后在 bootloader 中判断是否升级。

4.3 Memory Map

参考 TRM 的 4.1 Memory Map 章节,E3640 的 IRAM 地址为 0x400000 至 0x7FFFFF。

工程中分配的SF地址范围为 0x404000 至 0x5FFFFF,SX0 的地址范围为 0x600000 至 0x67FFFF,SX1 的地址范围为 0x680000 至 0x6FFFFF,SP0 的地址范围为 0x700000 至 0x77FFFF,SP1 的地址范围为 0x780000 至 0x7FFFFF。

SF 的起始地址为 0x404000 的原因,是因为需要预留 16K 字节大小的空间给 ROM 程序使用。

每个核的地址范围可以通过修改 IAR 工程的 link 脚本(.icf) 文件内的定义。默认的配置仅为参考配置,可以根据实际使用需求来修改,不同的核地址空间不重复即可。

五、 参考文档

- 《SemiDrive_E3_SSDK_User_Guide》

- 《E3400_E3600_MCU_TRM》

- 《AppNote_E3_Boot_and_OTA》

如有更多需求,欢迎联系大联大世平集团 ATU 部门:atu.sh@wpi-group.com 作者:Eason Wang / 王寅森

更多资讯,请扫码关注我们!

评论