-

本方案采用FPGA作为驱动屏幕的装置,有下列几项优点:

- 适合各种不同TFT-LCD的界面规格,诸如 并口 RGB 888/ BT656/ BT709 /LVDS /MIPI DSI 等市场规格上常用的界面

- 支持不同分辨率的屏,可以从320x240 ,640x480 , 800x600 , 1280x720, 1024x 800, 1920x1080 ,640x480 , 800x600 , 1280x720, 1024x 800, 1920x1080 等

- 支持不同祯率的要求,如 30祯/60/60祯 等等

- 支持字裤与图形编码,在许多应用中,可以自由定义英数字及中文繁体简体和特殊符号等,可以显示在屏幕上,并给予不同颜色与底图的算法,当需要文字与底图叠加的功能要求也能轻易做到

- 方案简单,由于采用逻辑编码,不容易死机,,不会像MCU一样容易跑飞而当机或花屏

- 升级容易,只要在FPGA的逻辑容量范围内,可以随意改变逻辑编排,方便增加功能与提升性能,不需要额外的电路辅助

-

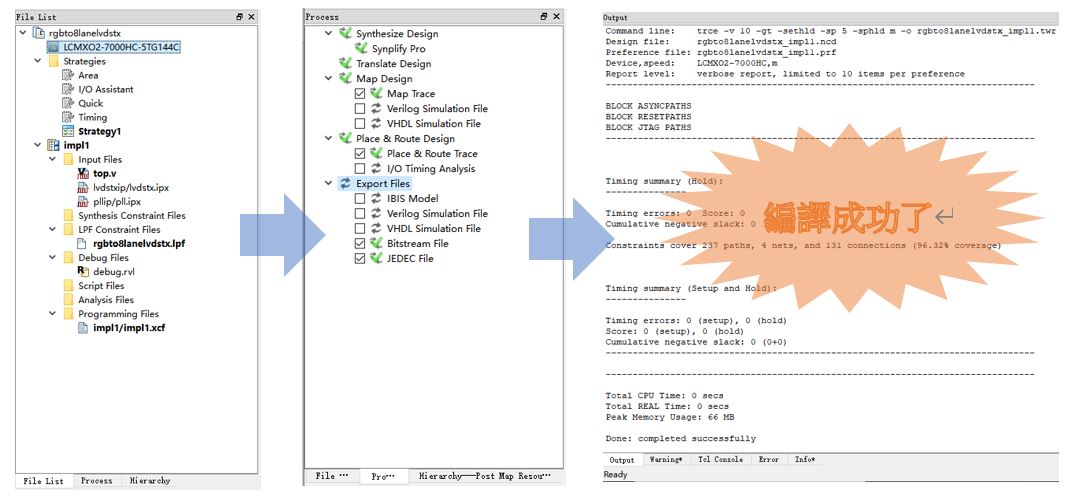

简单易用的逻辑编成软体综合布局布线工具,以下将以简单的步骤与方法带领各位入门

- 下列介绍如何编写RTL代码点亮TFT LCD显示屏幕

- 材料:

- FPGA Lattice FPGA XO2

- TFT LCD 800X480

- USB 下载线

- Verilog 编译工具

- TFT LCD 屏幕介绍:

- 先选用适合分辨率的屏:

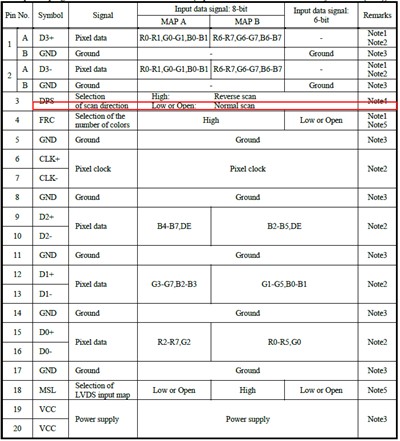

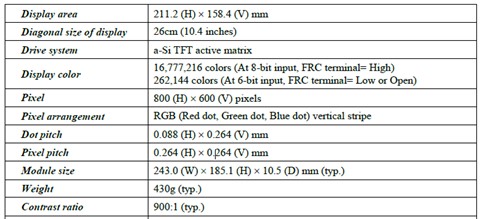

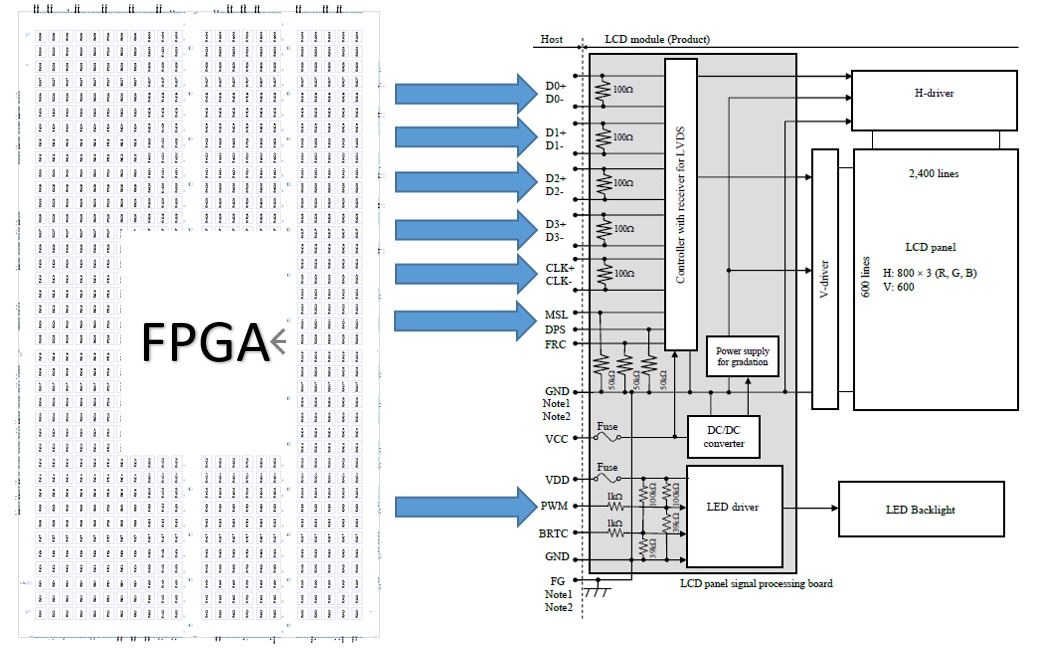

- 下方所示的屏幕规格为: 800 X 600 点RGB 格式

- 色彩深度为 16,777,216色深(24bit) 或 262,144色深(18 bit)

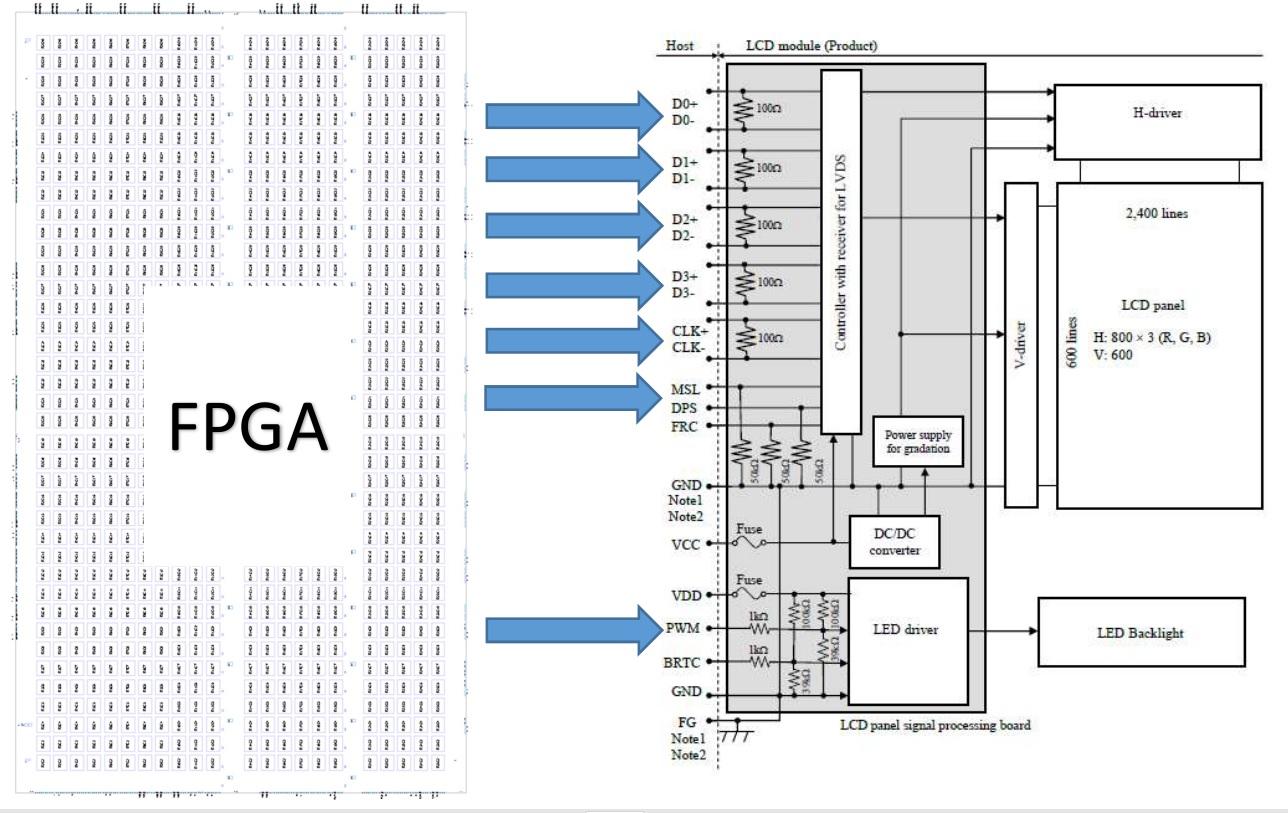

- 连接线的接法:LVDS脚位说明:

- 把FPGA LVDS Pin 接到TFT LCD LVDS Pin(D0+/D0-/ D1+/D1-/ D2+/D2-/ D3+/D3-/CLK+/CLK-)

- 先选用适合分辨率的屏:

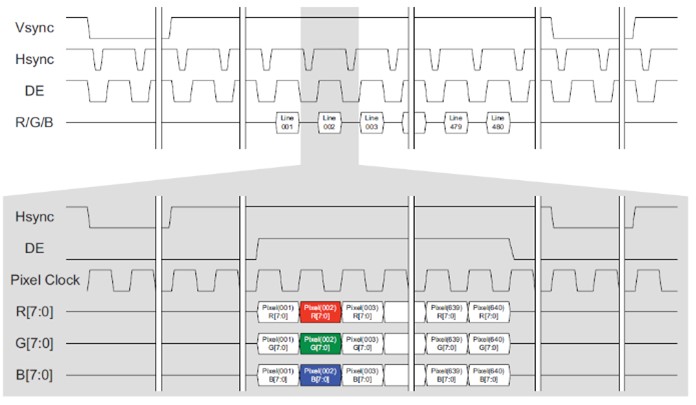

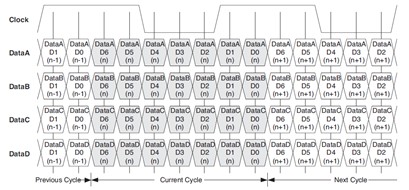

- ideo 的LVDS内容说明:

- 把FPGA I/O Pin 接到TFT LCD LED PWM Pin

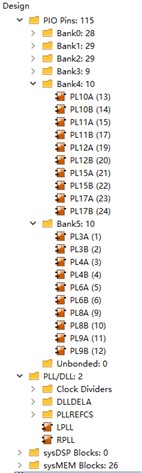

- FPGA XO2器件介绍:

- 器件料号: MachXO2:LCMXO2-7000HE-TQFP144

- Bank4 LVDS I/O:

- 使用 PLA10A/LVDS_D0+

- 使用 PLA10B/LVDS_D0-

- 使用 PLA11A/LVDS_D1+

- 使用 PLA11B/LVDS_D1-

- 使用 PLA12A/LVDS_D2+

- 使用 PLA12B/LVDS_D2-

- 使用 PLA15A/LVDS_D3+

- 使用 PLA15B/LVDS_D3-

- 使用 PLA10A/LVDS_clk+

- 使用 PLA17B/LVDS_clk-

- 使用 PLA3A /PWM

- 使用 PLA3B /MSL

- 使用 PLA4A /DPS

- 使用 PLA4B /FRC

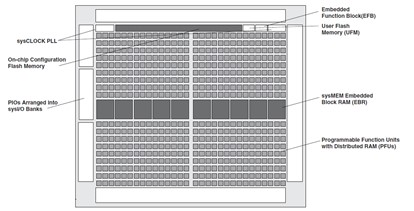

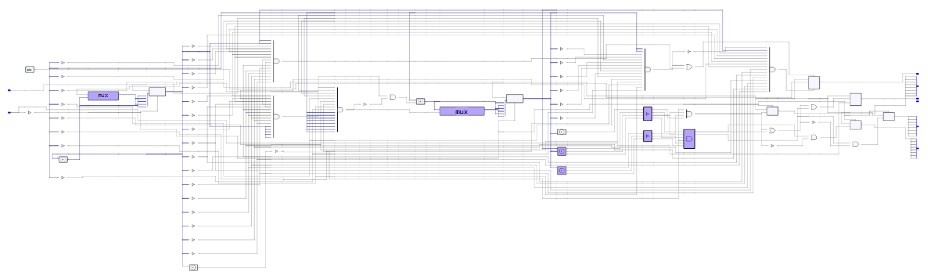

- FPGA内的资源:

- PLL:

- On chip OSC:

- EBR:

- PFU:

- LVDS I/O:

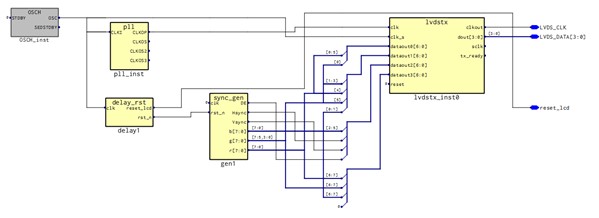

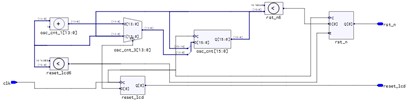

- 规划FPGA逻辑模块: (下图为连接好的各模块图)

- 搭建 top module:

-

module top (

output wire reset_lcd,

//lvds pin

output wire LVDS_CLK,

output wire [3:0] LVDS_DATA );

这里调用有用到的各IP模块

. .(此处请自由发挥)

.

endmodule

-

- 搭建WPI 提供的IP:

-

delay_rst delay1(

.clk(osc_38),

.rst_n(rst_n),

.reset_lcd(reset_lcd)

);

-

sync_gen gen1(

.r(r),

.g(g),

.b(b),

.DE(DE),

.Vsync(Vsync),

.Hsync(Hsync),

.clk(clk),

.rst_n(rst_n)

)

-

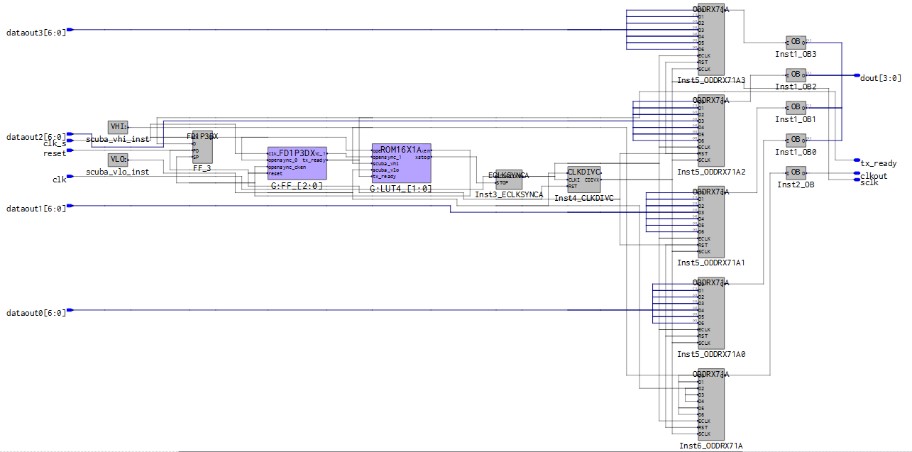

lvdstx lvdstx_inst0 (

.clk_s(osc_38 ),

.reset(1'b0 ),

.clk(pll_166 ),

.dataout0(tx0_a ),

.dataout1(tx0_b ),

.dataout2(tx0_c ),

.dataout3(tx0_d ),

.sclk( ),

.tx_ready( ),

//lvds pin

.clkout(LVDS_CLK ),

.dout(LVDS_DATA )

);

- 搭建原厂 提供的IP:

-

defparam OSCH_inst.NOM_FREQ = "38";

OSCH OSCH_inst(

.STDBY(1'b0),

.OSC(osc_38),

.SEDSTDBY()

); //synthesis syn_black_box

-

pll pll_inst (

.CLKI(osc_38 ),

.CLKOP(pll_166 ),

.CLKOS(pll_47 ),

.CLKOS2(pll_spi ),

.CLKOS3(pll_100 )

);

-

-

-

- 使用综合布局布线工具:

-

- 下载烧录程序到FPGA板子:

- 恭喜你!现在就可以看到显示画面啰!!

如果你想要再进阶学习与使用本方案,赶快来连系我吧!

大联大控股世平集团

大联大商贸有限公司

FPGA 系统开发 研发总监 郑保夏 Jones Cheng

Office: 886-2-2788-5200台北

86-21-23099388深圳#37048

Mobile:

(TW) +886 -930801444 台湾

(CN) +86-15801597488 北京

(CN) +86-15000264113 上海

E.mail: jones.cheng@wpi-group.com

WPI Group 世 平 集 团 A Member of WPG Holdings 大联大控股

►场景应用图

►展示板照片

►方案方块图

►核心技术优势

采用FPGA来驱动显示屏TFT-LCD, 有着比MCU更高效能,及更高灵活度, 不论是 RGB888的并行接口或是LVDS的串型接口, 可以轻易定义封包内容,也能随意地编解码各家的显示屏, 对于不同分辨率和不同色深要求的应用场合,绝对是FPGA来做主控端再适合也不过了, 低的操作频率,不发烫,省电等等优势, 是你的方案首选

►方案规格

LVDS分辨率支持 1920x1080p 以内, 祯率可以30fps 或60fps 支持自定义协议包, 支持通用LVDS标准协议包