PA即英语Power Amplifier的缩写,在NXP的Smart PA中有集成DSP,因此对I2S的时钟要求比较高,如果出现时钟抖动比较大的话,可能会导致DSP挂掉或异常。

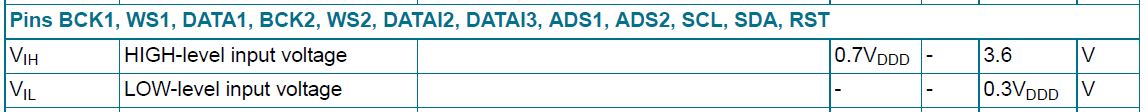

对I2S信号电平幅度的要求:

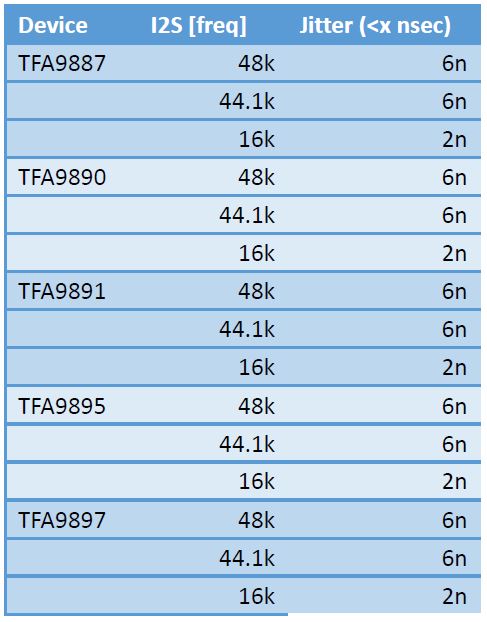

Smart PA芯片对I2S时钟Jitter(抖动)的要求:

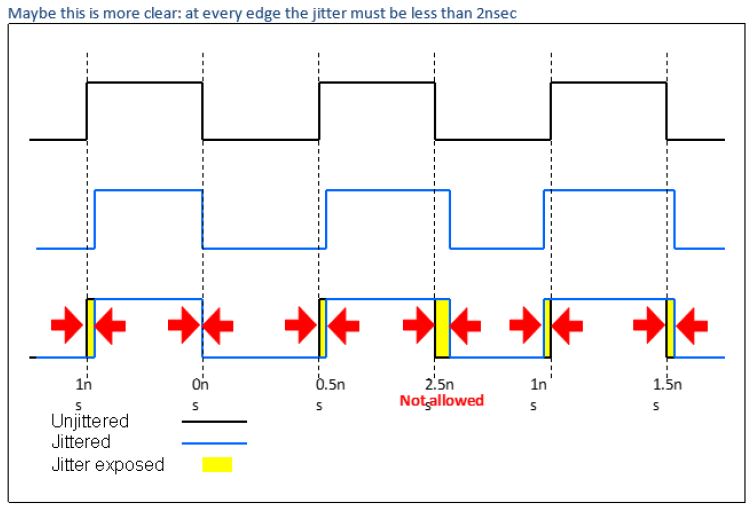

Jitter示例:

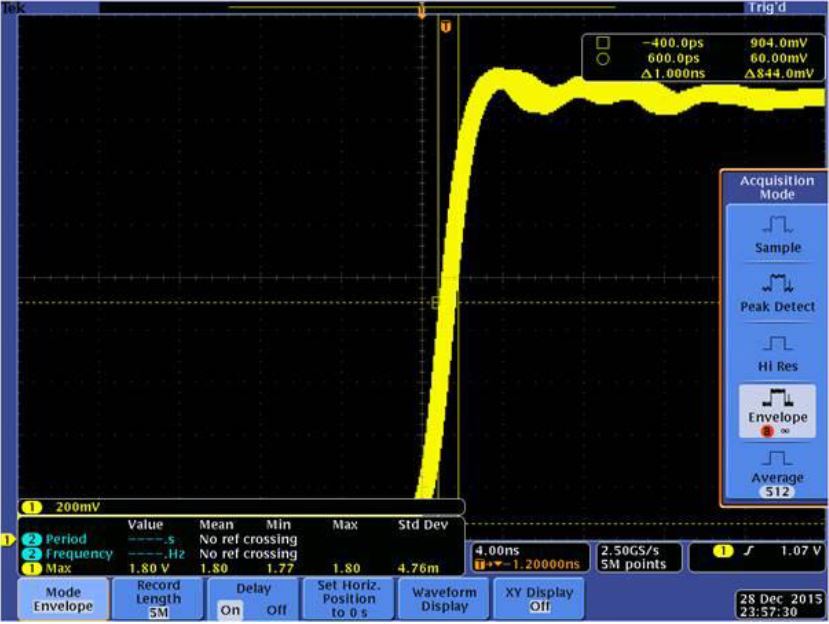

Jitter测量方法:

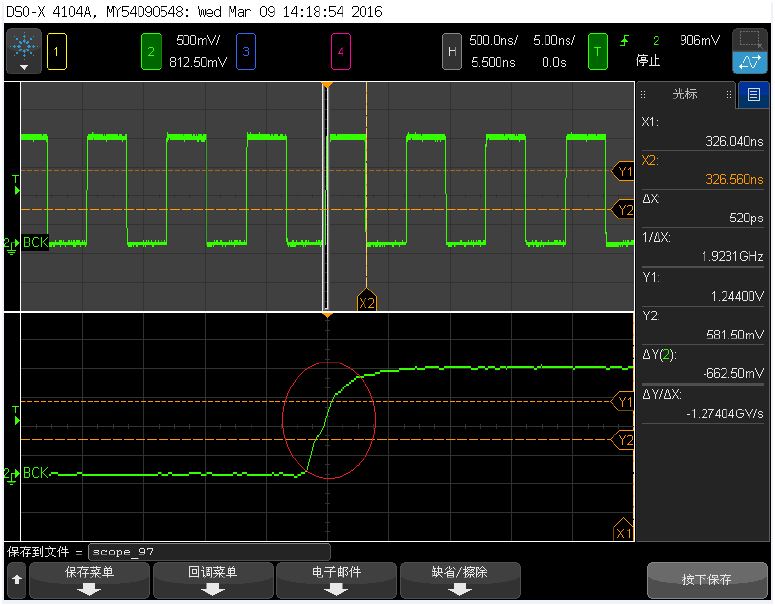

示波器设置,下降沿触发测试上升沿,使能Envelope. 利用采集模式,将此模式设置为Envelope模式,如下所示:

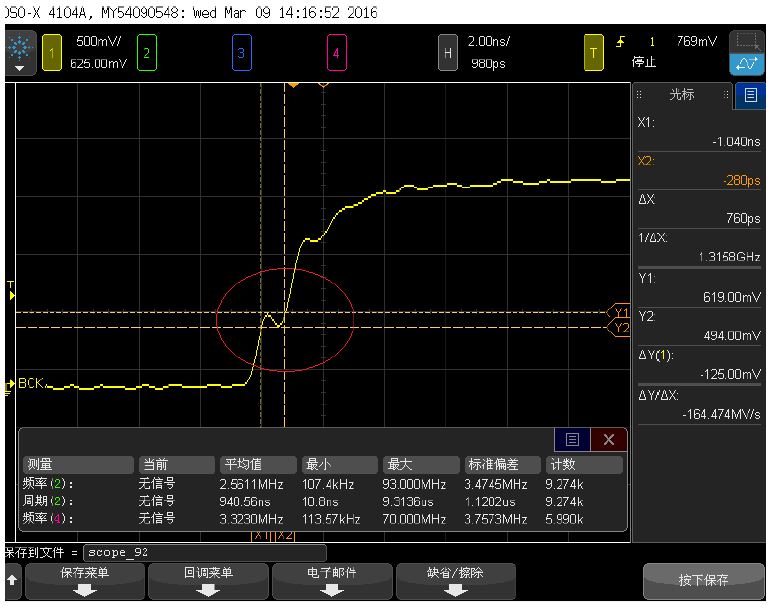

然后用光标可以测量上升沿和下降沿的距离厚度。最好一次只测量一个,因为您希望尽可能地放大边缘以查看抖动。 另外,不同的探头测出来的结果还是不一样的,建议用Active FET Probe有源探头 (更少的电容)。

1、无源探头(结果没有下垂)

2、有源探针(结果凹陷)

这意味着信号应该稳定在0.3-0.7 VDDD之间,也就是0.54V - 1.26V之间(VDDD=1.8V)。 从上面的图片可以看出,在494到619 mV之间,这确实是一个问题,尤其是当它是一个时钟输入,如BCK时钟信号。 当它是一个时钟输入时,可以产生一个双时钟,而PLL可以跟随这个时钟,这会导致不需要的情况出现。 因此,应该对信号进行改进,以防止可能出现的问题,这些问题是信号完整性优化的一部分。