前面我们讲了很多基于 S32V234 平台的软件开发如何进行,有包括 BSP、ISP、APEX、GPU 等,但针对硬件好像一直忘了跟大家说,那么,接下来我们一起来看看大家爱不释手的 S32V234 的 DDR 是如何设计的。

一、原理图部分

1. NXP S32V234 DDR 控制器介绍

1.1 S32V234 包含两个 32bit DRAM 控制器,接口支持 LPDDR2 x16、 x32,DDR3/DDR3L x16、x32,控制器有如下特点:

① 每个 DDR 控制器最大容量可以支持 8Gbit;

② 每个控制器支持两个片选信号;

③ DDR3 模式 Burst Length 支持 8 位,LPDDR2 可以支持 4 位;

④ 支持最大运行时钟速率为 533MHz。

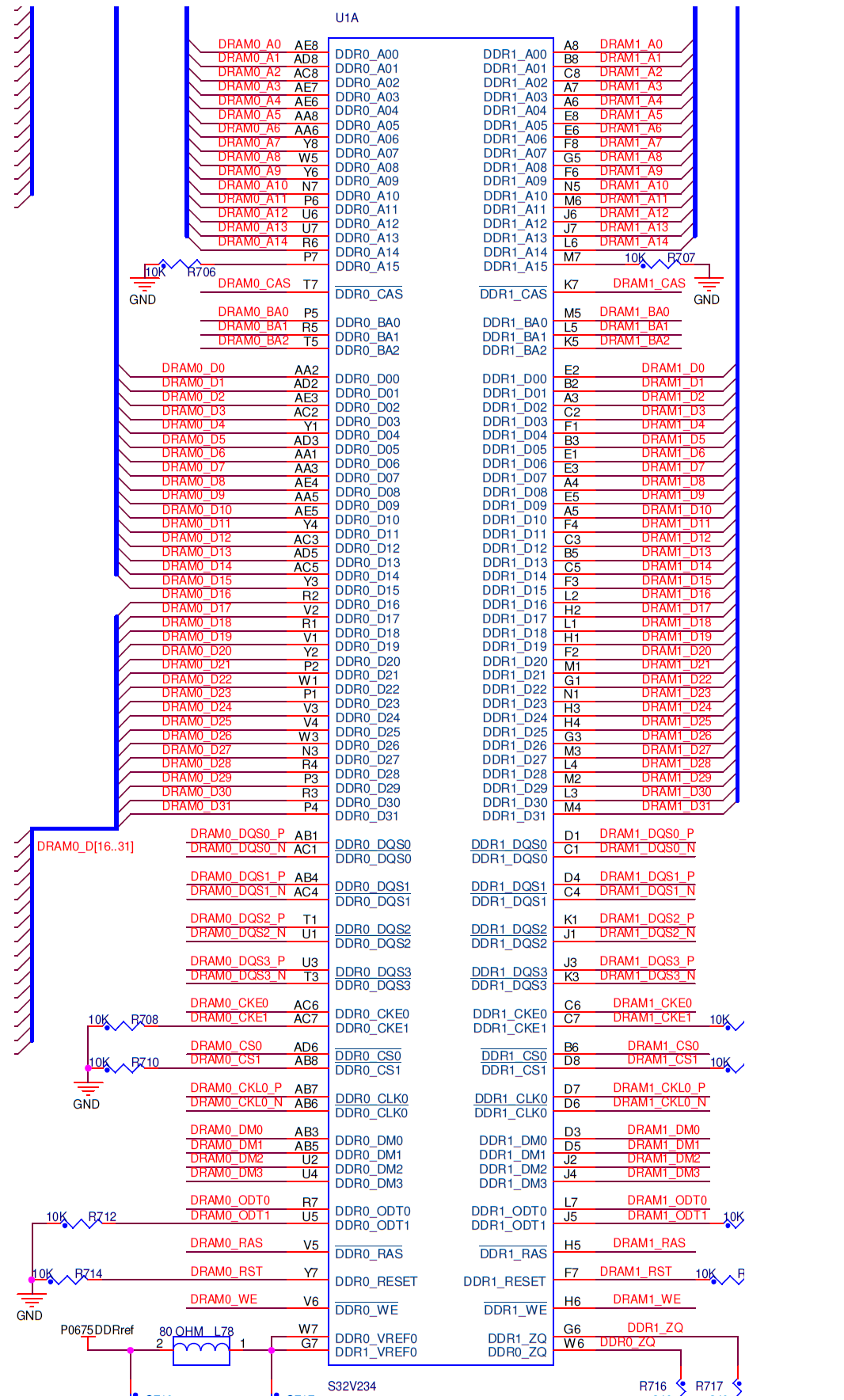

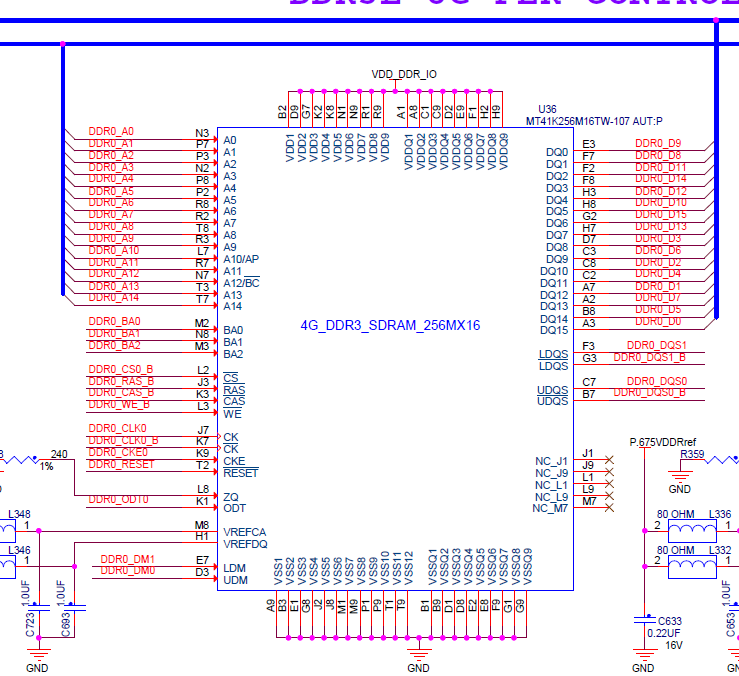

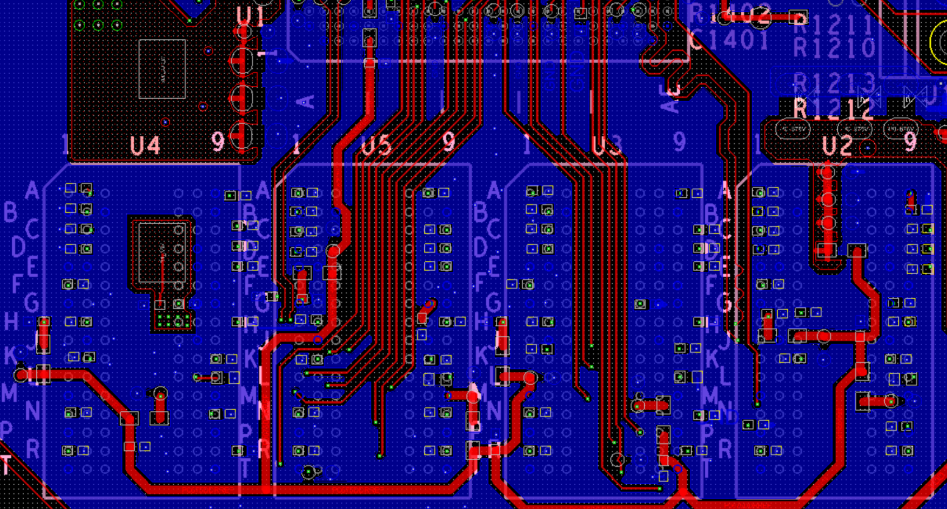

如下图 1.1 S32V234 DDR 控制器原理接线图所示:

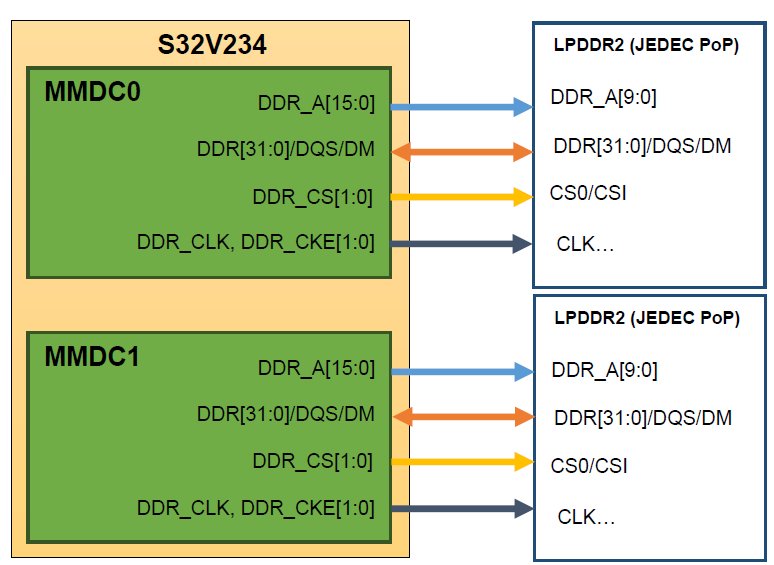

1.2 S32V234 的 SDRAM-LPDDR2 拓扑结构及相关原理图

如图 1.2(a) S32V234 SDRAM-LPDDR2 拓扑结构图

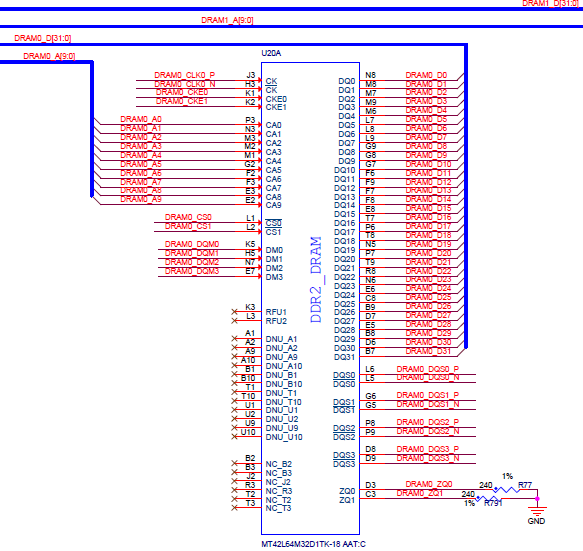

如下图 1.2(b) S32V234 LPDDR2 原理图

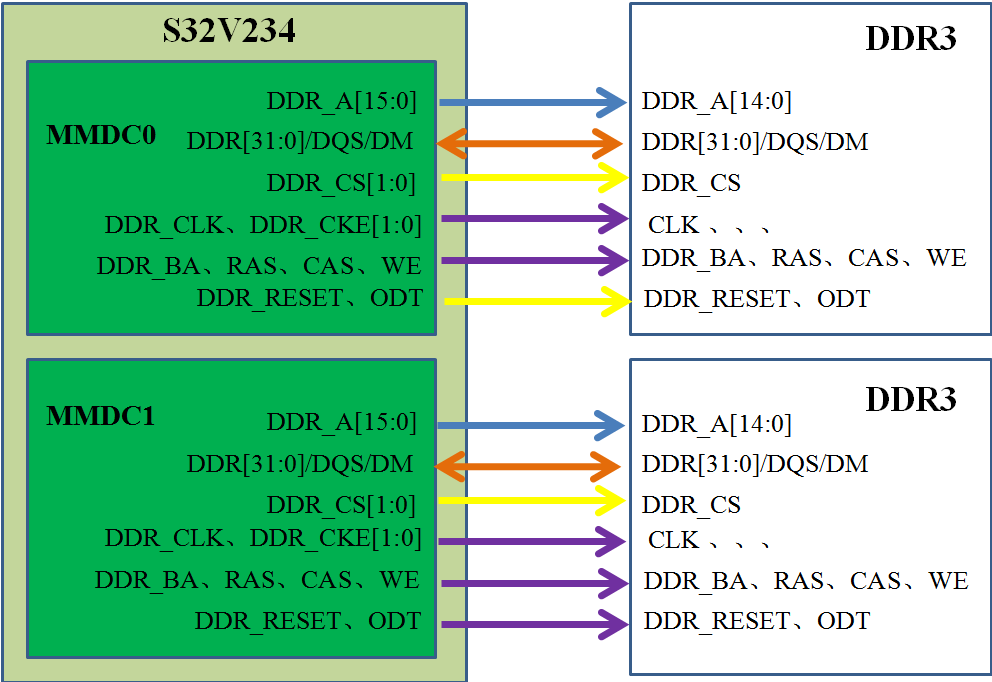

1.3 S32V234 的 SDRAM-DDR3 拓扑结构及相关原理图

图 1.3(a) S32V234 SDRAM-DDR3 拓扑结构图所示

如下图 1.3(b) S32V234 DDR3 原理图所示

2. DDR 电源部分

2.1 VDD_DDR_IO

如图 1.4 DDR IO 电源说明

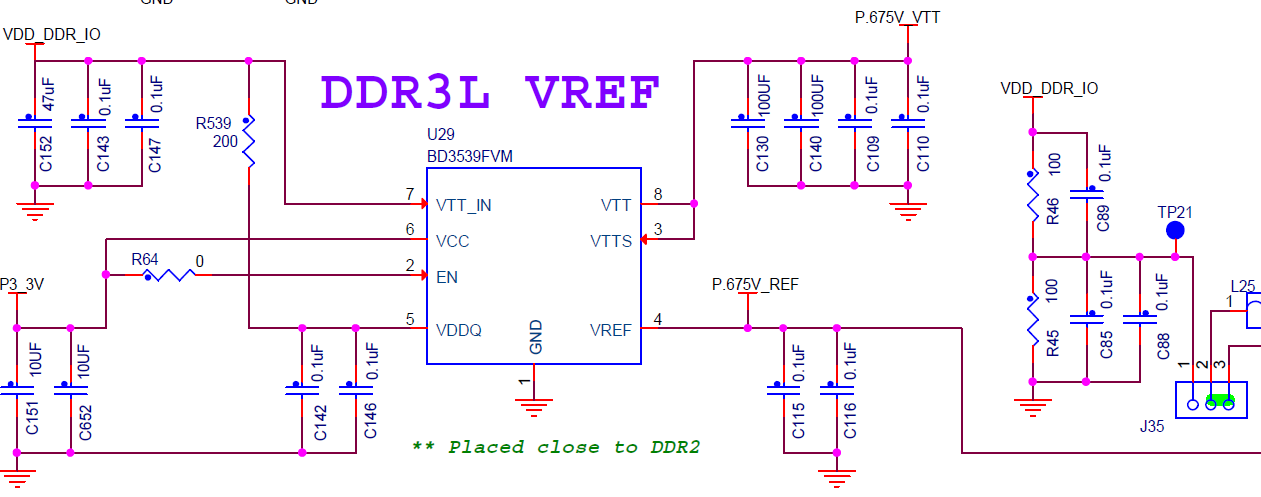

2.2 DDR0_VREF0/DDR1_VREF1

① DDR_VREF 电源是 DDR_IO 电源的一半,可以采用芯片单独供电或者电阻分压的方式提供,需要注意电压的精准度;

② 0.675_VTT 电压需要从专用芯片电路获得,不能和 DDR_VREF 共网络。

如下图 1.5 DDR VREF & VTT 电源电路

二、PCB Layout 部分

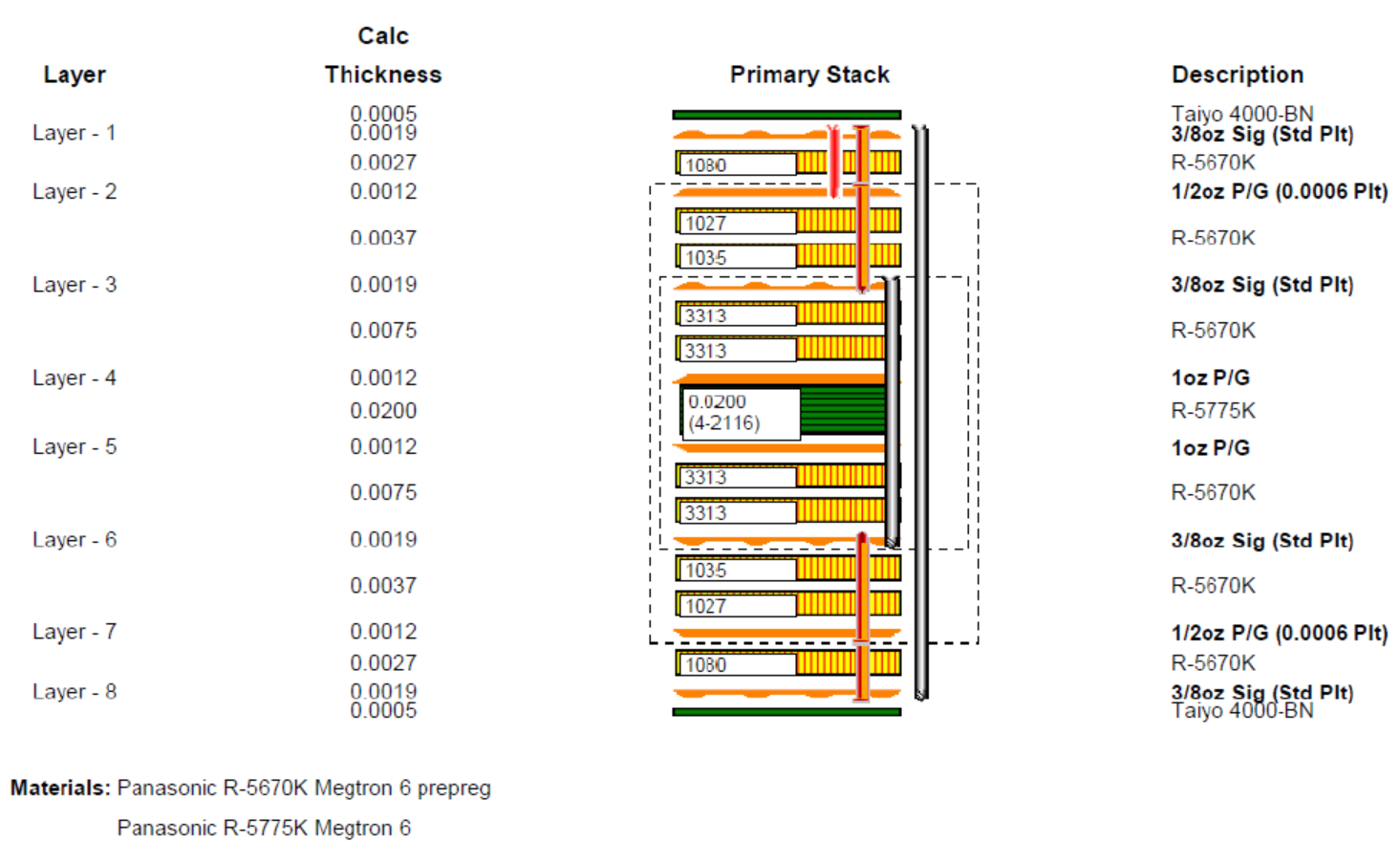

1. 为了保证 S32V234 有更高的性能表现,推荐使用 8 层或以上的 PCB 叠层结构,同时建议器件采用双面贴片设计,以下 S32V234-EVB2 PCB 叠层结构可作为参考。

如下图 2.1 Layer stack S32V234-EVB2 board

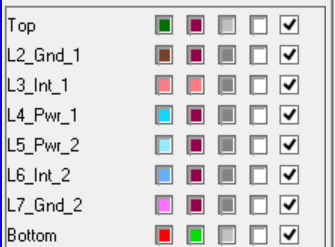

2. 层的定义设计原则

① 器件面下层(第二层)为地平面,为器件面布线提供参考平面;

② 所有信号层尽可能与地平面相邻;

③ 主电源层尽可能与对应地层相邻;

④ 建议采用对称结构设计。

如下图 2.2 PCB 层定义参考所示

3. DDR 走线规则

3.1 走线宽度及安全间距

① 所有走线建议线宽:4mil minimum,6mil nominal;

② VDD、VDDQ、VSS、VSSQ 必须铺铜皮,用尽量短的走线连接到这些平面;

③ 不同信号组之间保持 3W 线宽间距,差分对走线保持 1 倍线宽间距。

3.2 信号分组及走线长度要求

3.2.1 一个 DDR 控制器信号分组说明如下:

GROUP A:(DATA0—DATA7,DM0,DQS0P/ DQS0M);

GROUP B:(DATA8—DATA15,DM1,DQS1P/ DQS1M);

GROUP C:(DATA16—DATA23,DM2,DQS2P/ DQS2M);

GROUP D:(DATA24—DATA31,DM3,DQS3P/ DQS3M);

GROUP E(Address):ADDR0—ADDR14 共 15 条地址线;

GROUP G(Control):WE、CAS、RAS、CS0、CS1、CKE0、CKE1、ODT0、

ODT1、BA0、BA1、BA2、RESET 等控制信号;

GROUP F(Clock): CLK、CLKn 差分对。

3.2.2 信号线走线长度控制

① DQSnP/DQSnM 之间线长误差控制在 5mil 以内;

② DATAn 与 DMn 组内线长误差控制 50mil 以内,组间 120mil 以内;

③ GROUP E 与 GROUP G 以 CLK 长度为参考,误差控制 100mil 以内;

④ GROUP F 中 CLK、CLKn 差分对的线长误差控制在 5mil 以内。

3.3 走线规则

① DDR 的信号走线必须有完整参考面,以保证阻抗的连续性;

② 所有信号线禁止跨越不同的电源平面;

③ 避免其它类型的信号线穿越 DDR 走线区域;

④ DQS 不要与 CLK 信号相邻走线;

⑤ 注意蛇形走线的线与线中心间距保持 3W 线距;

⑥ S32V234 与 DDR 颗粒的每个供电管脚尽量靠近放置一个退耦电容。

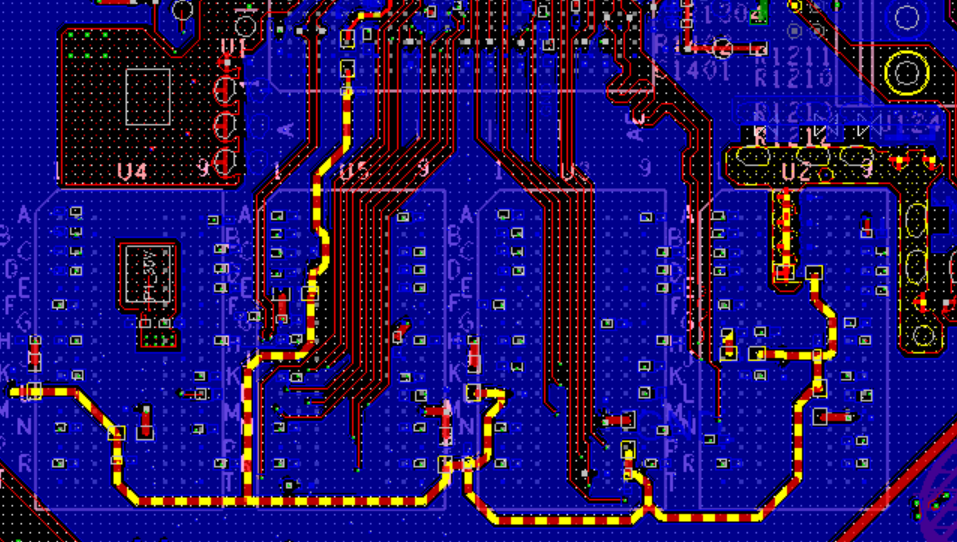

如下图 3.3 DDR 的退耦电容摆放

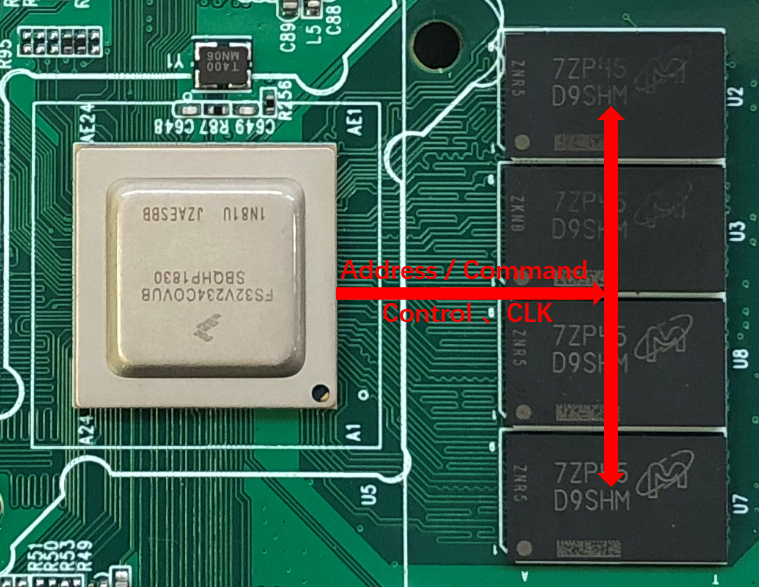

3.4 拓扑结构

① 若 PCB 布线空间允许,Address/Command、Control、CLK 应优先采用单纯的“T”型拓扑结构。

② 保证主控芯片至各个 DDR 颗粒的点对点长度误差小于 100mil;

③ 分支节点至各个 DDR 颗粒的布线长度应尽可能短,同时应最大限度保证分支节点到两个 DDR 颗粒的布线长度相等,必要时可采用蛇形线;

④ 对称的“T”型拓扑可以最大限度改善信号质量;

⑤ 为满足主控芯片至各个 DDR 颗粒等长要求做的蛇形线应优先考虑在主控至分支节点之间做补偿处理。

如下图 3.4 S32V234 DDR “T”型拓扑结构

3.5 VREF 处理

① VREF 尽量靠近芯片并走线尽量短,注意与数据线分开,避开干扰源;

② 走线线宽建议不小于 10mil;

③ 如有 VTT 网络,VREF 应与 VTT 分在不同的层或保持最少 150mil 距离。

如下图 2.5 VREF 走线

3.6 阻抗要求

① DDR 相关走线的单线特征阻抗控制在 50Ω;

② 差分对阻抗控制在 100Ω;

③ 推荐使用 FR-4 作为 PCB 的基板材料。

S32V234 平台的 DDR Layout 设计需要严格遵循设计规则,设计完成后需要做 PI & SI 仿真,所以如果没有这方面的设计能力,建议直接使用 NXP 验证过的 S32V234 + DDR Layout 参考设计,并且采用对应的叠层结构,按照阻抗控制要求制板,缩短研发时间,提升产品可靠性。

如需具体的技术交流讨论,请关注我,给我留言,也可以发邮件与我们联系(atu.cn@wpi-group.com)。

评论