MPC5744 芯片简介

一、 前言

MPC5744 是 NXP 推出的一颗基于 Power 架构内核的 32 位 MCU,采用哈佛架构,最高主频达到 200 MHz,内置容量 2.5MB 的Flash 和 384 KB 的SRAM。此外,它满足适用于汽车和工业功能安全应用的最高功能安全标准。本篇博文将为大家简要介绍MPC5744 芯片,具体内容包括 MPC5744 的内核特性、外设资源、功能特点以及应用方向等几个方面。

二、 内核介绍

MPC5744 采用了两个延迟锁步的 e200z4 的内核,分别为主核 e200z4251n3 内核以及校验核 e200z424,e200z424 内核是 e200z4251n3 内核的真子集,两个内核的寄存器集完全一样,区别在于 e200z424 内核没有指令缓存、数据缓存。当两个核心都使能的时候,校验核跟主核工作在延迟锁步的模式,那么什么是延迟锁步呢?

锁步是硬件冗余技术的一种,旨在提高系统的可靠性。在锁步模式下,同时将同一组输入发送到这两个内核中,然后这两个内核在相同的时钟周期内执行相同的计算,定期比较结果,看是否发生故障,一旦输出不匹配,通常会标记故障并执行重启。

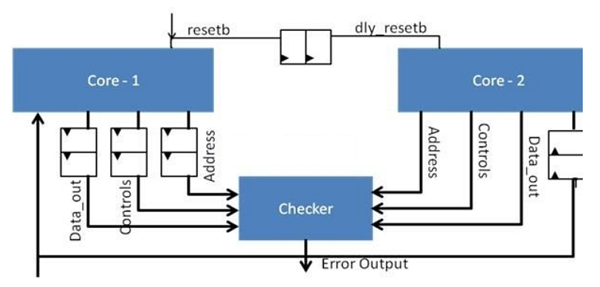

延迟锁步是锁步的一种,其中一个内核的输入延时了 N 个时钟周期,而另一个内核的输出也延迟相同的时钟周期,然后比较结果。采用延迟锁步可以获得时间分集,由于一个内核在 N 个时钟周期后将执行相同的运算,冲击这两个内核并以相同方式影响其功能的噪声脉冲的概率将大大减少。下图显示了延迟锁步的工作配置,馈送给内核 2 的数据被延迟了两个时钟周期,内核 2 的重置也延迟了两个时钟周期,内核 1 的输出延迟了两个时钟周期,然后通过校验电路进行结果比较,如发现故障则标记错误。

图 2.1 延迟锁步原理示意

e200z4251n3 和 e200z424 内核中内嵌有浮点运算单元,用于支持实时的单精度浮点数数字运算,同时也支持VLE(变长度编码),以提高代码密度。

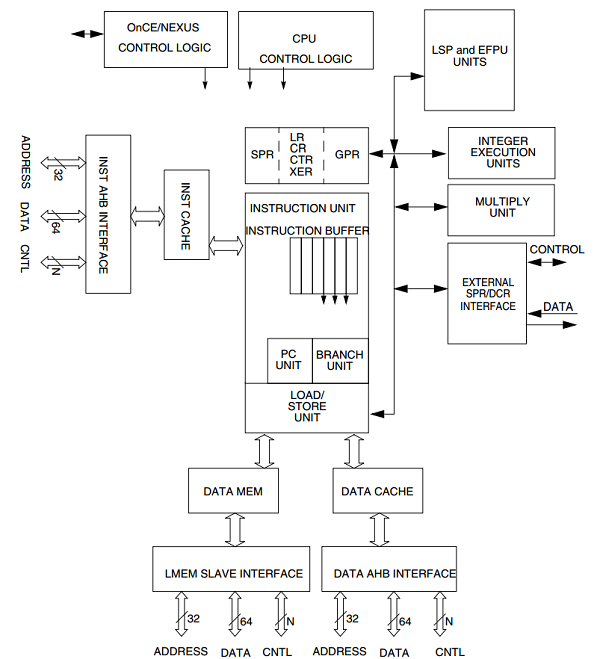

此外,e200z4251n3 和 e200z424 内核集成了一对整数执行单元、一个分支控制单元、指令提取单元,加载/存储单元,以及一个多端口寄存器,能够在一个时钟周期提供六次读和三次写操作。大部分整型指令执行周期为一个时钟。e200z4251n3 和 e200z424 内核还集成了一个 Nexus Class3+ 调试模块和一个内存保护单元。如下图所示为 e200z 的内核框图。

图 2.2 e200z 框图

三、 芯片资源

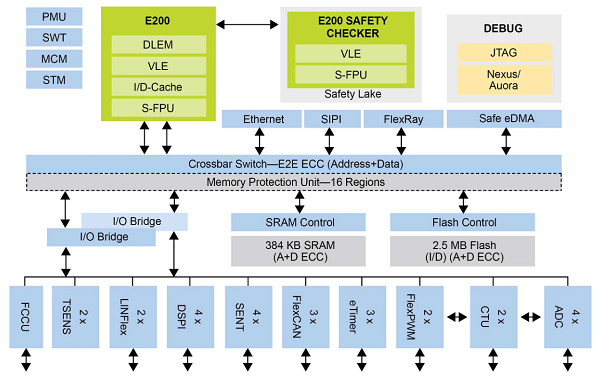

如下图所示为 MPC5744 芯片的功能框图。

图 3.1 MPC5744 框图

MPC5744 包含了丰富的外设资源,主要资源如下所示:

- 内存资源

- 内置 5 MB 的带 ECC 校验的 Flash

- 内置 384 KB 的带 ECC 校验的 SRAM

- 定时器资源

- 一个 4 通道 32 Bit 的 PIT 定时器

- 一个 4 通道 32 Bit的系统定时器模块

- 一个 32 Bit的软件看门狗定时器

- 3 个 16 Bit 6 通道的 eTimer 模块

- 2 个 16 Bit 8 通道的 FlexPWM 模块

- 通信模块

- 3 个 FlexCAN 模块,带 64 个消息缓冲区

- 1 个 FlexRay 模块,带 64 个消息缓冲区

- 2 个 LinFlexD 模块

- 4 个 SPI 模块

- 2 个 2 通道的 SENT 模块

- 1 个 10/100 Mbps Ethernet MAC

- 其它资源

- 4 个 12 Bit 16 通道的 ADC 模块

- 一个 SGEN (正弦波生成器)

- 一个 CRC 模块

- 一个 FCCU(错误收集和控制单元)

- 2 个 CTU (交叉触发单元)

四、 功能特点

MPC5744 芯片是一款专门为需要满足高汽车安全完整性等级(ASIL)的应用所设计的,因此其最大特点在于其安全性,MPC5744 的高安全性主要体现在以下方面:

- 采用双核延迟锁步的设计,提高代码执行的安全性

关于双核延迟锁步的机制,本文前面已经详细叙述过,因此不再说明,值得注意的是,MPC5744 在 DMA 中也使用了延迟锁步的设计,进一步确保了 DMA 传输过程的可靠性。

- Flash 和 SRAM 均带有 e2eECC,提高错误检测的能力

MPC5744 中提供了 e2eECC,可检测总线主设备和总线客户端的所有数据链路上的数据损坏。因此存储器不需要额外进行 ECC 计算。系统中有一个中央储存器错误管理单元,负责采集和报告与在 SRAM、外设系统 RAM 及闪存上所使用的 ECC 逻辑相关的错误事件,每当错误发生时,MEMU 都会收到一个错误信号,然后记录错误地址,设置相应的错误标记并报告给 FCCU。

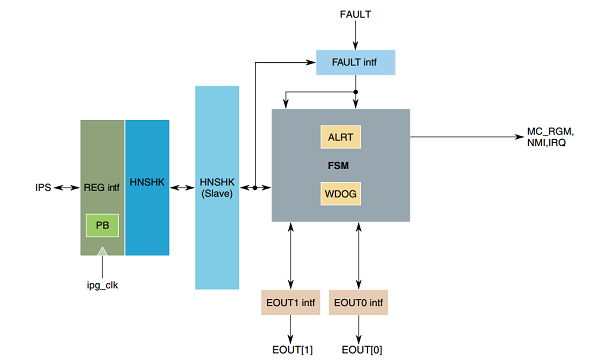

- 内置可编程的故障采集和控制单元(FCCU),可监控器件的完整性状态并提供灵活的安全状态控制

FCCU 提供了一个硬件通道来收集错误,当检测到错误发生时将设备转移到安全的状态中去,对于错误的收集和控制操作不需要 CPU 进行额外的干预。FCCU 会收集芯片中安全模块(例如 RCCU、e2eECC 等)的错误信息,错误发生时会按照用户的配置进行相应处理,例如进入中断处理、产生复位、进入 NMI 以及无响应等等。此外,芯片还提供两个外部指示引脚(EOUT0/1),可以就系统中发生的故障与外部环境进行通信,并遵循各类静态或切换协议。

图 4.1 FCCU 模块框图

- 内置时钟监控单元(CMU),可以监控系统的时钟输出是否正常

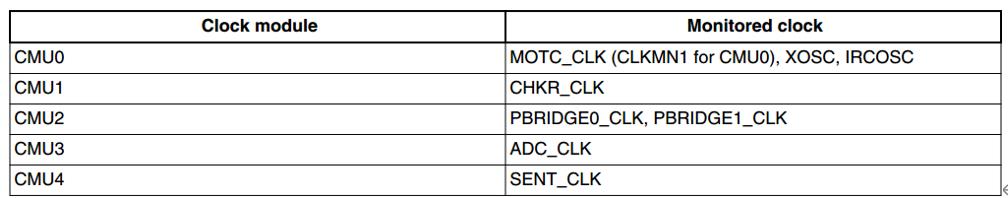

MPC5744 中集成有 5 个 CMU,每个 CMU 所监控的时钟如下表所示

五、 应用

MPC5744 的目标应用是对汽车安全完整性等级(ASIL)要求高的应用,主要的目标应用包括:

- 汽车制动与稳定控制

- 电动助力转向系统

- 电池管理系统

- 安全气囊

- 汽车雷达系统

六、参考资料

- 《MPC5744PRM》, Rev 6.1 , 2017.10

- 《MPC5744P》, Rev 6.1 , 2017.11

- https://www.dgzj.com/qiche/40731.html , 汽车电子元器件冗余设计机制 , 2015.05

- https://www.sohu.com/a/354116152_560178 , MCU 如何实现功能安全 ,2019.11

评论