一、前言

Hi3566V100 是一颗面向车载行车记录仪、驾驶员状态监控等领域推出的高性能、低功耗的 Camera SoC。Hi3566V100 内核为 Cortex A7 MP2 @792MHz,

支持双路1080p@30fps H.265/H.264 编码。

二、Hi3566V100 晶体及匹配电容原理设计思路

一个系统如果稳定运作需要时钟,而晶体是产生时钟的重要元件之一,调整匹配电容的参数可以将晶体的工作频率微调到标称值。

(1)晶体重要参数介绍

图 1 晶体重要参数

① 标称频率 (Nominal Frequency) 是晶体元件技术规范中规定的频率,它与晶体元件的实际工作频率有一定的差值。

② 负载电容 (Load Capacitance) 它是晶体中跨接晶体两端的总的有效电容(不是晶体外接的匹配电容),主要影响负载谐振频率和等效负载谐振电阻,

与晶体一起决定振荡电路的工作频率,通过调整负载电容,就可以将振荡器的工作频率微调到标称值。

③ 频率误差 (Frequency Tolerance) & 频率稳定度 (Frequency Stability) 用单位 ppm 来表示,即百万分之一 (Parts Per Million 1/106),是相对

标称频率的变化量,此值越小表示精度越高。比如,24MHz 晶体的频偏为 ±20ppm,根据公式 Δf=(f*ppm)/10^6,可以计算出频率的变化值是±480Hz,

即频率范围是 (999520 ~ 24.000480MHz)。

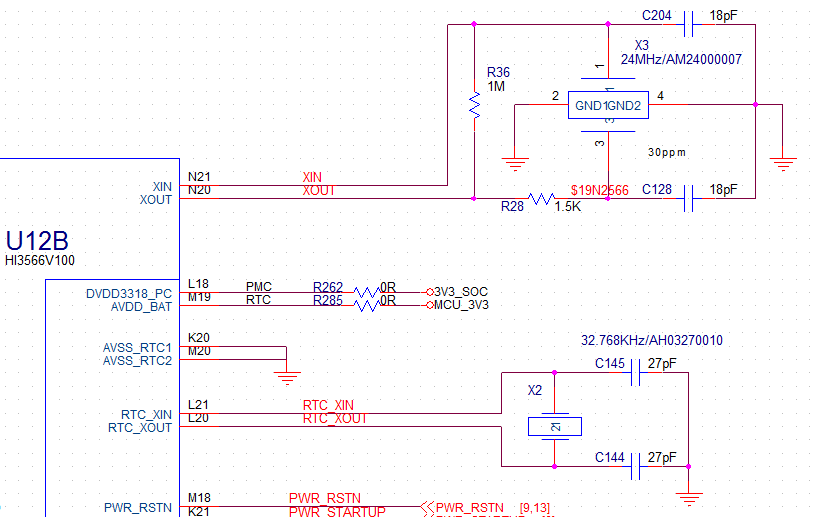

(2)Hi3566V100 的时钟电路包含 24MHz 和 32.768KHz 两颗晶体。

图 2 晶体部分接口原理图

上图中,晶体 X3 的 Pin1与芯片的 N21相连,Pin3 通过电阻 R28 与芯片的 N20相连,其中 R36 为反馈电阻 (一般 ≥1MΩ),R28 起到限制振荡幅度的作用,

X3 是无源晶体,C128、C204 是晶体的匹配电容。

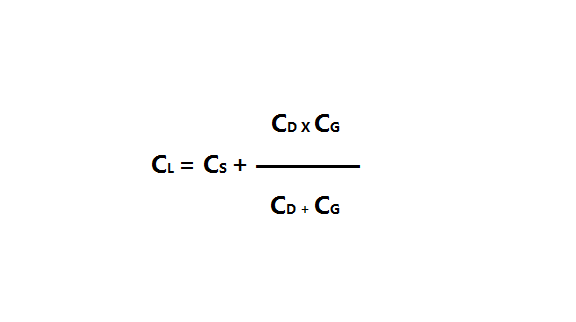

(3) 晶体负载电容计算公式

图 3 晶体负载电容计算公式

其中,CS 为晶体两个管脚间的寄生电容 (Shunt Capacitance),CD 表示晶体振荡电路输出管脚到地的总电容,包括 PCB 走线电容 CPCB、芯片管脚寄生电容

Co、外加匹配电容 C128,即 CD = CPCB + Co + C128;CG 表示晶体振荡电路输入管脚到地的总电容,包括 PCB 走线电容 CPCB、芯片管脚寄生电容 CI、外加

匹配电容 C204,即 CG = CPCB + CI + C204,一般 CS 为1pF 左右,CI 与 Co 一般为几pF,具体可参考芯片或晶体的数据手册。(假设晶体的负载电容 CL = 9pF,

CS = 1pF, CI = Co = 1pF, CPCB = 1pF, CD = CG)根据负载电容计算公式,则匹配电容 C128 = C204 = 14pF,而 14pF 电容不常用,故实际电路中取 18pF,

一般晶体的匹配电容取负载电容的 2 倍即可。(注意:不同品牌、不同型号的晶体,其固有的负载电容参数可能不同,那么电路中匹配电容的取值也会不同)

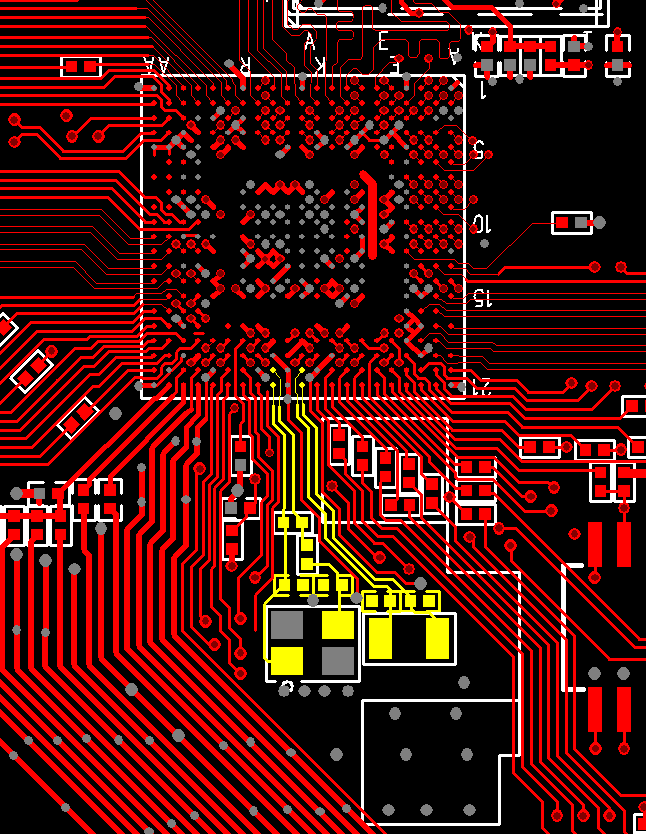

三、PCB 设计思路

1. 晶体、外部匹配电容与芯片之间的走线尽可能最短,如果走线过长,会对 EMC、ESD 与串扰产生非常敏感的影响,同时也会增加寄生电容。

2. 晶体及匹配电容的摆放位置要合理。

3. 晶体的信号走线全程做包地处理,并保证这些信号有完整的参考平面,晶体下方不能有高速信号穿过。

图 4 晶体及匹配电容的摆放及 PCB 走线

图 5 晶体及匹配电容 PCB 走线做包地

4. 如需进一步的技术交流讨论,请在 大大通 上关注我,并给我留言。

四、参考文献

1.《Hi3562V100/Hi3566V100 硬件设计用户指南》

2.《 HI3566V100DMEB_VER_B_SCH 》

3.《 HI3566V100DMEB_VER_B_PCB 》

评论