本内容主要介绍X9H核心板制板过程中的差分与单端阻抗相关的匹配计算与操作,并总结相关的经验分享给大家,希望给各位有所帮助。首先介绍几个相关的概念如下。

一、 差分信号

先了解一下差分信号的概念和介绍。

1、差分信号

差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。在这两根线上的传输的信号就是差分信号。信号接收端比较这两个电压的差值来判断发送端发送的是逻辑0还是逻辑1。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

一般类型有:USB、以太网、PCIE、SATA、RS485、RS422、HDMI、LVDS 。

常用对有:+/- 、PM/PN 、TXN/TXP 。

2 、简述几点差分布线的布线要求

(1)差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

如果等长和等距不能同时满足,则 PCB 差分走线的设计中最重要的规则就是匹配线长。同时为了弥补阻抗的匹配可以采用接收端差分线对之间加一匹配电阻。其值应等于差分阻抗的值。差分走线也可以走在不同的信号层中,但一般不建议 这种走法。因此尽量少跨层和走过孔,尽量少走弯路。

(2)差分线对之间要有GND 隔离,或者保持距离,不要太近。增大差分信号与其它信号走线的间距,或者通过GND 隔离。

(3)差分线要优先布线。

3 、举例USB PCB差分线设计建议

为了保证良好的信号质量,USB 2.0 端口数据信号线按照差分线方式走线。为了达到USB 2.0 高速480MHz 的速度要求,建议PCB 布线设计采用以下原则:

差分数据线走线尽可能短、直,差分数据线对内走线长度严格等长,走线长度偏差控制在±5mil 以内。

差分数据线控制 90±10%的均匀差分阻抗。

差分数据线走线尽可能在临近地平面的布线层走线且不要换层。

差分数据线走线应有完整的地平面层作为参考平面,不能跨平面分割。

差分数据线走线应尽量用最少的过孔和拐角,拐角可考虑用圆弧或者 135 度角,避免直角,以减少反射和阻抗变化。

避免邻近其它高速周期信号和大电流信号,并保证间距大于 50mil,以减小串扰。

二、阻抗参数

1、阻抗计算工具

推荐一款阻抗计算工具:Polar SI9000

2、几种计算阻抗的情形与参数含义介绍

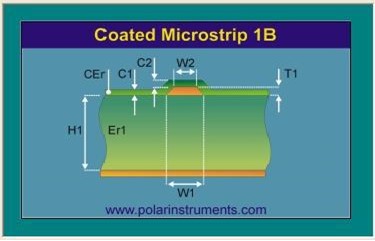

- 外层单端:Coated Microstrip 1B

H1:介质厚度

Er1:介电常数

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

T1:成品铜厚

C1:基材的绿油厚度

C2:铜皮或走线上的绿油厚度

Cer:绿油的介电常数

Zo:由上面的参数计算出来的理论阻值

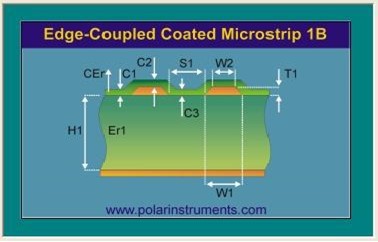

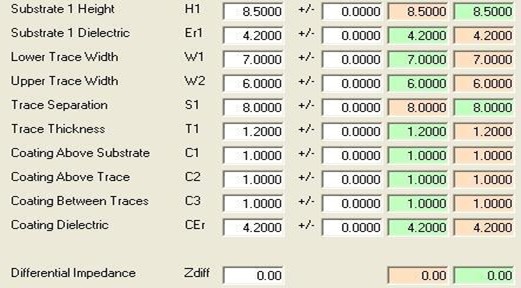

2.外层差分:Edge-Coupled Coated Microstrip 1B(重点)

H1:介质厚度

Er1:介电常数

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

S1:阻抗线间距

T1:成品铜厚

C1:基材的绿油厚度

C2:铜皮或走线上的绿油厚度

C3:基材上面的绿油厚度

Cer:绿油的介电常数

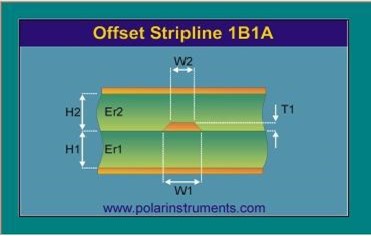

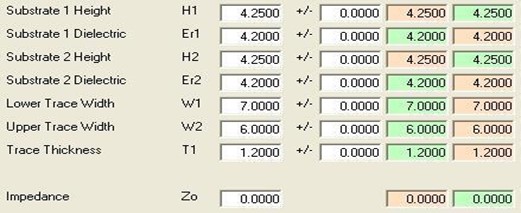

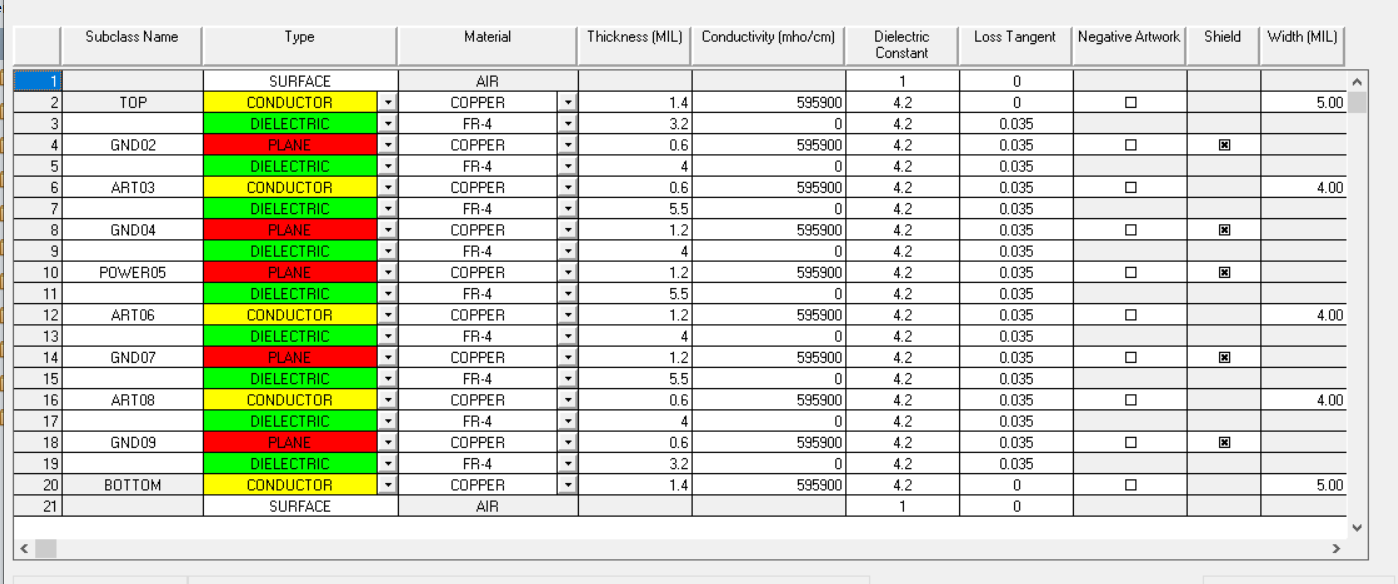

3.内层单端:Offset Stripline 1B1A

H1:介质厚度

Er1:H1厚度板材的介电常数

H2:介质厚度

Er2:H2厚度板材的介电常数

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

T1:成品铜厚

Zo:由上面的参数计算出来的理论阻值

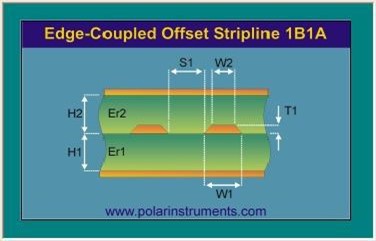

4.内层差分:Edge-Couled Offset Stripline 1B1A

H1:介质厚度

Er1:H1厚度介质的介电常数

H2:介质厚度

Er2:H2厚度介质的介电常数

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

S1:客户要求的线距

T1:成品铜厚

Zdiff:由上面的参数计算出来的理论阻值

3、影响 PCB 板迹线控制阻抗的几个相关参数分述

1. 铜层厚度

铜层厚度代表了 PCB 迹线的高度 T。内层铜箔通常情况下用到 1 OZ(厚度为 35 微米),也有在电源层要流过大电流时用到 2OZ(厚度为 70 微米)。外层铜箔常用 1/2 OZ(18 微米),但由于经过板镀和图形电镀最终成品外层铜厚将

达到48 微米(实际计算时用该值),设计成其他铜厚将较难控制铜厚厚度公差。若外层使用 1OZ铜箔,则最终铜厚将达到 65 微米。

2.PCB板迹线的上下线宽

由于侧蚀的影响, PCB 迹线的截面为一梯形,上下线宽差距以 1mil 来计算,其中下线宽等于要求线宽,而上线宽等于要求线宽减1mil。

3.阻焊层

阻焊层厚度按 10um 为准(选择盖阻焊模式),但有机印后将会有所增厚,但其变化将基本不会带来阻抗值的变化。

4.介质厚度

常用板材(芯板): (mm OZ/OZ *表示其数值为不包括铜箔厚度的芯板厚度)

0.13* 1/1 0.21* 1/1 0.25* 1/1 0.36* 1/1

0.51* 1/1 0.71* 1/1 0.80* 1/1

1.0 1/1 1.2 1/1 1.6 0.5/0.5 1.6 1/1 1.6 2/2

2.0 1/1 2.0 2/2 2.4 1/1 3.0 1/1 3.2 1/1

常用半固化片: (mm/mil)

7628: 0.175/6.9

2116: 0.11/4.3

1080: 0.066/2.6

实际计算厚度时注意半固化片随着两面线路结构不同而有所不同。

其中 GND 层包括铜面积占80%以上的线路层。如果介质在 HOZ 和 1OZ 铜箔之间,其厚度按 HOZ 情况计算。

5.介电常数

- Er 的值是线路板材质的绝缘常数(介电常数), 它对于线路的特性阻抗值而言是一个重要的组成部分。设计厂商因此有时会指定迹线阻抗值并依赖于线路板制造商来控制流程,以使迹线阻抗满足设计厂商指定的技术规范。

- 迹线的控制阻抗与板材介电常数的平方根成反比。

- 通过板材供应商提供的板材阻抗范围为 4.2~5.2,而 POLAR 公司建议单端采用 4.2,而差分若两线间距小会有所影响则建议采用 4.7。

- 根据一年多来各阻抗实验及生产板,我公司选用 4.2 进行计算能符合要求。

- 由于介电常数与板材型号和信号频率有相关性,设计人员应该充分考虑该影响。如:高频板材有介电常数 2.5 等。

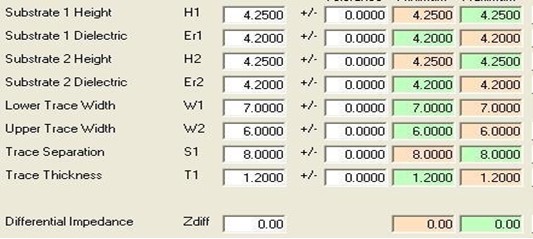

4、 X9H核心板制板要求与叠层阻抗信息

X9H核心板制板基本信息如下:

|

1 |

档名 |

P20-034 Dragonfly-X9H_Core Board__20210518 |

|

2 |

层数 ( 层 ) |

10 |

|

3 |

数量 ( 片 ) |

10 |

|

4 |

板厚 ( mm ) |

1.6 |

|

5 |

参考尺寸 ( mm ) |

82.5 × 61.5 |

|

6 |

拼板方式 ( 行 × 列 ) |

板厂拼板,并回传确认 |

X9H核心板工艺要求如下:

|

1 |

板材 |

FR-4 TG17 |

|

2 |

表面处理 ( 喷锡/沉金/镀金 ) |

沉金 |

|

3 |

铜箔厚度 ( oz ) |

内层: 0.5 |

|

外层: 1 | ||

|

4 |

阻焊油颜色 |

绿色( 双面 ) |

|

5 |

丝印颜色 |

白色( 双面 ) |

|

6 |

最小线宽线距 ( mil ) |

线宽: 3.2 |

|

7 |

最小孔径 ( mil ) |

8 |

|

8 |

盲埋孔 |

无 |

|

9 |

过孔阻焊盖油 |

是 |

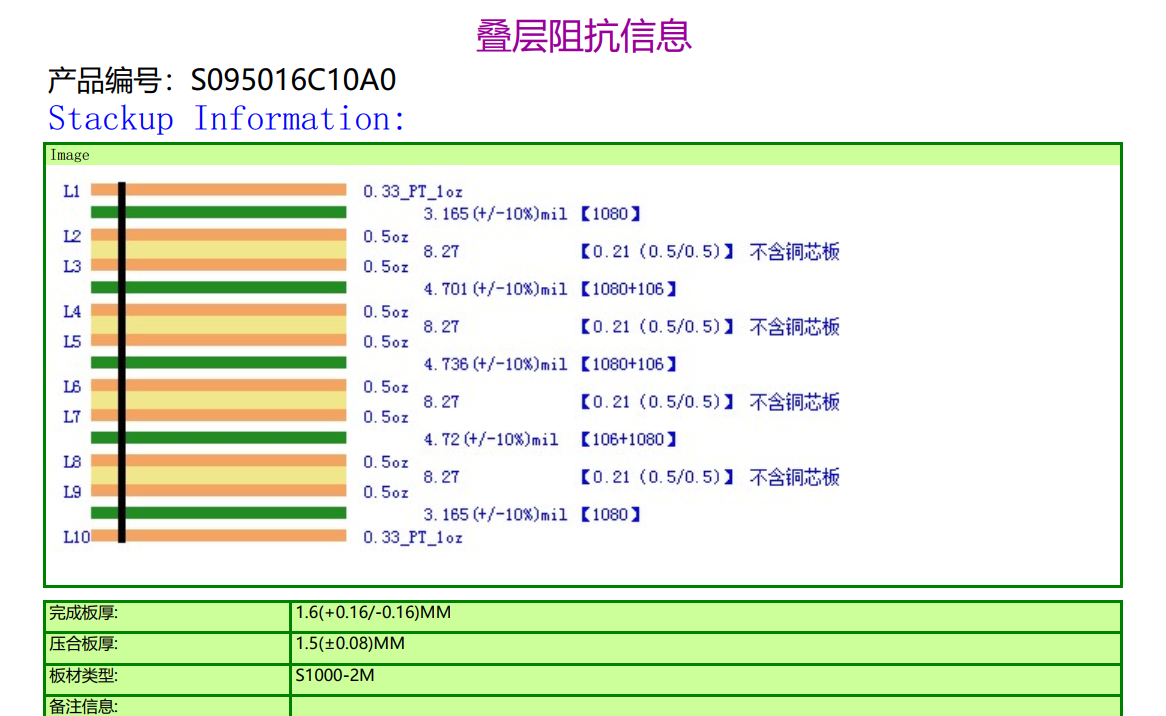

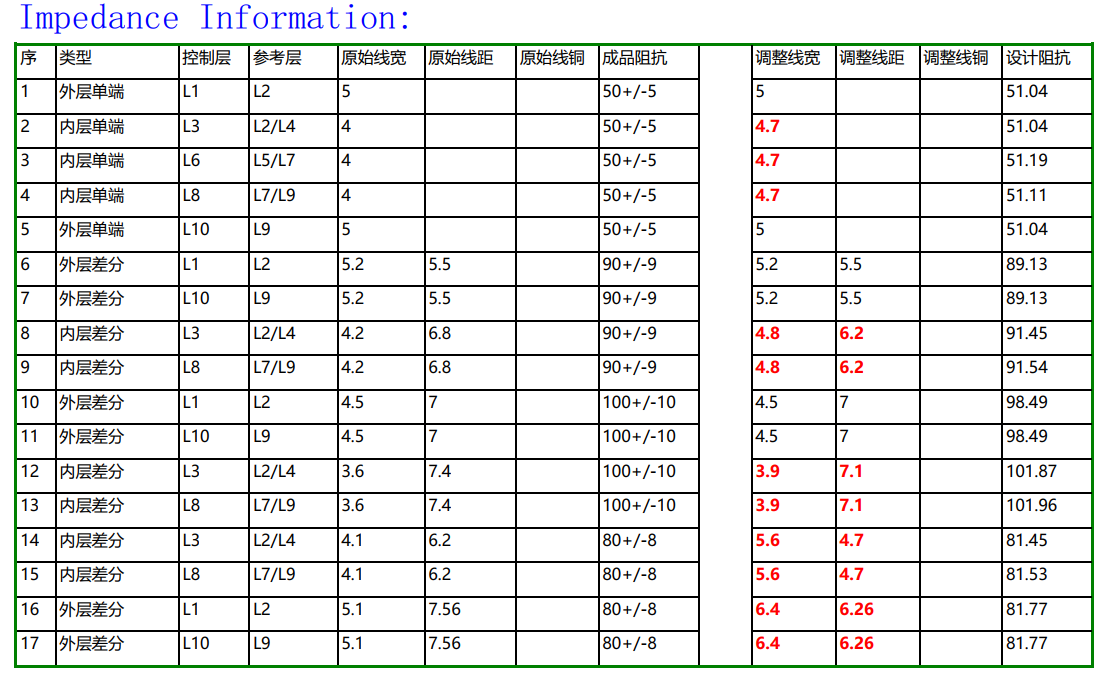

X9H核心板叠层图如下:

通过上面的匹配计算方式可以计算出相应的阻抗要求下的相关参数。下面是通过上面的方式匹配计算得到的叠层阻抗信息。

X9H核心板叠层阻抗信息:

5、 X9H 核心板是基于SemiDrive X9H MPU芯片的开发套件,核心板实物图片如下:

三、总结

1、阻抗计算参数与阻抗影响关系

- H介质层厚度: H与Zo成正比,H值越大,Zo越大;

- W1线宽: W1与Zo成反比,W1值越大,Zo越小;

- T 铜厚: T与Zo成反比,T值越大,Zo越小;

- Er 介电常数: Er与Zo成反比,Er值越大,Zo越小;

- S差动阻抗线间距: S与Zo成正比,S值越大,Zo越大;

2、主要通过下面的途径对阻抗设计进行微调

◆ 调整阻抗控制线宽、间距。

◆ 调整介质层厚度。

通过调整阻抗控制线宽、间距和介质厚度参数可以实现阻抗的控制。阻抗控制线宽、间距、叠层结构,这些是硬件工程师在 PCB 设计时设置,一般制版时要求严格禁止修改PCB图的任何东西。至于介电常数、介质厚度、成品铜厚,这些是与材质有关。

如对此有更多需求,敬请联系世平集团 ATU 部门,atu.cn@wpi-group.com。

参考文献:

《高速电路设计实践》

《信号完整性揭秘:于博士SI设计手记》

《Printed Circuit Board Design Techniques for EMC Compliance》

评论

rogerhu

2023年1月9日