一、简介

2019年10月,在恩智浦 ARM 技术大会上一则宣传语彻底引爆微控制器界,“单片机首次迈入 1GHz 主频大关”。

i.MX RT 系列的 i.MX RT1170 首次将 ARM Cortex-M7 的主频提升至 1 GHz,并且首次引入双核概念,双核系统搭载一颗高性能内核和一颗高能效内核。

一颗主频高达 400MHz Cortex-M4 内核,这颗 Cortex-M4 可以用作专门处理一些相对简单的外设资源、金融级别的信息安全、低运行/低待机功耗,有了这颗高能效的 Cortex-M4 内核,另一颗超高性能的 Cortex-M7 核可以专注于音视频识别与处理、千兆以太网通信控制等复杂任务上,双核系统中这两颗内核均可作为主从关系,用户可以自定义主从关系,从核由设定的主核启动后激活

二、i.MX RT1170 应用

这颗强劲的 MCU 的应用也十分广阔:

智能家居的HMI或主处理器音频/语音处理

新兴消费/零售设备

工业控制

楼宇控制

智能能源系统

马达驱动

医疗仪器

汽车/摩托车 HMI

Auto 处理器

三、双核通信

3.1 双核通信简介

有着高性能和高能效双核的 i.MX RT1170 ,在双核系统中双核间的通信更是系统中十分重要的环节,双核间有四种通信分享资源方式 :

MU

SEMA4

RDC/XRDC2

分享内存

3.2 MU

通过 MU(Messaging Unit)消息传递单元,一个核可以向另一个核发送 32 位的消息,并触发另一个核的中断,它支持四个双向通道。

3.3 SEMA4

SEMA4 通常用于保护多核环境中的资源,以防止不同的主机同时使用一个资源,该资源可以是内存块、外设或者甚至是内存中的 SW 对象,SEMA4最多支持 16 个门,只有成功锁住这个门并获得 sema4 的核,才能使用这个sema4门保护的资源,其他核必须等待,直到拥有这个门的核,释放或开放这个门。

3.4 RDC/XRDC2

RDC/XRDC2 用于资源隔离,资源可以是外围设备或内存,权限可以被读、写,也可以同时被读和写。

例如,我们可以将 LPUART1 分配到 CM7 域,那么只有 CM7 核可以访问 LPUART1。如果其他总线主机( 如 CM4 核)访问 LPUART1 就会发生 ISR 冲突

3.5 分享内存

CM7 核和 CM4 核都可以访问共享内存,如果一个数据块需要从一个核传递到另一个核,那么 MU 共享内存可以是一个很好的候选。

典型的工作流程如下:

- 一个核向 B 核写入块数据

- 步骤 1 完成后,A 核触发 B 核 MU 中断,B 核知道 A 核有数据块准备好。

- B 芯读取数据块并处理。

- 步骤3完成后,B核触发 A 核 MU 中断,A 核知道 B 核已经处理了数据块,然后 A 核可以加载 B 核的下一个数据块。

四、双核通信例程

4.1 创建双核 MU 工程

以下例程介绍以四种通信方式中的 MU 通信方式为例,从创建 SDK 工程开始、概述例程、到演示例程效果。

4.1.1 SDK 获取

SDK 可再 NXP 官网根据需求添加部件自定义生成 SDK,NXP MCUXpresso SDK Builder 的链接如下 https://mcuxpresso.nxp.com/en/welcome

4.1.2 创建 MU 工程

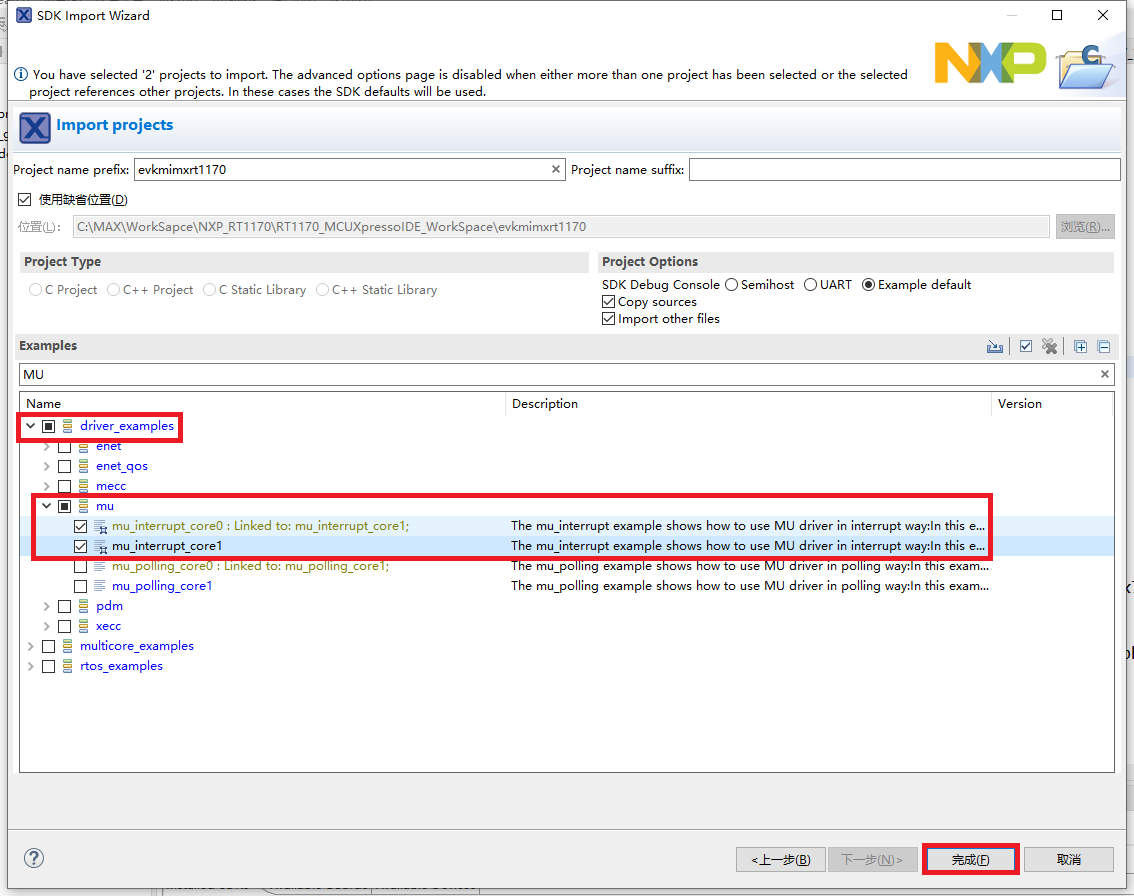

文件 -> Import SDK Examples -> evkimxrt1170 -> driver_examples -> mu -> 选择 mu_interrupt_core0 会Link 上 mu_interrupt_core1 自动勾选。

4.1.3 双核通信调试

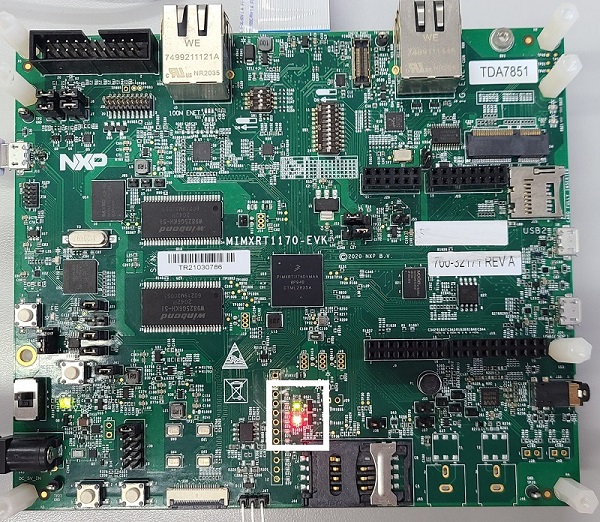

双核调试指南,请参阅入门 MCUXpresso SDK For MMXRT1170-EVK ( 文档MCUXSDKMIMXRT117XGSUG),可在 MCUXpresso SDK Builder 官网上找到。

4.2 双核通信

4.2.1 初始化 MU

初始化 MU 模块,仅使能 MU 时钟功能,参数为 MU 外设基地址。

/* MUA init */

MU_Init(APP_MU);

4.2.2 激活从核 CM4

主核程序里添加代码来激活启动从核,激活从核的第一步是加载从核程序,程序从加载执行位置上可分为两种,一种是在 Flash 中执行,另一个是拷贝到 RAM 中执行。

#if CORE0_BOOT_CORE1

/* Boot core 1. */

#if BOOT_CORE1_BY_MU

MU_BootCoreB(APP_MU, APP_CORE1_BOOT_MODE);

#else

APP_BootCore1();

#endif

#endifCOR1_BOOT_ADDRESS 是从核 App Image 在外部 Flash 里存放的首地址。

#define CORE1_BOOT_ADDRESS 0x20200000

IOMUXC_LPSR_GPR->GPR0 = IOMUXC_LPSR_GPR_GPR0_CM4_INIT_VTOR_LOW(CORE1_BOOT_ADDRESS >> 3);

IOMUXC_LPSR_GPR->GPR1 = IOMUXC_LPSR_GPR_GPR1_CM4_INIT_VTOR_HIGH(CORE1_BOOT_ADDRESS >> 16);

4.2.3 开启 MU 中断, MU 发送与接收数据

启用 MU 发送和接收中断,在中断处理函数中发送和接收数据。

/* Enable transmit and receive interrupt */

MU_EnableInterrupts(APP_MU, (kMU_Tx0EmptyInterruptEnable | kMU_Rx0FullInterruptEnable));

/* MU 发送 */

MU_SendMsgNonBlocking(APP_MU, CHN_MU_REG_NUM, g_msgSend[g_curSend++]);

/* MU 接收 */

g_msgRecv[g_curRecv++] = MU_ReceiveMsgNonBlocking(APP_MU, CHN_MU_REG_NUM);

4.2.4 例程演示效果

从核程序启动相似,烧录激活另一核步骤,同样通过 API MU_Init(APP_MU) 启动 MU 后,通过 MU_SetFlags(APP_MU, BOOT_FLAG) API 发送标志到主核心 0,通知器核心 1 的 MU 单元也已经启动完成,随后进入等待 MU 数据接收或发送完成,接收到的数据经过比对相同后 , CM4 核会控制 LED 闪烁,以表示双核通信例程实验成功。

串口 LOG 打印:

开发板 LED 闪烁:

评论