一、前言

本文以世平集团推出的 NXP Echoes-S32K144 评估板为例,使用配置 I2C 模块发送与接收数据,为了更直观观察 LPI2C 的工作效果,我们发送命令控制 Buck_boost CPSQ5206 并每秒发送读取命令读取 CPSQ5206 内部寄存器状态使用 LPUART 打印。

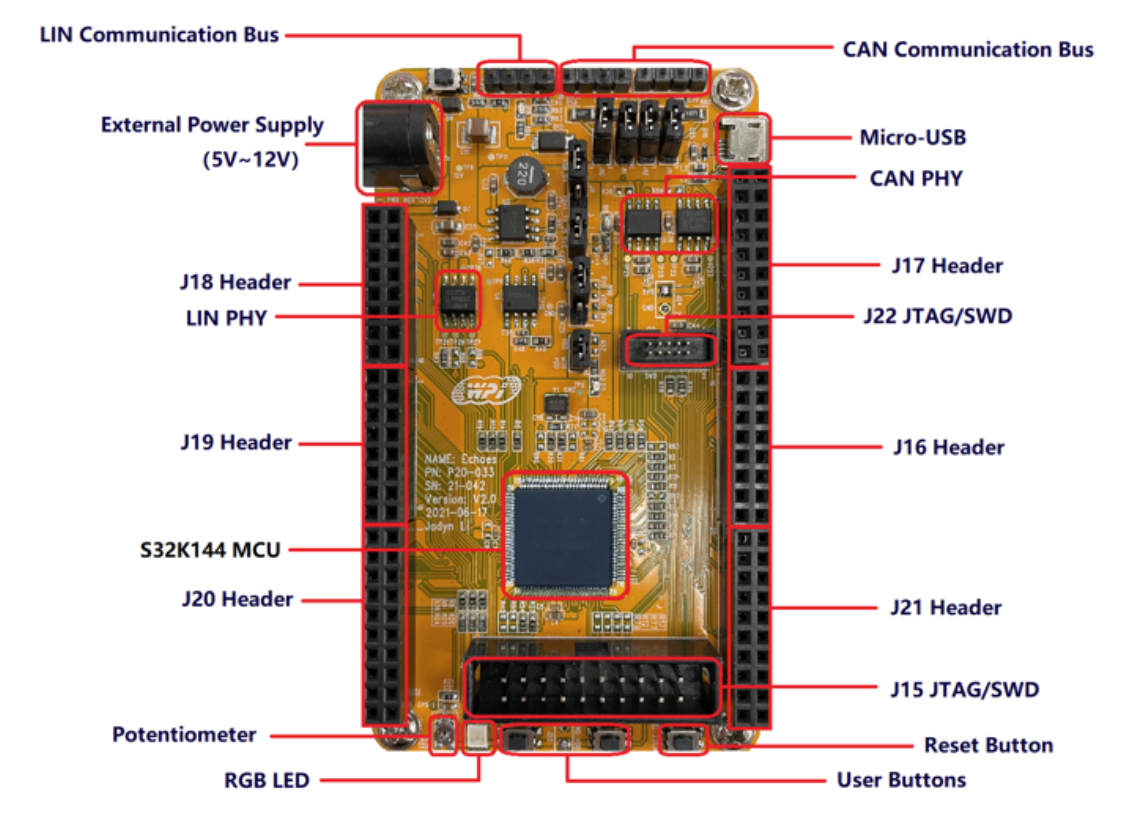

S32K144 是恩智浦(NXP)公司于 2017 推出面向通用汽车应用市场的高性能微处理器,该微处理器基于 32位 ARM Cortex-M4F 内核,最快内核频率达 112MHz。NXP Echoes-S32K144评估板采用 14×14mm LQFP100 封装,引脚间距 0.5mm,具有丰富的外设资源。该方案支持 JTAG 标准调试接口和 JTAG 4 线 SWD 调试模式,具有 micro USB 或外部 12V 电源两种供电选择,板载 CAN、LIN 与 UART 连接。

图 1-1 NXP Echoes-S32K144评估板

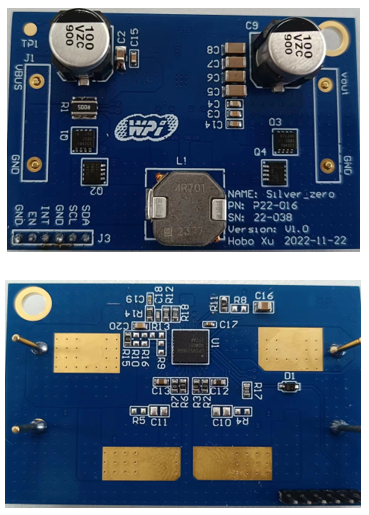

Silver_zero 是大联大世平集团推出的一款 DC/DC 电压调节方案,采用数字控制式 Buck_Boost CPSQ5206C。CPSQ5206 是AEC-Q100 认证的同步 4 开关 Buck-Boost 控制器,支持 3.8V 到 36V 的宽输入电压范围,并提供分辨率为10mV 的 2.0V 到 36V 可编程输出电压。当使用 5mΩ 电流传感电阻时,控制器可输出分辨率为 50mA 高达 8A 的调节电流。为确保变流器的安全运行 CPSQ5206 还提供输入/输出过压保护、输出短路保护、MOSFET 逐周期限流和热关机等全面保护。

图 1-2 Silver_zero

本文将各模块独立介绍并在各模块章节中讲解初始化函数代码,最后在主函数代码章节中调用各模块初始化函数。由于模块头文件为各函数声明,所以本文默认各头文件声明已创建并编写无误,若未有头文件,可创建 .h 文件并将各函数名复制到 .h 文件中编译成功即可。

二、S32K144 I2C 模块

2.1 S32K144 I2C 模块介绍

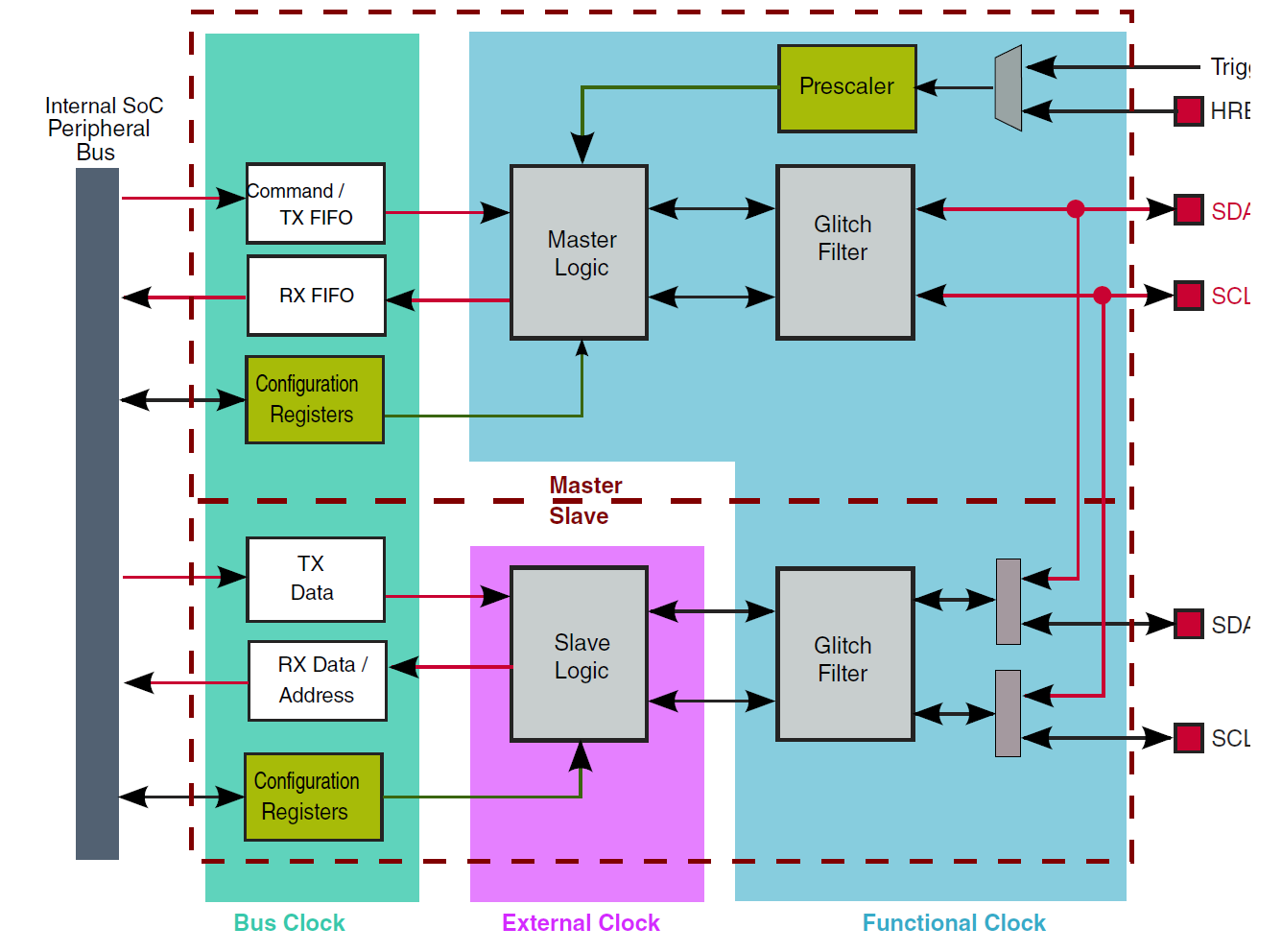

LPI2C 是一种低功耗的集成电路间(I2C)模块,它可以作为主设备或者从设备的 I2C 总线的有效接口。如果存在可用的适当时钟,该模块可以在停止模式下继续运行,并且设计用于低 CPU 减轻 DMA 访问 FIFO 寄存器消耗。

LPI2C 模块同样符合系统管理总线(SMBus) 2.0 规范。

S32K144 具有 1 个 LPI2C 模块,这些模块具有以下特点:

LPI2C 支持以下 I2C 规范功能:

- 支持标准、快速、快速+和超快模式。

- 从机支持 HS 模式。

- 如果 SCL 引脚实现电流源上拉(设备特定),主机将支持 HS 模式。

- 支持多主机,包括同步与仲裁。

- 时钟展宽。

- 通用调用,7 位和 10 位寻址。

- 软件复位、START 字节和设备 ID 需要软件支持。

LPI2C 主机支持以下功能:

- 命令/发送 4 字 FIFO。

- 命令 FIFO 将在启动传输之前等待空闲 I2C 总线。

- 命令 FIFO 可以启动(重复)START 和 STOP 条件以及一个或多个主接收机传输。

- STOP 条件可以从命令 FIFO 生成,或在传输 FIFO 为空时自动生成。

- 主机请求输入可以用于控制 I2C 总线发送的开始时间。

- 灵活的接收数据匹配可以在数据匹配时产生中断或者丢弃不需要的数据。

- 标志和可选中断,用以发送重复启动条件、停止条件、仲裁丢失、意外 NACK 和命令字错误的信号。

LPI2C 从机支持以下功能:

- 单独的 I2C 从机寄存器,可以做大限度地减少由主从机切换造成的软件消耗。

- 支持 7 位或 10 位寻址、地址范围、SMBus 警报和通用呼叫地址。

- 发送数据寄存器支持中断或 DMA 请求。

- 接收数据寄存器支持中断或 DMA 请求。

- 软件可控制的 ACK 或 NACK,具有 ACK/NACK 位上的可选时钟扩展。

- 可配置时钟展宽,以避免传输 FIFO 不足和接收 FIFO 超时。

- 标志和可选的数据包结束中断、STOP 条件或位错误检测。

图2.1-1 LPI2C 框图

2.2 S32K144 LPI2C 工作模式与信号描述

表2.2.1 LPI2C 模块支持的芯片模式

|

芯片模式 |

LPI2C 工作 |

|

运行模式 |

正常工作 |

|

停止或等待模式 |

如果 Doze Enable 位(MCR[DOZEN])置 0,且 LPI2C 使用外部或内部时钟源在停止或等待模式下保持运行,则 LPI2C 可以继续运行 |

|

低泄漏停止模式 |

Doze Enable(MCR[DOZEN])位被忽略,LPI2C 将在确认进入低泄漏模式之前等待电流传输完成任何未决操作。 |

|

调试模式 |

如果调试使能位(MCR[DBGE])置位,LPI2C 将会继续运行。 |

表2.2.2 LPI2C 模块信号描述

|

信号 |

描述 |

I/O |

|

SCL |

LPI2C 时钟线。在四线模式下是 SCL 输入引脚。 |

I/O |

|

SDA |

LPI2C 数据线。在四线模式下是 SDA 输入引脚。 |

I/O |

|

HREQ |

如果 I2C 总线空闲并且被置位的情况下,主机请求可以发起 LPI2C 主传输。 |

I |

|

SCLS |

I2C 辅助时钟线。在四线模式下是 SCLS 输出引脚。如果 LPI2C 主/从被配置成单独使用的引脚,则是 LPI2C 的从 SCL 引脚。 |

I/O |

|

SDAS |

I2C 辅助数据线。在四线模式下是 SDAS 输出引脚。如果 LPI2C 主/从被配置成单独使用的引脚。则是 LPI2C 的从 SDA 引脚。 |

I/O |

2.3 S32K144 LPI2C 寄存器介绍

LPI2C 模块由 28 个 32 位寄存器构成,这些寄存器又分为主机寄存器与从机寄存器,详细的寄存器映射见下表。

表2.3.1 LPI2C Memory Map

|

Offset |

Register |

Width (In bits) |

Access |

Reset value |

|

0h |

Version ID Register (VERID) |

32 |

RO |

01000003h |

|

4h |

Parameter Register (PARAM) |

32 |

RO |

00000202h |

|

10h |

Master Control Register (MCR) |

32 |

RW |

00000000h |

|

14h |

Master Status Register (MSR) |

32 |

W1C |

00000001h |

|

18h |

Master Interrupt Enable Register (MIER) |

32 |

RW |

00000000h |

|

1Ch |

Master DMA Enable Register (MDER) |

32 |

RW |

00000000h |

|

20h |

Master Configuration Register 0 (MCFGR0) |

32 |

RW |

00000000h |

|

24h |

Master Configuration Register 1 (MCFGR1) |

32 |

RW |

00000000h |

|

28h |

Master Configuration Register 2 (MCFGR2) |

32 |

RW |

00000000h |

|

2Ch |

Master Configuration Register 3 (MCFGR3) |

32 |

RW |

00000000h |

|

40h |

Master Data Match Register (MDMR) |

32 |

RW |

00000000h |

|

48h |

Master Clock Configuration Register 0 (MCCR0) |

32 |

RW |

00000000h |

|

50h |

Master Clock Configuration Register 1 (MCCR1) |

32 |

RW |

00000000h |

|

58h |

Master FIFO Control Register (MFCR) |

32 |

RW |

00000000h |

|

5Ch |

Master FIFO Status Register (MFSR) |

32 |

RO |

00000000h |

|

60h |

Master Transmit Data Register (MTDR) |

32 |

WORZ |

00000000h |

|

70h |

Master Receive Data Register (MRDR) |

32 |

RO |

00004000h |

|

110h |

Slave Control Register (SCR) |

32 |

RW |

00000000h |

|

114h |

Slave Status Register (SSR) |

32 |

W1C |

00000000h |

|

118h |

Slave Interrupt Enable Register (SIER) |

32 |

RW |

00000000h |

|

11Ch |

Slave DMA Enable Register (SDER) |

32 |

RW |

00000000h |

|

124h |

Slave Configuration Register 1 (SCFGR1) |

32 |

RW |

00000000h |

|

128h |

Slave Configuration Register 2 (SCFGR2) |

32 |

RW |

00000000h |

|

140h |

Slave Address Match Register (SAMR) |

32 |

RW |

00000000h |

|

150h |

Slave Address Status Register (SASR) |

32 |

RO |

00004000h |

|

154h |

Slave Transmit ACK Register (STAR) |

32 |

RW |

00000000h |

|

160h |

Slave Transmit Data Register (STDR) |

32 |

WORZ |

00000000h |

|

170h |

Slave Receive Data Register (SRDR) |

32 |

RO |

00004000h |

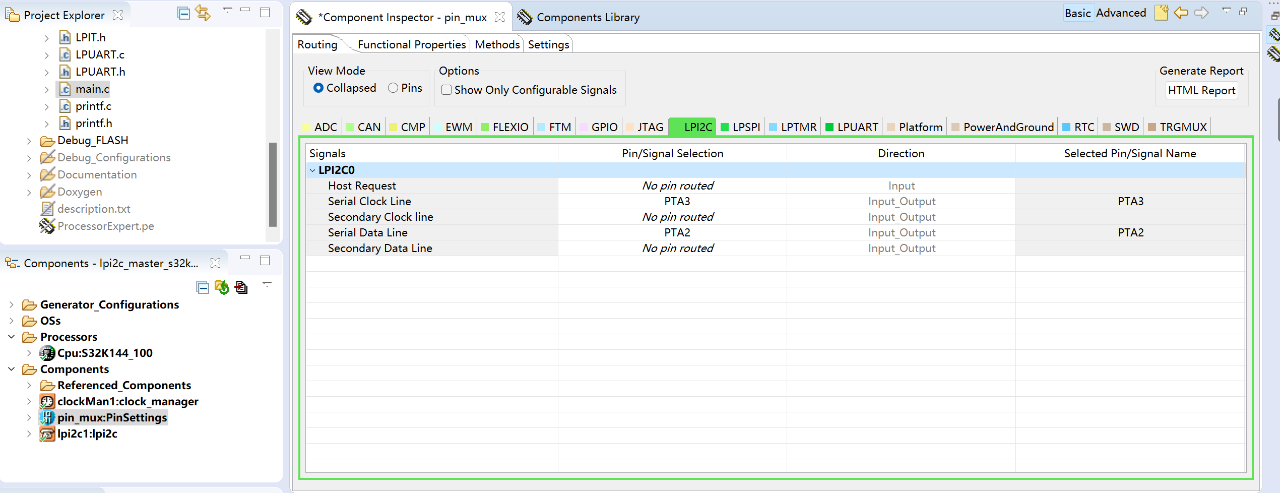

2.4 S32K144 LPI2C 例程导入

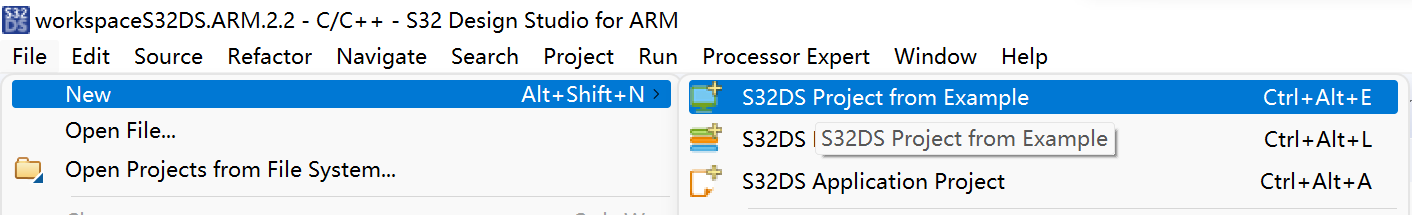

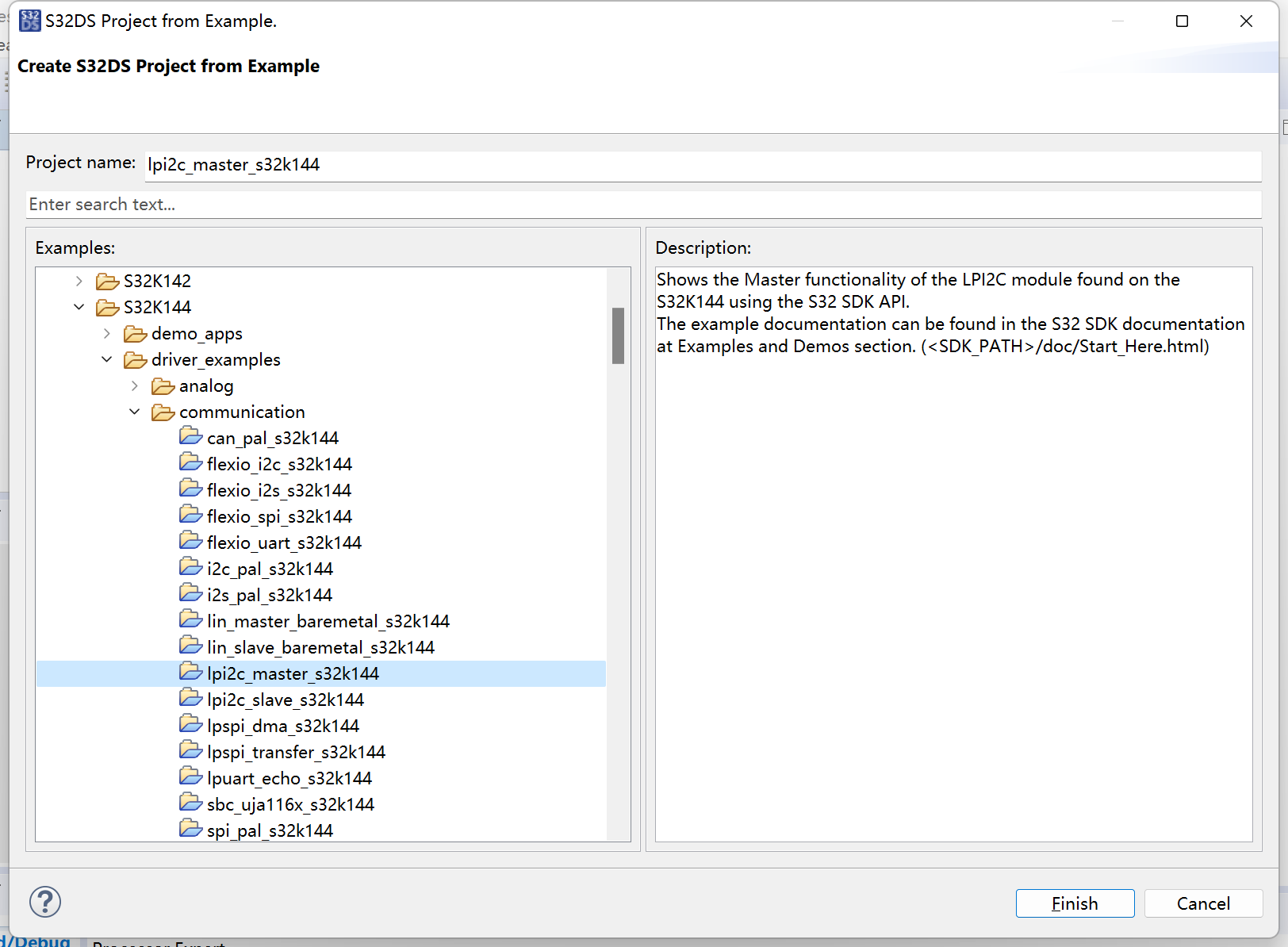

由于 LPI2C 寄存器过多直接对寄存器编程操作过于繁杂,所以我们使用 S32DS 内的库函数进行编程具体操作如下。(IDE:S32 Design Studio for ARM Version 2.2;SDK:S32K1xx RTM v3.0.0)

- 打开S32 Design Studio,点击:“File”->“New”->“S32DS Project from Example”。

- 在弹出的窗口选取 S32K144 目录下的 lpi2c_master 例程,点击“Finish”。

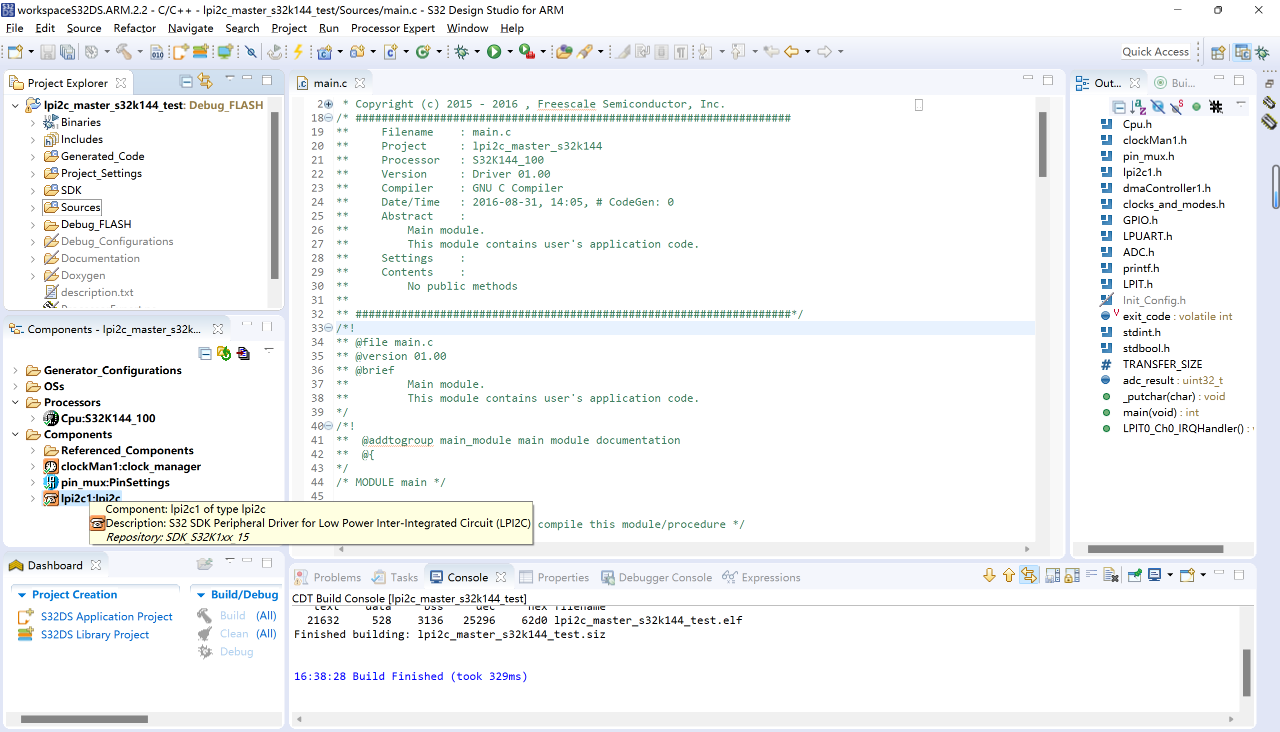

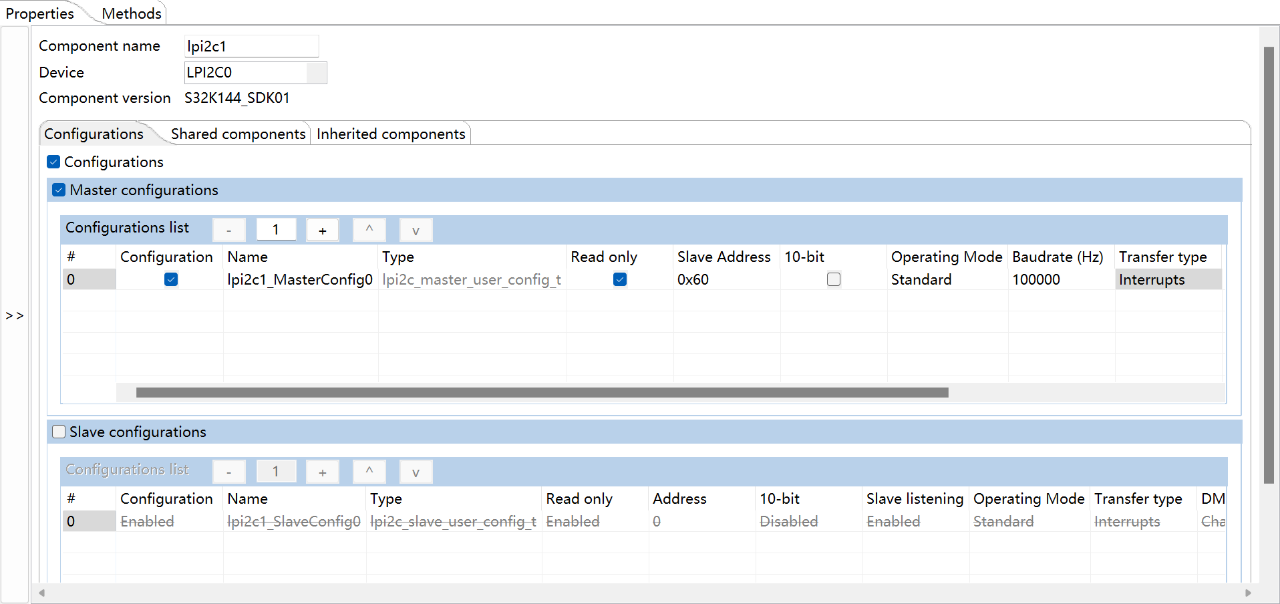

- 导入例程后双击左侧的“lpi2c1:lpi2c”按钮进入 I2C 配置。

- 在跳出窗口内将 Slave Address 设置成 0x60,Operating Mode 设置成 Standard,Baudrate (Hz) 设置成 100000。(CPSQ5206 芯片 I2C 地址可选地址为 60H、62H,由外部电路决定,Silver_zero 的外部电路设计确定其 I2C 地址为 60H。)

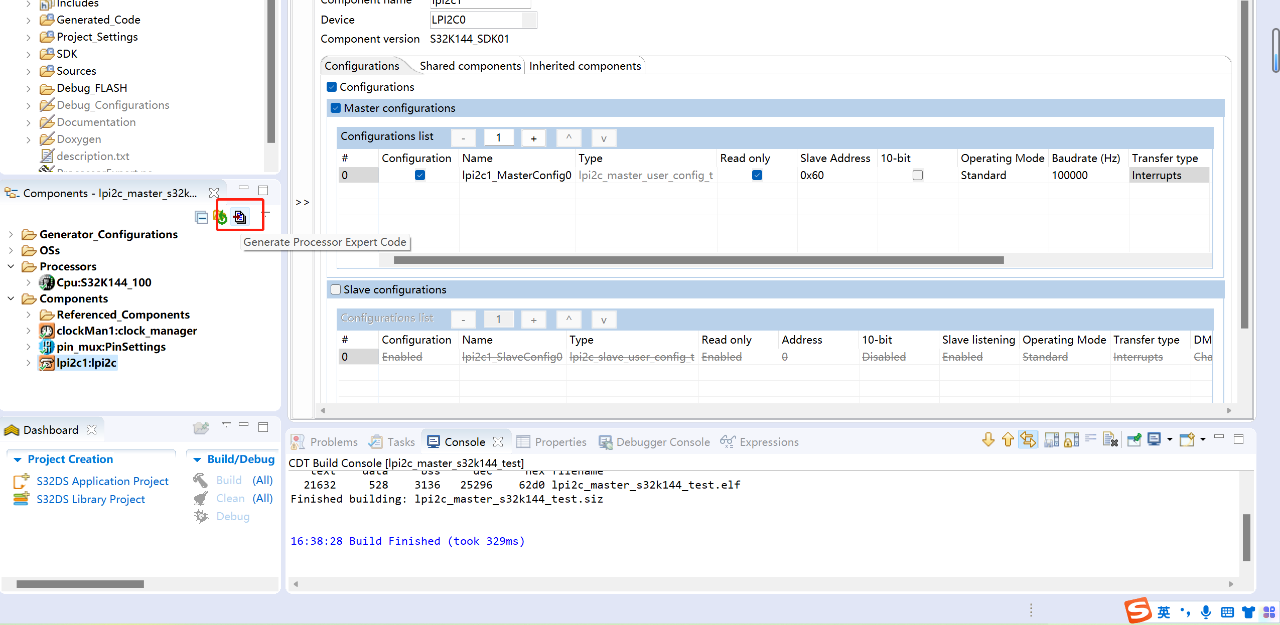

- 设置完成后点击左侧红框内生成代码按钮进行代码更新。

- 在引脚复用配置中将 PTA3 配置成 SCL,PTA2 配置成 SDA 随后点更新代码按钮。

- 点击左上角“Build”按钮,编译程序。

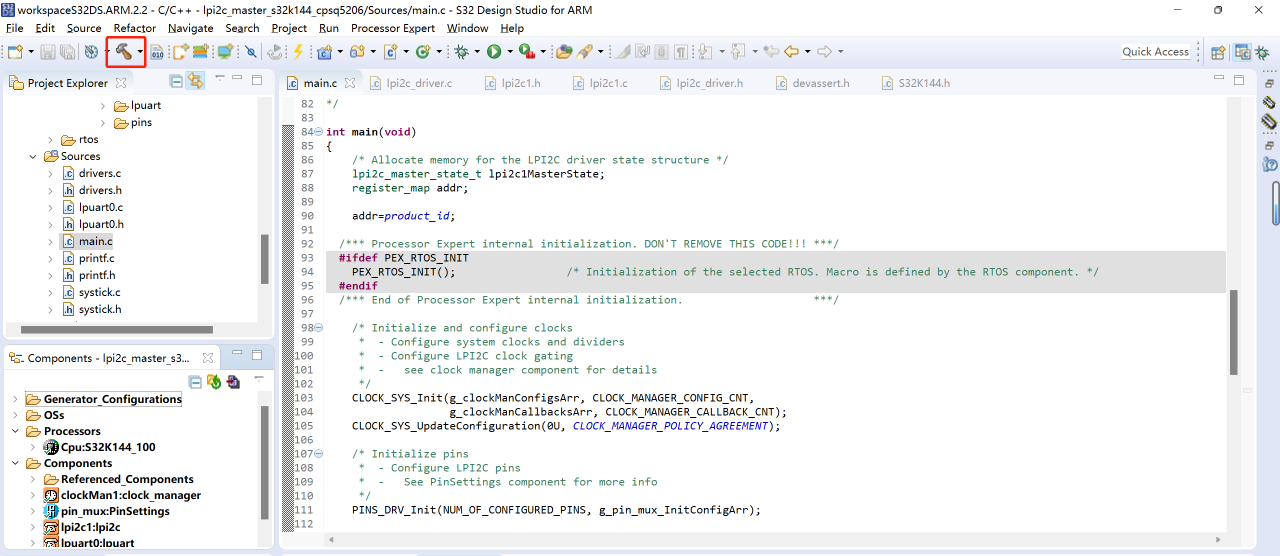

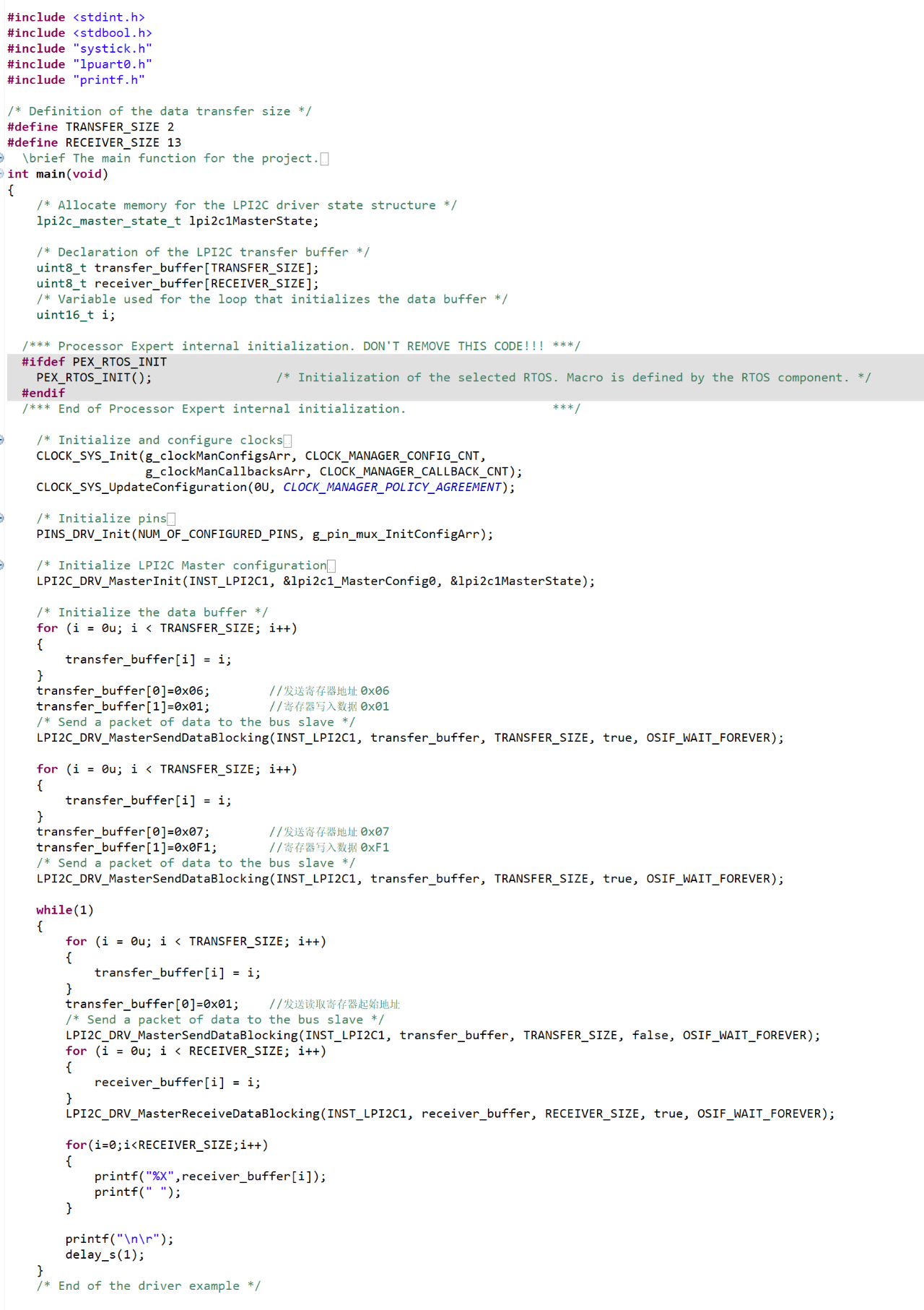

三、代码编写与测试

3.1 代码编写

为了更直观观察 LPI2C 模块的读取结果,还调用了 Systick 与 LPUART 模块来每隔 1 秒通过 LPUART 发送一次 LPI2C 模块的读取结果,Systick、LPUART 模块初始化与 Printf 函数代码编写较长本文不在此赘述。

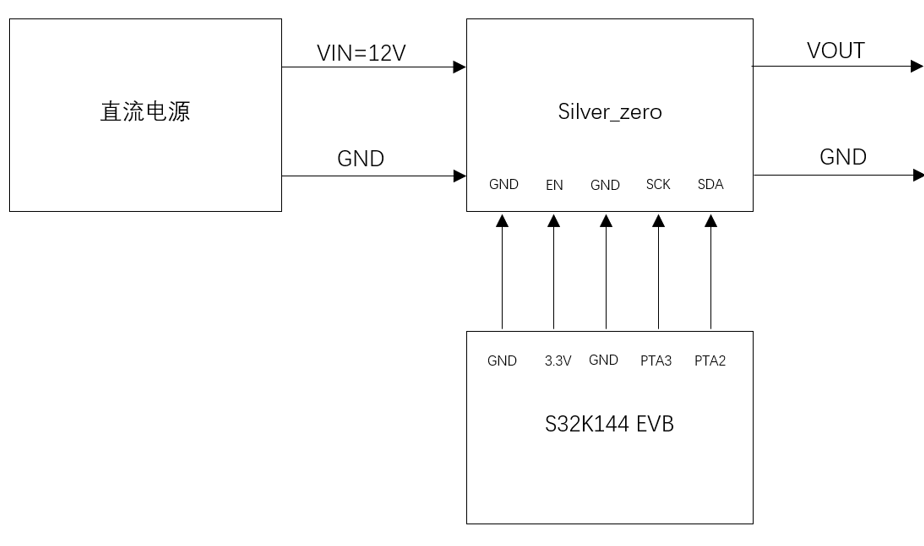

3.2 调试测试

按图将直流电源、Silver_zero 与S32K144 EVB连接。直流电源与 Silver_zero J1 的 VBUS 和 GND 连接为 Silver_zero 提供 12V 直流电,S32K144 EVB 与 Silver_zero J3 连接,各引脚的对应关系如下,Silver_zero 的J2 为 VOUT、GND。使用示波器测量 VIN、SW1(电感左侧)、SW2(电感右侧)与 VOUT 并记录波形,同时记录串口发送 CPSQ5206 当前工作状态。

设备连接图

S32K144 EVB 与 Sliver_zero 引脚对应表

|

Silver_zero |

SDA |

SCL |

GND |

INT |

EN |

GND |

|

S32K144 EVB |

PTA2 |

PTA3 |

GND |

|

3.3V |

GND |

注:INT 引脚 CPSQ5206 分压反馈引脚,使用外部分压反馈时连接,Silver_zero 使用内部分压反馈无需连接。

VIN=12V,L=4.7uH, FSW=400KHZ,CH1:VIN,CH2:OUT,CH3:SW1,CH4:SW2。

串口成功打印 log 与 CPSQ5206 数据手册默认工作状态和写入数据相同,代码成功运行。

四、参考文献

[1] S32K144 Reference Manual.pdf,NXP

[2] S32K1xx Series Cookbook.pdf,NXP

[3] S32K144_IO_Signal_Description_Input_Multiplexing,NXP

[4] PCB - P20-033 Echoes_V2.0_Jadyn Li_20210618, 大大购

[5] CP-D-31-CA01-Rev0.2 CPSQ5206_Datasheet, CPS

欢迎在博文下方留言评论,我们会及时回复您的问题。如有更多需求,欢迎联系大联大世平集团 ATU 部门:atu.sh@wpi-group.com

作者:Hobo Xu / 许宁

评论