一、 前言

客户用芯驰 X9HP 平台做的智能座舱产品,已初步完成 PCB Layout,下面是我们对客户 PCB Layout 评审后的

一些建议。

二、 SEMIDRIVE X9HP PCB Layout 评审要点

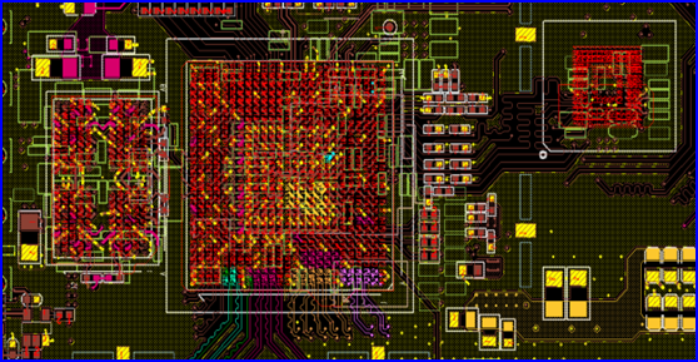

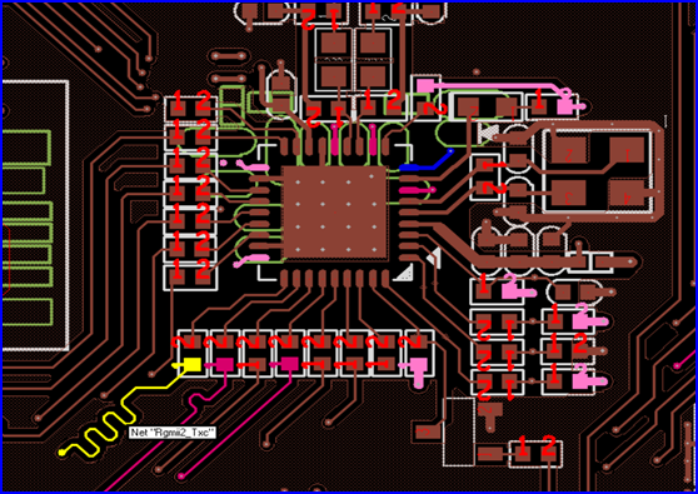

① 如图,SoC、DDR、eMMC 这些区域下面的信号层不要铺地,GND 层除外,建议这部分参考原厂的 PCB 设计。

▲ 图 1 SoC 部分 GND 铺铜

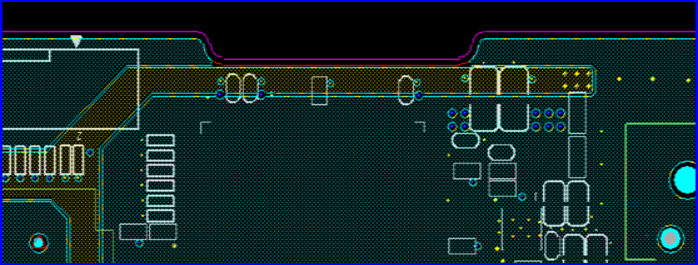

② 如图,底层的走线,建议不要太靠近板边。

▲ 图 2 底层板边走线图

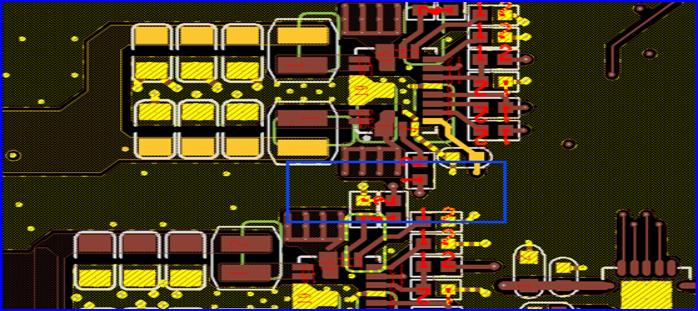

③ 如图,电源部分 GND 断开了,建议连接上。

▲ 图 3 GND 不完整

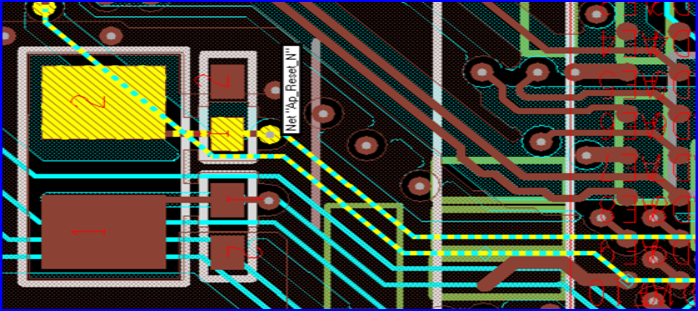

④ 如图,晶体 X2 的时钟走线离系统复位信号 AP_RESET_N 太近,建议优化。

▲ 图 4 AP_RESET_N 走线

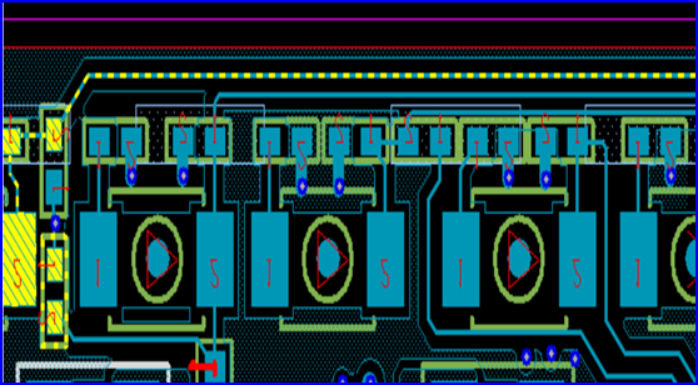

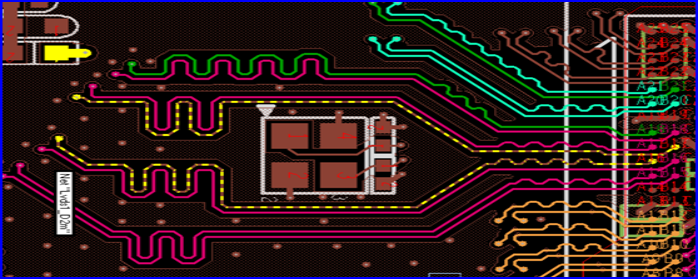

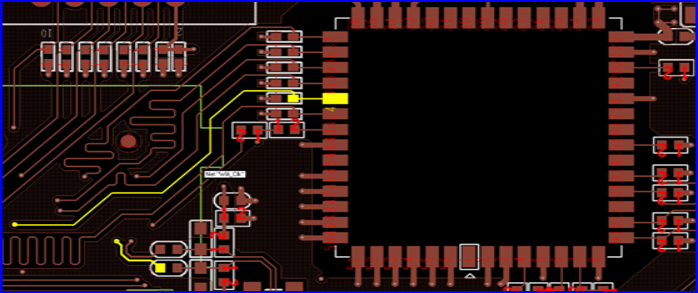

⑤ 如图,eMMC 时钟信号 EMMC1_M1_CLK 走线,建议包地。

▲ 图 5 EMMC1_M1_CLK 走线

⑥ 如图,LVDS 信号走线,建议不要太靠近晶体 X1,LVDS 走线阻抗要求 100 Ω。

▲ 图 6 LVDS 走线

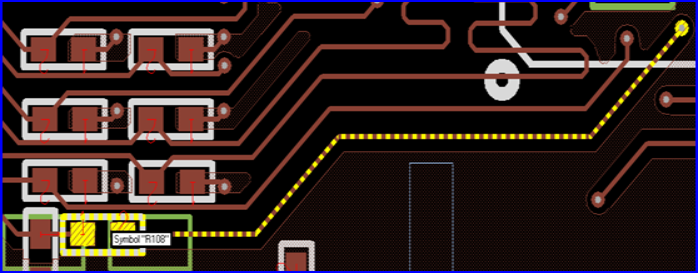

⑦ 如图,Ethernet 部分的走线,时钟信号走线 TXC、RXC 建议包地,TXD 信号上的电阻,建议靠近 SoC 摆放,RXD 信号上的电阻,建议靠近 PHY 芯片摆放。

▲ 图 7 Ethernet 部分走线

⑧ 如图,第 5 层边上的电源 VDD_3V3,建议不要太靠近板边,板边要有完整的 GND。

▲ 图 8 电源 VDD_3V3 走线

⑨ 如图,Wi-Fi 部分时钟信号 WIFI_CLK 走线,建议包地。

▲ 图 9 WIFI_CLK 走线

以上便是芯驰 SEMIDRIVE X9HP PCB Layout 评审要点

接下来我们也会不断更新更多关于 SEMIDRIVE X9、G9 系列的开发博文,同时我们也会持续推出更多 ADAS相关的技术开发博文。如需更深入的技术交流,欢迎在博文下方评论或者关注并给我留言。

附录:参考文献

①《 SemiDrive_9 系列硬件设计手册_Rev01.04 》

②《 SD007_MS_TI_B01_PCB_20220705 》

评论