DC-DC同步降压电路设计是一种非常受欢迎与常见的降压电路设计,而在DC-DC降压电路设计中,目前业界可以分为传统式分离式降压设计与整合式降压设计,本文主要为探讨与比较DC-DC降压电路中传统式的分离式降压电路设计与整合式降压的电路设计之间优缺:

- 整合式降压电路与分离式降压电路设计的优缺点:

2.Layout布局上的差异:

- 整合式设计降压: 将Controller与H/L Mos皆设计进同一个包装元件之中,因此设计上所占用PCB面积较传统分离式降压电路设计上的PCB面积少许多。

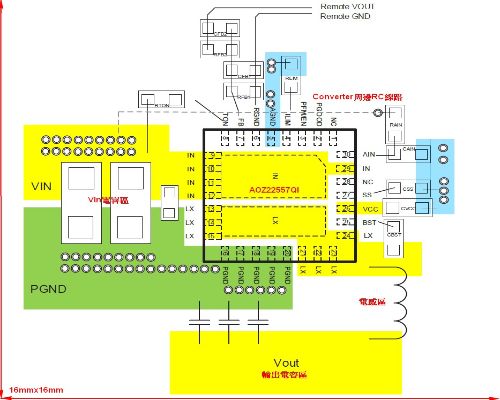

以AOS所推出AOZ22557QI为设计范例,其整合式降压本体包装为4mm×4mm QFN-30L package,包含周边元件的设计,可实现于16mmx16mm PCB 面积内将一完整降压电路设计与布局完成:

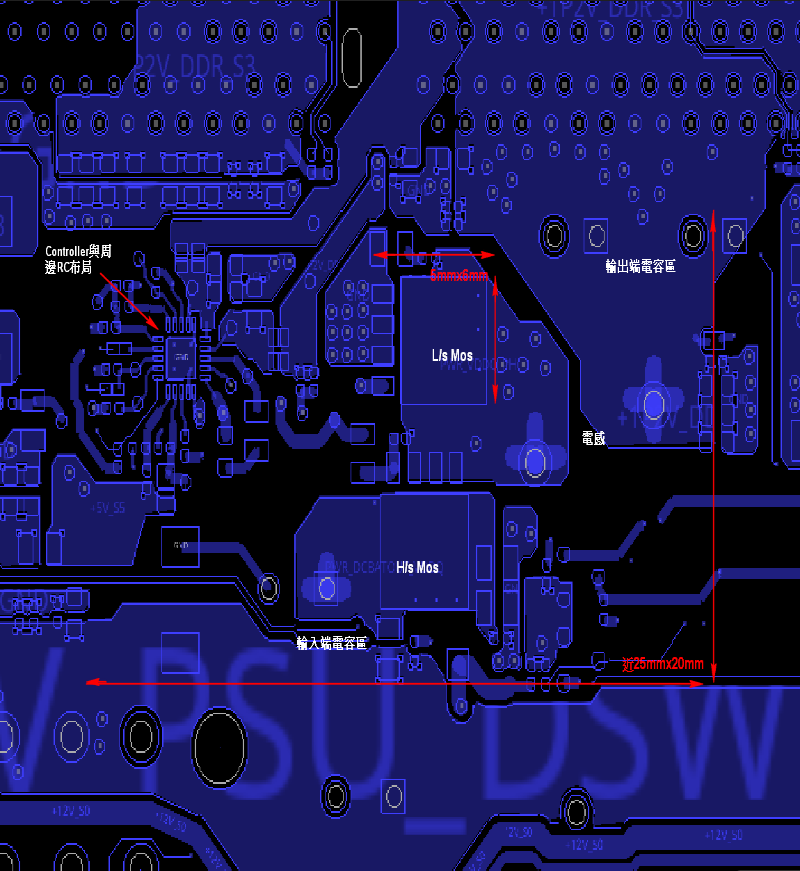

- 分离式设计降压电路设计的布局来看,就算选用目前最小包装的单体Mos 也要3mmx3mm 两颗再外加上Controller与其周边线路以及降压电路所需电感元件等等,也极难满足在极小的空间中完成电路的设计与PCB布局.所需空间25mm*20mm.

分离式设计降压电路 (以常见QFN5x6 package)范例:

结论:

从上比较来看可以很明显的观察出, 整合式设计降压在电路设计与PCB布局中具有相当大的优势,可使电路设计在极小的空间中完成设计,现如今许多电子产品皆追求着轻薄短小,不论是桌上型电脑,笔记型电脑,显示卡,平板,手机等设计都是如此,在此之中整合式降压的设计优势不难看出为何可以成为占据现行设计中达到接近75%份额的香饽饽!

附上AOS COT AOZ22557QI简介,欢迎各位有需要的至AOS官网搜寻整合式降压产品或寻找诠鼎的AOS PM,谢谢。

Q&A:

Q1: AOZ22557QI 内部包装的H/L Mos Rds(on)为多少?

Ans: H-S Mos:11mΩ / L-S Mos:4mΩ.

Q2: AOZ22557QI最高操作频率?

Ans: 1MHz工作频率.(Based on application and temperature)

Q3: AOZ22557QI内部Minimum Off Time为多少?

Ans: 规格为Minimum Off Time为350ns.

Q4: AOZ22557QI的静态电流Quiescent Supply Current为多少?

Ans: 规格为Quiescent Supply Current为400uA.

Q5: AOZ22557QI的应用领域适用哪些部分?

Ans: 数位视讯转换盒与LCD TV以及服务器等Point-of-load DC/DC converters皆适用.