1. 概述

(1)Boot Package 格式

① BPT(Boot Package Table)

| 启动设备 | Normal Boot Package 存储地址 | Backup Boot Package 存储地址 | Third Try Boot Package 存储地址 |

| NOR/Hyper Fla sh | 由SFS指定 | 由SFS指定 | 由SFS指定 |

| eMMC | BOOT1分区 offset=0 | BOOT2分区 offset=0 | User Areas分区 offset=20kB |

| SD card | offset=20kB | - | - |

| USB/UART | 无存储 | - | - |

(2)安全启动

上电后固化在芯片中的 ROM 程序会根据 boot pin 的设置从 XSPI/eMMC/SD/UART/USB 等介质中获取下级启动镜像。启动镜像的格式必须满足前述 Boot Package 格式。

ROM 程序验证 BPT 以及每个 core 镜像的流程如下:

①. 计算 BPT 中公钥的 hash(SHA256)并与 ROTPK1 中保存的 hash 对比,如果两者不一致,则启动失败

②. 使用 BPT 中的公钥验证 BPT 中的签名,如果签名验证失败,则启动失败

③. 计算每个 core 镜像 hash,与保存在 BPT 中的 hash 对比,如果不一致则启动失败

④. 上述都成功,则启动 BPT 中所指定的core镜像

(3)BootROM 控制⽅式:

使⽤ Semidrive 提供的⼯具(atb_signer)对 image 进⾏签名时,设置 Debug 控制字并填写芯⽚ DeviceID(DID)。当 BootROM 启动成功时,依据控制字打开 Debug。

(4)Flsah layout

上图为 HyperFlash 和 NorFlash 的典型的 Flash storage layout,其中 HyperFlash 的 sector size(sector 指 Flash 最小擦除单位)为 256kByte(典型值),NorFlash 的 sector size 为 4kByte(典型值)。为使擦写方便,对 flash 空间时做如下分配:

- 将 SFS 存放在第 1 个 Sector 的起始地址 0x0 至 0x7F 中占用 128Byte;

- 将 RFD 存储在第 1 个 Sector,其具体的起始地址为 0xF0-0x1FF,占用 272个Byte,RFD 是用于加密启动的信息,可以查看芯驰的资料或者后续博文;

- 将第 2 个 Sector 预留为 XSPI training 数据区域;

- 以第 3 个 sector 为起始,存放 Primary GPT 分区表预留区域(非必须,仅预留,提示GPT 分区表并非必须,如果不使用分区表,该区域可以不预留。),GPT 分区表 Primary 部分占用 17KB 空间,在 HyperFlash 上占用 1 个 sector,在 NorFlash 上占用 5 个 sector 存储。此外,根据 GPT 分区表的格式,也需要在 Flash 尾部需预留空间 17KB 存储 Secondary 分区表。

- Normal Boot Package、Backup Boot Package、Third Try Boot Package 由 SFS (打包可以指定用户程序地址)中的地址指定,如果按照上图中预留分区表的 Layout 则中 3 个 Boot Package 的存储地址为:

| HyperFlash存储地址 | NorFlash存储地址 | NorFlash |

| Normal Boot Package | 0xC0000(SFS指定) | 0x7000(SFS指定) |

| Backup Boot Package | 0x4C0000(SFS指定) | 0x407000(SFS指定) |

| Third Try Boot Package | 0x8C0000(SFS指定) | 0x807000(SFS指定) |

2. 环境准备

• Lauterbach Trace32 调试器 for arm

• E3 参考板(其上的 E3 芯⽚位于开发模式)。

• 芯驰 SDToolBox,各个⼯具的使⽤⼿册集成在⼯具包中,双击⼯具包中的 Help 图标可以查看相关应⽤的使⽤说明,fuse 相关操作在⼿册第七章:SDFuseTool 使⽤说明。

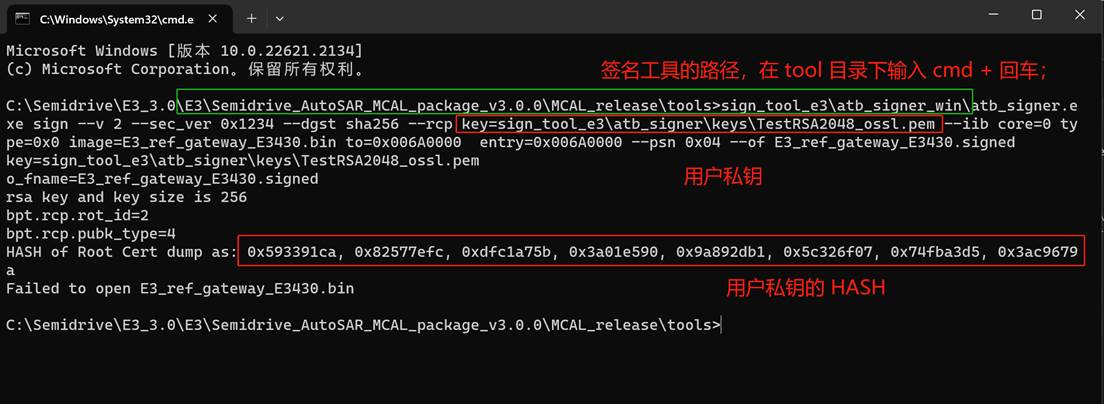

• atb_signer:safety/securityimage 签名⼯具。

key=sign_tool_e3\atb_signer\keys\TestRSA2048_ossl.pem

• ⼀个⽤⼾私钥(例如⼀个 rsa2048 的私钥,可使⽤ Openssl ⽣成)。

• ⼀个 8 字节的数做为芯⽚的 UID : 0x12345678abcdef88 (芯⽚出⼚应该已经烧写完成,这里这是举个例子)

3. 安全启动

; ------------------------------------------------------------------------------

; @Title: Example for manual JTAG access, Debugger in DOWN Mode

; @Description:

;This script reads out the IDCODE of an ARM7 core when the debugger is in

;DOWN mode.

;Detailed knowledge about JTAG is required to use manual JTAG control signals!

;Tested on an ARM7 target board.

; @Keywords: idcode

; @Author: PEG

; @Props: Template

; @Copyright: (C) 1989-2014 Lauterbach GmbH, licensed for use with TRACE32(R) on

; ------------------------------------------------------------------------------

; $Id: example1.cmm 6982 2023-02-22 11:10:17Z kjmal $

; @Copyright: Semidrive semiconductor

; @Title: Semidrive Secure Debug (Challenge & Response) logic.

; The debugger is in DOWN mode, the JTAG driver is tristated.

area

SYStem.CPU CortexR5

SYStem.CONFIG.apbaccessport 0

SYStem.CONFIG.apbap1.base 0x2000

SYStem.CONFIG.debugaccessport 0

SYStem.CONFIG.debugap1.base 0x2000

SYStem.CONFIG.COREDEBUG.Base 0xF2081000

;taishan

;SYStem.CONFIG.COREDEBUG.Base 0xF0a01000

;taishanl

;SYStem.CONFIG.COREDEBUG.Base 0xF0a01000

;taishanll

SYStem.Option.TRST OFF

SYStem.JtagClock 1MHz

JTAG.PIN ENable

; enable JTAG output driver

JTAG.SHIFTTMS 1 1 1 1 1

; soft reset of the JTAG interface, goto Test-Logic Reset state

JTAG.SHIFTTMS 0 1 1 0 0

; goto Shift-IR state

JTAG.SHIFTREG 1 1 1 1

; shift in UID instruction

JTAG.SHIFTTMS 1 1 0 0

; goto Shift-DR state

JTAG.SHIFTREG %long 0x0 0x0

; shift in 64bit dummy code. shift out our uid

PRINT JTAG.SHIFT()

; print the UID

JTAG.SHIFTTMS 1 1 0 0

; goto Shift-DR state

JTAG.SHIFTREG %long 0x74657374 0x6b657930

; shift in the corresponding key .shift out our uid

PRINT JTAG.SHIFT()

JTAG.SHIFTTMS 1 1 1 1 1

; goto Test-Logic Reset state

JTAG.SHIFTTMS 0 1 0 0

; goto Shift-DR state

JTAG.SHIFTREG %long 0x0

; shift our IDCODE

PRINT JTAG.SHIFT()

JTAG.PIN Disable

; Disable JTAG output driver

SYStem.Mode Attach

;attach

ENDDO

6. 后续博文系列

(1)【Semidriver E3】efuse 数据生成

(2)【Semidriver E3】efuse 数据烧写

等等

评论